pll鎖定時間按照頻率精度多少來計算

PLL鎖定時間是指當PLL嘗試將輸出頻率與輸入頻率相匹配時所需的時間。這個時間可以用來衡量PLL的性能,因為它決定了PLL能否快速、準確地鎖定頻率,并且影響PLL的應用領域。PLL鎖定時間可以根據(jù)PLL的頻率精度來計算,下面是一個詳細的討論。

PLL - 綜述

PLL是一種電路,它在輸入信號和輸出信號之間建立了一個相位鎖定環(huán),以使輸出頻率與輸入頻率之間存在固定的關系。舉例來說,如果PLL的輸入頻率為f_in,而輸出頻率為f_out,則它們之間的比例為f_out/f_in。PLL的設計目的是在輸出信號中保持與輸入信號相同的相對相位關系。

PLL通常用于數(shù)字通信的網(wǎng)絡中,以確保數(shù)據(jù)傳輸?shù)臏蚀_和可靠性。這是因為它可以平滑地調(diào)整周期性信號的相位和頻率,以便與同步數(shù)據(jù)傳輸協(xié)議匹配。

PLL鎖定時間 - 定義

PLL鎖定時間是指PLL從應用外加的輸入信號后,達到穩(wěn)定輸出頻率所需的時間。PLL鎖定時間是一個關鍵參數(shù),因為它決定了PLL能夠快速、準確地調(diào)整輸出信號。如果PLL的鎖定時間太長,將導致系統(tǒng)延遲和穩(wěn)定性差,影響PLL的性能。

PLL鎖定時間 - 計算

PLL鎖定時間可以通過下式計算得出:

t_lock = (2π/Δf_rms) * ln(1/ε)

其中,Δf_rms是指取樣時間段內(nèi)參考時鐘的頻率抖動標準差(也稱為參考時鐘的穩(wěn)定度);ε是指設定的固定值,用于表示PLL輸出頻率與參考時鐘頻率之間的偏差。例如,如果設置ε=0.01,則PLL輸出頻率與參考時鐘最多相差1%。Π是圓周率,ln表示自然對數(shù)。

這個公式由兩個部分組成:一個反映抖動穩(wěn)定度的部分,一個反映PLL響應的部分。抖動穩(wěn)定度是參考時鐘的波動,它會影響PLL的鎖定時間。PLL響應則指PLL反應能力的快慢,它會影響PLL鎖定時間。PLL響應越快,鎖定時間就越短。

在計算PLL鎖定時間時,還要考慮PLL的輸出頻率范圍和精度。例如,如果要實現(xiàn)PLL輸出頻率在1GHz到2GHz之間,那么Δf_rms的值應該取1GHz到2GHz范圍內(nèi)參考時鐘的抖動標準差。

PLL鎖定時間 - 影響因素

PLL鎖定時間受許多因素的影響,包括抖動穩(wěn)定性、PLL類型、芯片技術、電路設計等。

在很多情況下,PLL的鎖定時間是影響PLL的整體性能的最重要參數(shù)之一。PLL的鎖定時間從理論上可以通過上面的公式來計算,但實際的參數(shù)可能會與理論值略有不同,因為每個PLL都有自己獨特的抖動和響應特性。

PLL鎖定時間 - 案例研究

對于某些應用來說,PLL的鎖定時間是一個關鍵因素。在具體的設計中,需要考慮PLL鎖定時間的大小,以確保系統(tǒng)的穩(wěn)定性和可靠性。

例如,在字節(jié)緩存器中,PLL的性能對數(shù)據(jù)捕獲非常關鍵。實驗表明,如果PLL與參考時鐘的差異達到1%或更高,PLL就可能無法在規(guī)定的時間內(nèi)完成鎖定。針對這個問題,可以優(yōu)化PLL的抖動穩(wěn)定度和響應速度,來確保其能夠以最短的時間內(nèi)完成鎖定。

在數(shù)字時鐘生成電路中,鎖定時間也是非常關鍵的參數(shù)。數(shù)字時鐘生成電路中的PLL通常需要產(chǎn)生多種頻率和時鐘源,以滿足不同的應用需求。在這種情況下,鎖定時間對于確保時鐘源的同步性和穩(wěn)定性也非常重要。

PLL鎖定時間在很多電路設計中都是必不可少的性能參數(shù)之一。為了確保PLL能夠快速、準確地調(diào)整輸出頻率,電路設計人員必須仔細評估PLL的抖動穩(wěn)定度和響應速度,以確定理想的鎖定時間和參數(shù)。通過優(yōu)化PLL的性能和參數(shù),設計人員可以確保電路的穩(wěn)定性和可靠性,來滿足不同的應用需求。

-

pll

+關注

關注

6文章

880瀏覽量

136004 -

緩存器

+關注

關注

0文章

63瀏覽量

11823 -

時鐘源

+關注

關注

0文章

96瀏覽量

16223

發(fā)布評論請先 登錄

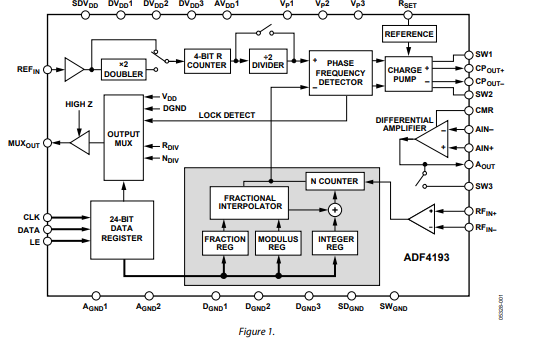

ADF4193低相位噪聲、快速建立PLL頻率合成器技術手冊

ADF4151小數(shù)N/整數(shù)N分頻PLL頻率合成器技術手冊

為何DAC5686高頻率輸入PLL不能鎖定?

AN-1390:手動選擇頻段以縮短PLL鎖定時間

評論