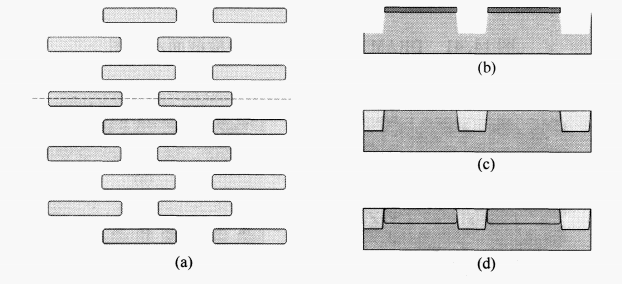

在下面的圖中較為詳細(xì)的顯示了堆疊式DRAM單元STI和阱區(qū)形成工藝。下圖(a)為AA層版圖,虛線表示橫截面位置。下圖(b)為AA刻蝕后的橫截面;下圖(c)為形成STI后的橫截面;下圖(d)顯示了P阱形成后的橫截面。STI和P阱形成過程由于相對較為獨(dú)立,所以可以同時在外圍區(qū)域進(jìn)行。此處P阱形成通過一個P阱光刻版。外圍區(qū)域有更精細(xì)的圖形,單元區(qū)域?yàn)榭瞻住阱只在外圍區(qū)域,而不在單元區(qū)域,這是因?yàn)镈RAM單元只有NMOS。

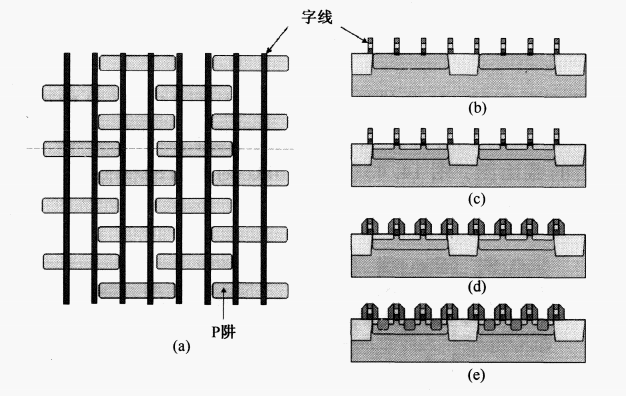

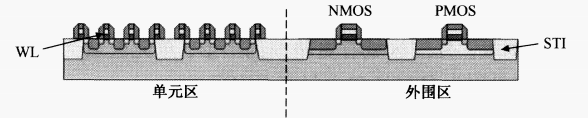

下圖詳細(xì)顯示了堆疊式DRAMSTI和阱區(qū)形成過程。下圖(a)所示為與AA層重疊的WL層布局圖,虛線表示橫截面的位置。下圖(b)顯示了DRAM單元NMOS柵的橫截面,這就是字線(WL)。下圖(c)所示為輕摻雜漏(LDD)形成工藝;下圖(d)為側(cè)壁間隔層形成工藝;下圖(e)為源/漏極形成工藝。兩個版圖沒有顯示在下圖中,分別為外圍區(qū)域的PMOSLDD和PMOSSD(見下圖的右側(cè))。鉆硅化物用于外圍區(qū)域以減小接觸電阻。

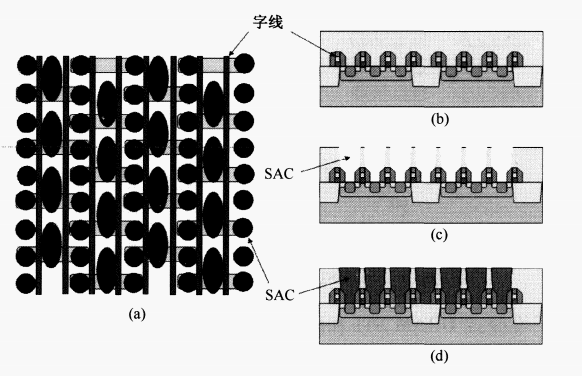

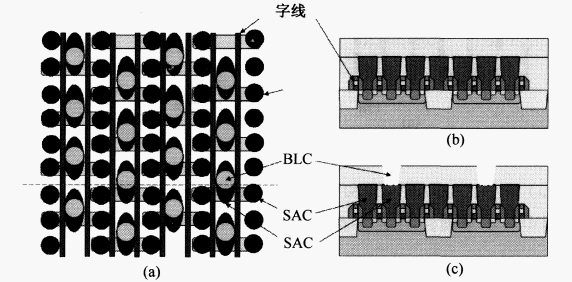

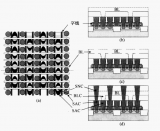

下圖(a)顯示了第一層接觸,即所謂的堆疊式DRAM自對準(zhǔn)接觸(SAC)。有些人也稱這種模式為刻蝕后焊盤接觸(LPC),或多晶硅CMP后的多晶硅焊盤(LPP)。因?yàn)閮?nèi)部接觸孔和短的WL是致命缺陷,通過ILD0刻蝕接觸孔非常具有挑戰(zhàn)性,通常在密集的字線之間使用硅酸鹽玻璃(BPSG)達(dá)到NMOS的源/漏極。因此,需要發(fā)展自對準(zhǔn)接觸工藝。通過在字線的頂部保留氮化物硬掩膜并在兩邊形成側(cè)壁氮化物,WL被氮化物包圍。當(dāng)SAC刻蝕工BPSG和氮化物之間具有足夠高的刻蝕選擇性時,刻蝕過程成為自對準(zhǔn)過程,這樣可以使得接觸孔通過密集的WL達(dá)到硅表面而無短路。

多晶硅沉積填充SAC孔之前,通常使用高劑量N型接觸離子注入用于減小接觸電阻。電子束檢查通常用于捕獲刻蝕和多晶硅CMP后形成的無孔接觸或栓塞WL接觸缺陷。SAC工藝在陣列區(qū)域。

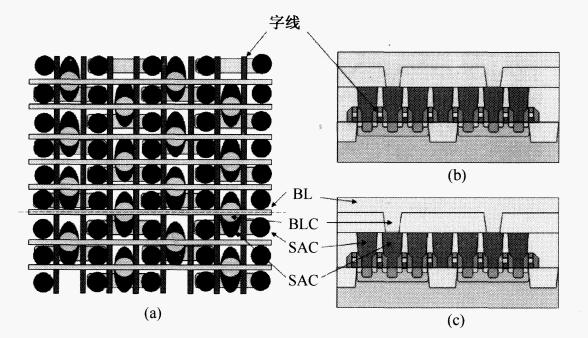

在下圖中顯示了堆疊式DRAM位線接觸(BLC)。從下圖(a)中可以看出位線接觸在SAC栓塞上連接到AA層的中間部分。每個BLC連接兩個DRAM單元。下圖(b)顯示了ILD1沉積和CMP后的截面圖,下圖(c)中BLC刻蝕后的橫截面。對于堆疊式DRAM,ILD1通常是BPSG。

外圍區(qū)域的位線接觸可以通過陣列區(qū)域的BLC圖形化,由于陣列和外圍區(qū)域的BLC在尺寸和深度方面差別很大,因此工藝工程師一般將這兩種接觸工藝過程分開。

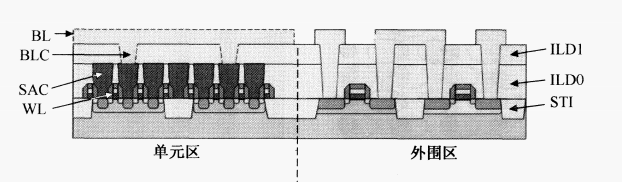

下圖(a)顯示了堆疊式DRAM的位線(BL)結(jié)構(gòu)。可以看出,位線通過和位于SAC栓塞上的BLC與AA層中間部分連接。鴇(W)是最常用于形成BL的金屬。Ti/TiN阻擋層/黏合層沉積后,W使用CVDX藝沉積填充BLC孔并在晶圓表面形成薄膜。BL光刻版定義出陣列和外圍區(qū)域的BL金屬線,并通過金屬刻蝕過程形成BL圖形。下圖顯示了BL和BLC形成后陣列和外圍區(qū)域的橫截面。為了防止BL短路接觸,通常在BL側(cè)壁上形成空間層。

審核編輯:劉清

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27290瀏覽量

218091 -

DRAM芯片

+關(guān)注

關(guān)注

1文章

84瀏覽量

18011 -

CMP

+關(guān)注

關(guān)注

6文章

150瀏覽量

25983 -

接觸電阻

+關(guān)注

關(guān)注

1文章

106瀏覽量

11919 -

NMOS管

+關(guān)注

關(guān)注

2文章

121瀏覽量

5407

原文標(biāo)題:半導(dǎo)體行業(yè)(二百零二)之ICT技術(shù)(十二)

文章出處:【微信號:FindRF,微信公眾號:FindRF】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

13um應(yīng)變補(bǔ)償多量子阱SLD臺面制作工藝的研究

三星宣布:DRAM工藝可達(dá)10nm

DRAM芯片中的記憶單元分析

配備DRAM的三層堆疊式CMOS影像傳感器介紹

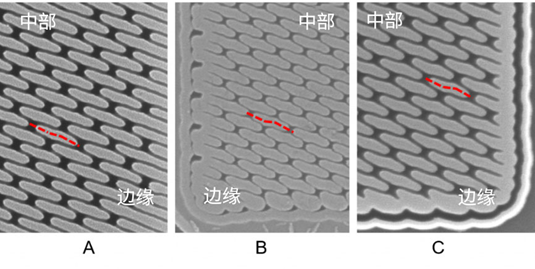

對先進(jìn)DRAM工藝中有源區(qū)形狀扭曲的研究

模塊工藝——雙阱工藝(Twin-well or Dual-Well)

CMOS集成電路的雙阱工藝簡析

動態(tài)隨機(jī)存儲器集成工藝(DRAM)詳解

堆疊式DRAM存儲節(jié)點(diǎn)相關(guān)部分的結(jié)構(gòu)分析

堆疊式DRAM單元STI和阱區(qū)形成工藝介紹

堆疊式DRAM單元STI和阱區(qū)形成工藝介紹

評論