本文介紹一個FPGA開源項目:PCIE通信。該工程圍繞Vivado軟件中提供的PCIE通信IP核XDMA IP建立。Xilinx提供了XDMA的開源驅動程序,可在Windows系統或者Linux系統下使用,因此采用XDMA IP進行PCIE通信是比較簡單直接的。

本文主要介紹一下XDMA IP核的使用和Vivado工程的源代碼結構。

01軟硬件平臺

- 軟件平臺:Vivado 2017.4;

- 硬件平臺:XC7Z035FFG676-2;

02IP核參數配置

2.1 XDMA

XDMA (DMA Subsystem for PCI Express) 是Xilinx提供的可用于PCIE2.0,PCIE3.0的SG模式DMA IP核。該IP核可配置AXI4接口或者AXI4-Stream接口,如果配置成AXI4接口,可方便接入AXI總線互聯,與DDR進行數據傳輸。

另外XDMA還提供可選擇的AXI4-Lite Master和AXI4-Lite Slave接口。其中AXI4-Lite Master接口可用于實現 PCIE BAR 地址到 AXI4-Lite 寄存器地址的映射,可以用于讀寫用戶邏輯寄存器,AXI4-Lite Slave接口用來將 XDMA 內部寄存器開放給用戶邏輯,用戶邏輯可以通過此接口訪問 XDMA 內部寄存器。

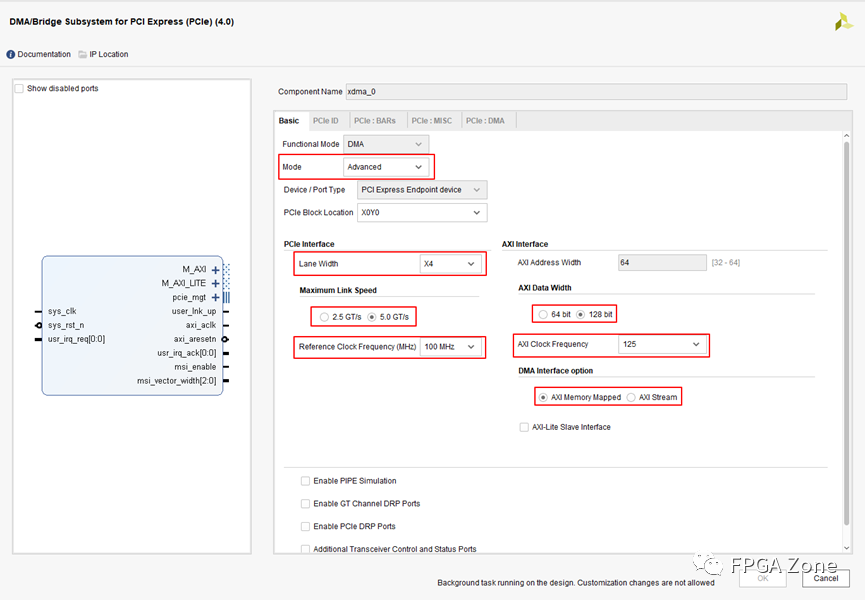

- Mode:選擇Advanced;

- Lane Width:根據FPGA硬件型號選擇;

- Max Link Speed:選擇5.0GT/s;

- Reference Clock:100MHZ;

- DMA Interface Option:選擇AXI4接口;

- AXI Data Width:AXI4總線位寬選擇128bits;

- AXI Clock:125MHZ;

PCIE ID配置保持默認選項。

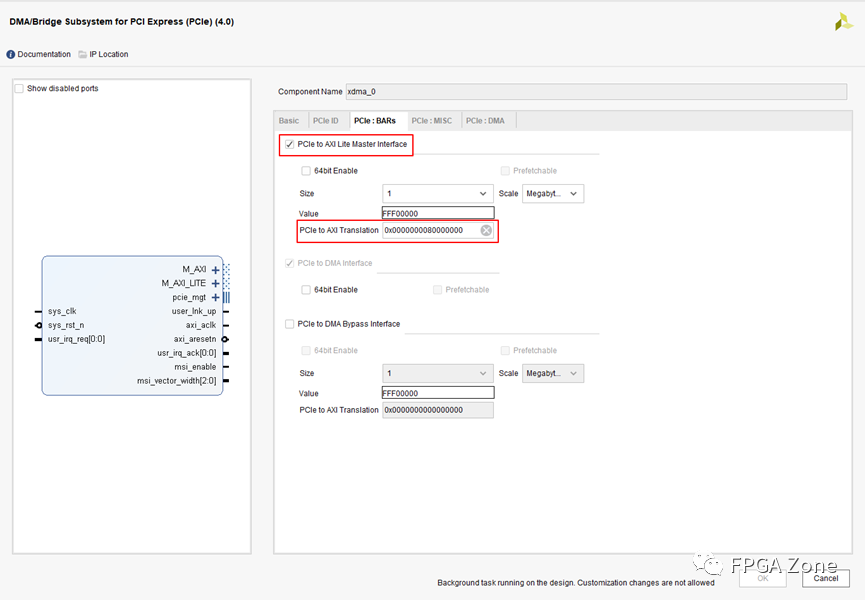

- 選擇PCIE to AXI Lite Master Interface;

- 空間大小根據實際需要進行選擇;

- PCIE to AXI Translation:BAR地址到AXI地址轉換,這里設置為0x8000_0000;

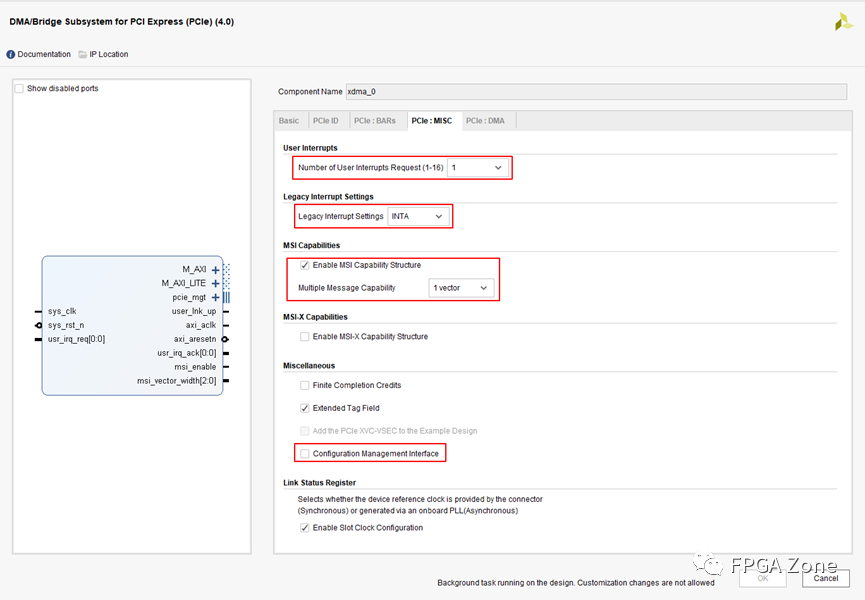

- User Interrupts:用戶中斷配置,根據實際需求選擇;

- Legacy Interrupt:XDMA支持Legacy中斷;

- 使能MSI中斷;

- Configuration Management Interface不選;

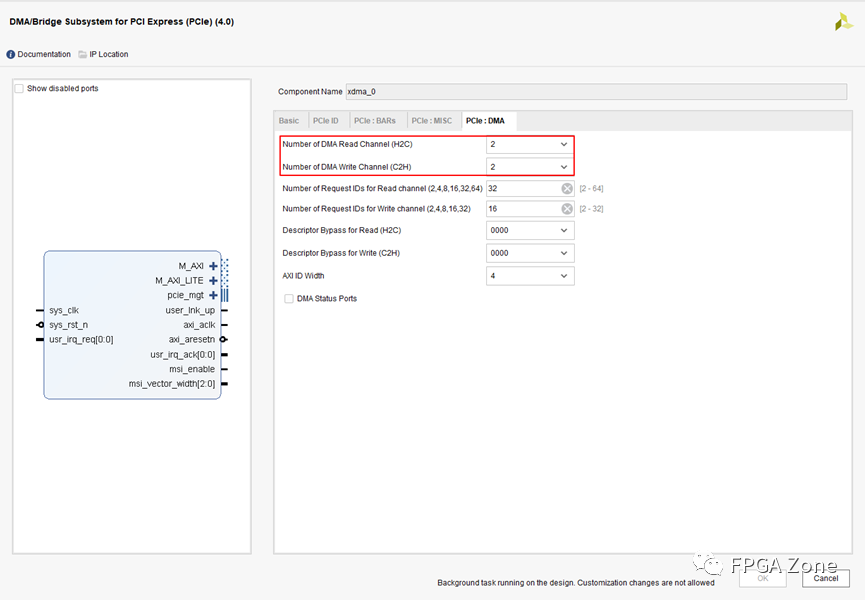

- Number of DMA Read Channel (H2C) 和Number of DMA Write Channel (C2H) :這里選擇2,即XDMA 可以提供最多兩個獨立的寫通道和兩個獨立的讀通道;

- 其它選項保持默認;

2.2 MIG 7 Series & AXI BRAM Controller

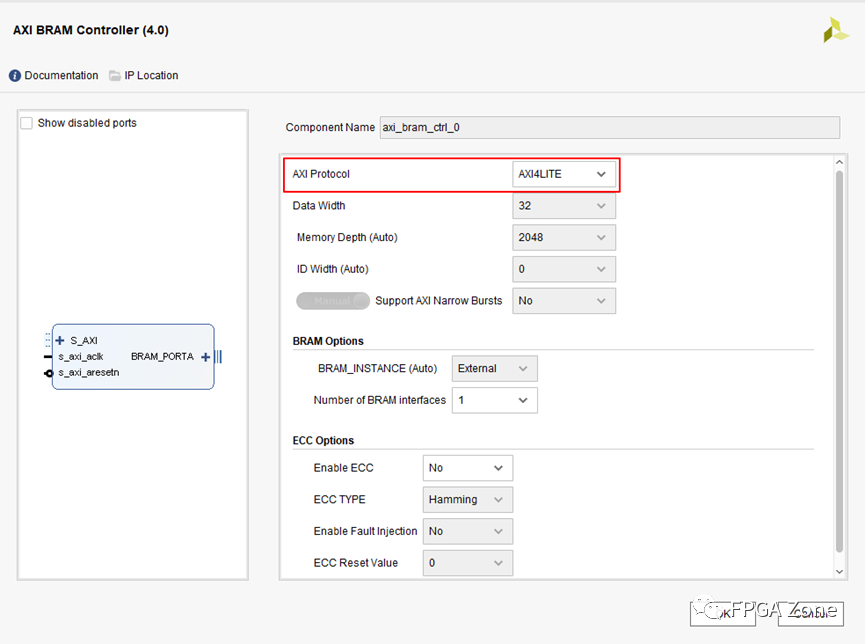

為了測試XDMA IP對AXI4總線以及AXI4-Lite總線讀寫功能,在本工程中添加了BRAM和MIG IP核。其中AXI BRAM Controller IP配置如下,AXI協議選擇AXI4LITE;MIG選擇AXI4接口掛載到AXI4總線,實現對DDR的讀寫。

03工程源碼結構

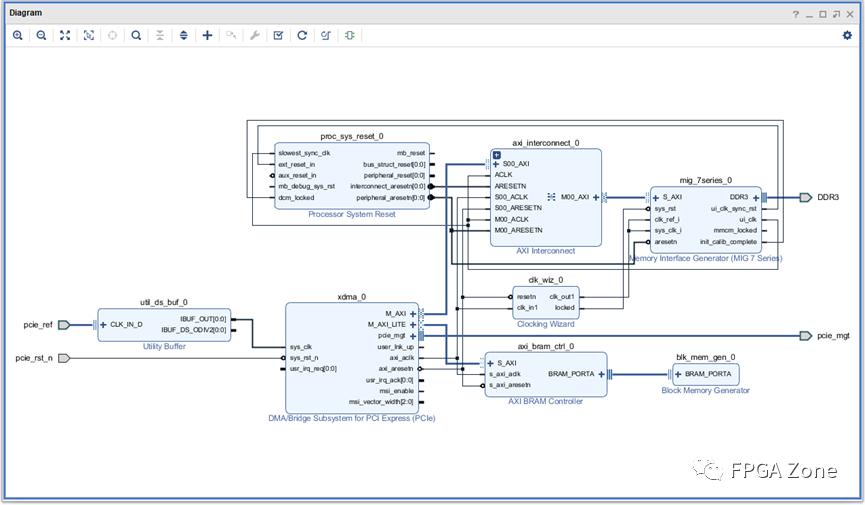

下圖為最終搭建好的系統的Block Design。本工程是基于Zynq平臺建立,但實際只用到PL端資源,因此也可方便移植到其它FPGA平臺使用。

地址配置:DDR地址配置從0開始,BRAM配置從0x8000_0000開始,與XDMA中地址映射保持一致。

04實現功能

該Vivado工程主要用于FPGA PCIE 通信基礎功能測試,具體為:上位機端通過PCIE接口實現對FPGA端BAR地址空間以及DMA內存地址空間讀寫操作。在此工程基礎上,可在FPGA端訪問DDR等模塊緩存的PCIE數據,并進行后續一系列處理。

-

FPGA

+關注

關注

1643文章

21925瀏覽量

612476 -

Linux

+關注

關注

87文章

11427瀏覽量

212422 -

WINDOWS

+關注

關注

4文章

3599瀏覽量

90748 -

通信測試

+關注

關注

0文章

62瀏覽量

49692 -

PCIe

+關注

關注

16文章

1305瀏覽量

84460

發布評論請先 登錄

FPGA的PCIE接口應用需要注意哪些問題

開發FPGA Kintex-7板子的PCIe與DDR模塊高速通信,應該準備些什么?

pc如何通過pcie與FPGA通信

6678 pcie和FPGA接口

基于AM57x平臺的PCIe通信案例(一)

基于AM57x平臺的PCIe通信案例(二)

基于C66x平臺DSP與FPGA通信測試

尋求fpga大牛開發一個簡單的fpga pcie設備

AC701能否通過Artix 7的PCIe鏈路與PC通信?

如何通過PCIe進行FPGA到PC的通信?

2個PCIE PHY在FPGA中連接可能實現嗎?

關于xilinx FPGA pcie測試問題

米爾ARM+FPGA架構開發板PCIE2SCREEN示例分析與測試

評論