臺積電、三星、英特爾等芯片大廠近期積極布局背面供電網絡(BSPDN),像三星計劃將BSPDN技術用于2納米芯片,該公司近日也于日本VLSI研討會上公布BSPDN研究結果。

根據比利時微電子研究中心(imec)的說法,BSPDN目標是減緩邏輯芯片正面在后段制程面臨的壅塞問題,通過設計技術協同優化(DTCO),在標準單元實現更有效率的導線設計,協助縮小邏輯標準單元的尺寸。

BSPDN 可解釋成小芯片設計演變,原本將邏輯電路和存儲器模組整合的現有方案,改成正面具備邏輯運算功能,背面供電或訊號傳遞。

一般而言,通過晶圓正面供電的方法雖能完成任務,但會使功率密度下降、性能受損。

三星稱跟傳統方法相比,BSPDN可將面積減少14.8%,芯片能擁有更多空間,公司可增加更多晶體管,提高整體性能; 線長也減少9.2%,有助降低電阻、使更多電流通過,進而降低功耗,改善功率傳輸狀況。

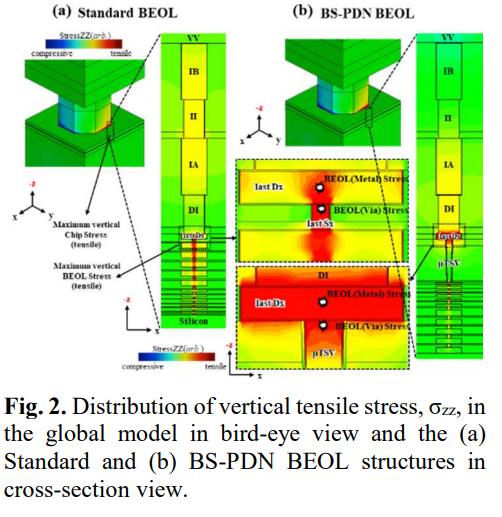

▲ 三星分享 BSPDN 研究成果 (Source:三星)

今年6月,英特爾也舉辦了BSPDN相關的發布會,并將其命名為PowerVia。該公司計劃在英特爾20A制程中采用這方法,使得芯片利用率有望達到90%。

英特爾認為,PowerVia將解決硅架構中的互連瓶頸,透過晶圓背面提電來實現連續傳輸; 該公司預計在2024年推出的 Arrow Lake CPU 中采用這種新方法。

另有消息稱,臺積電如期2025年上線2納米制程,2025年下半年在新竹量產,計劃2026年推出N2P制程,這個制程將采用BSPDN技術。

-

半導體

+關注

關注

334文章

27442瀏覽量

219474 -

存儲器

+關注

關注

38文章

7502瀏覽量

163940 -

納米芯片

+關注

關注

0文章

50瀏覽量

14489

原文標題:半導體“三雄”搶攻下一代技術!

文章出處:【微信號:閃德半導體,微信公眾號:閃德半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

意法半導體下一代汽車微控制器的戰略部署

意法半導體發布新款生物傳感器芯片,賦能下一代智能穿戴醫療設備

下一代半導體技術焦點:光子半導體競爭升級

安世半導體Nexperia將在漢堡投資2億美元研發下一代寬禁帶半導體產品(WBG)

豐田、日產和本田將合作開發下一代汽車的AI和芯片

煜輝半導體獲近億元A輪融資,用于下一代半導體設備研發制造

意法半導體將推出基于新技術的下一代STM32微控制器

全新潛力:金剛石作為下一代半導體的角逐者

納微半導體下一代GaNFast?氮化鎵技術為三星打造超快“加速充電”

三星擴大與Arm合作,優化下一代GAA片上系統IP

DesignCon2024 | 芯和半導體發布針對下一代電子系統的“SI/PI/多物理場分析”EDA解決方案

半導體“三雄”搶攻下一代技術!

半導體“三雄”搶攻下一代技術!

評論