今天給大家分享的是:高速信號、14條高速信號布局設計規則。

在低頻(<50 MHz)下,信號保持在數據特性限制范圍內,并且電路板按預期運行。當速度增加時,阻抗不匹配串擾、反射、振鈴和地彈問題會因更高頻率的影響而出現,這些因素不僅影響系統的數字特性,還會影響系統的模擬特性。由于I/O 和內存接口的數據速率不斷提高,上面說的這些問題很常見。但目前采用高速布局設計規則或者更好的PCB設計來避免嗎這些問題。

一、什么是高速信號?

通常來說,頻率高于50 MHz的信號被認為是高速信號。

理想情況下,時鐘信號是方波,但實際上不可能立馬就將一個“低”電平改為“高”電平,這里有一個特定上升和下降時間,因此在時域中看起來是一個梯形。

但需要注意的是頻域中時鐘信號較高的頻率諧波的幅度取決于其上升和下降時間,如果上升時間較長,則諧波的幅度會變小。

二、高速布局設計規則是什么?

在高速PCB設計時,重點關注布局。下面介紹14個布局設計規則,不僅可以滿足設計要求,還可以降低制造成本。

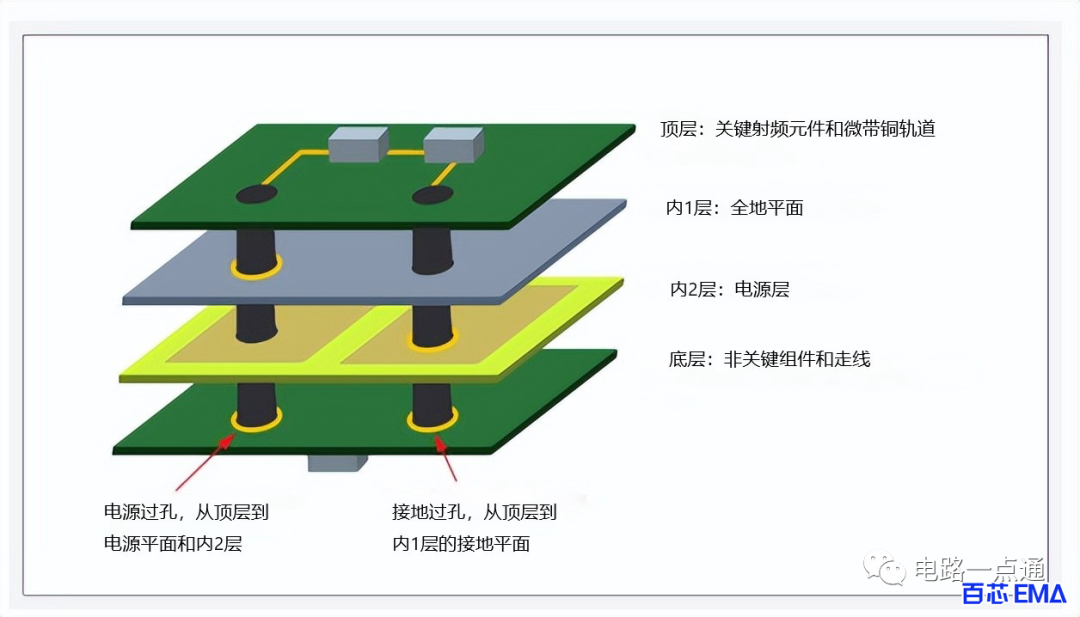

1、在信號走線下方放置一個公共接地層

這樣可以確保電路板中任意2個接地點之間的阻抗最小,不應該通過布線其中的任何走線來破壞地平面。

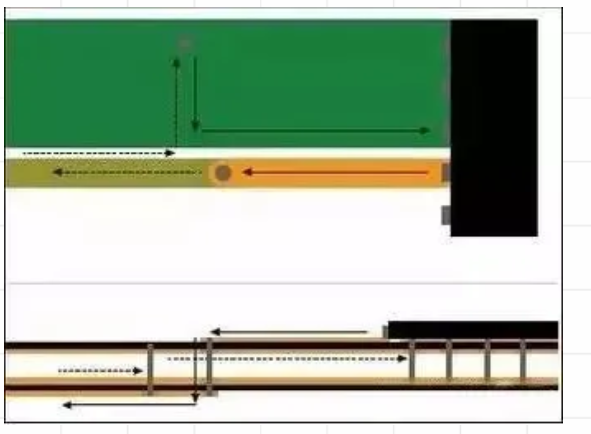

信號走線下方的公共接地層

當需要在同一區域的電路板兩側布線走線時,就無法保證良好的接地層。在這種情況下,唯一的解決方案是在通過大量過孔互連的跡線兩側實現接地平面。

PCB兩側的布線軌道需要更多數量的過孔

2、過孔放置

過孔定位不當會產生平面區域,其中過孔會阻擋電流流動或縮小銅空間,從而導致高電流密度,從而導致電壓降,最好放置形成網格的過孔,在過孔之間留出足夠的空間以包含電源平面。

通過放置發出信號

3、對稱放置過孔以消除阻抗不連續性

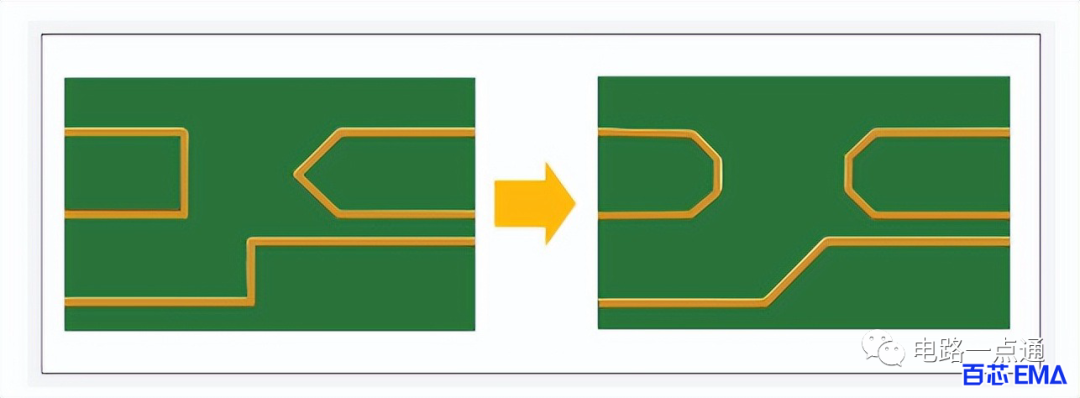

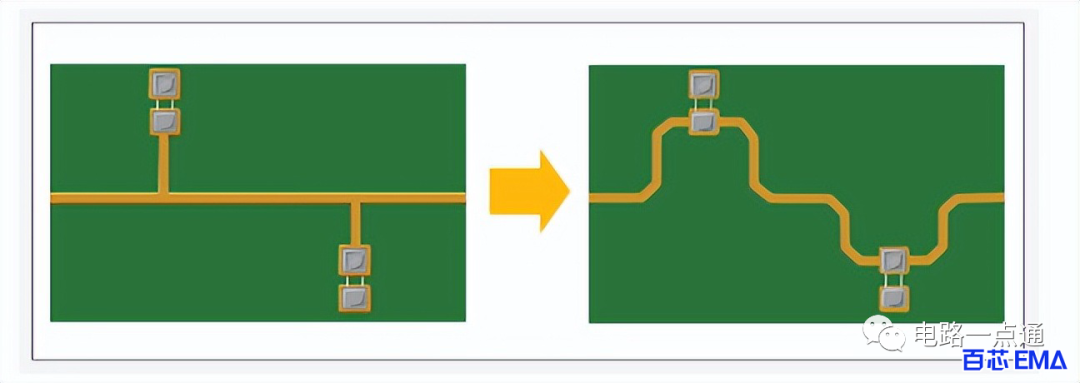

4、布線時保持最小彎曲

如果需要彎曲,則應實施135°彎曲,而不是如圖 (左側)所示的 90°。

布線時選擇最小彎曲

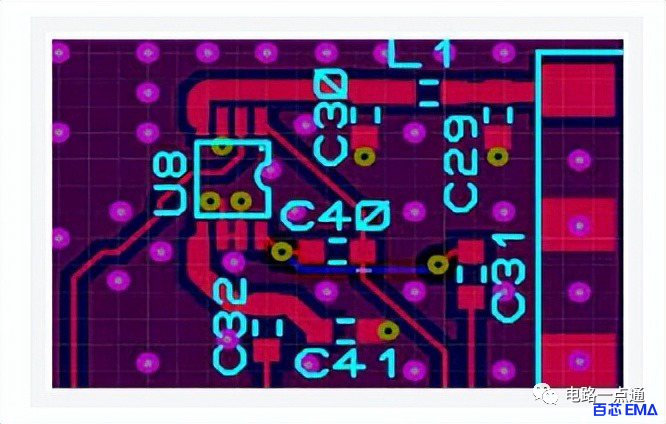

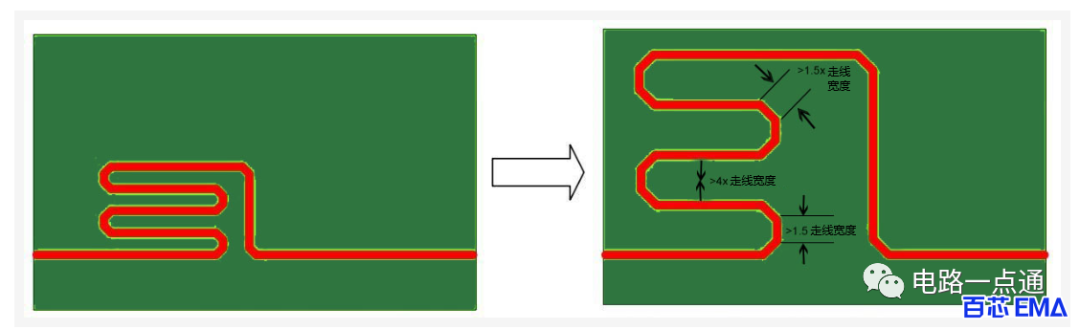

5、添加蛇形走線以實現特定的走線長度

特定長度的蛇形走線

6、在信號走線之間保持至少 3W 的間距

可以最大限度地減少串擾。

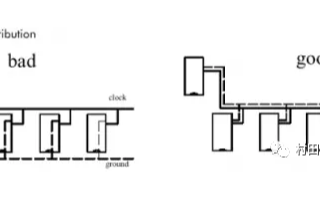

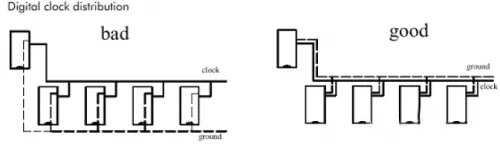

7、實施菊花鏈布線以避免長存根

長存根的菊花鏈布線

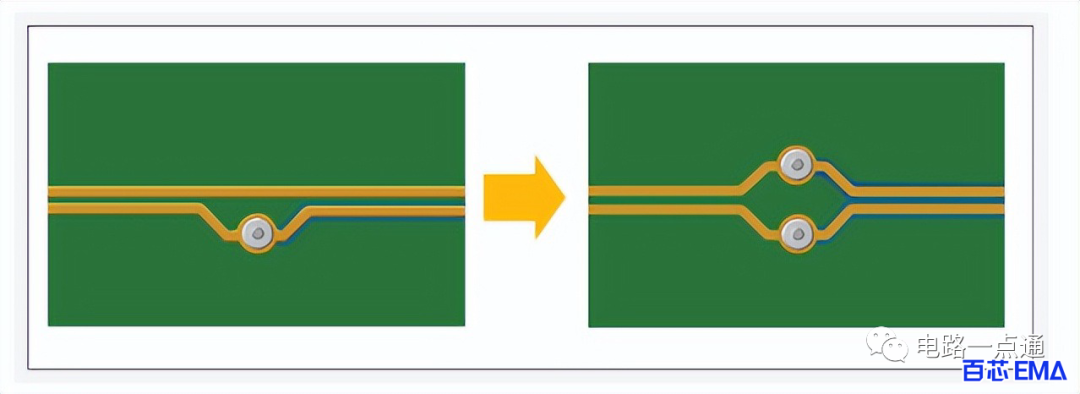

8、避免在差分對之間放置元器件和過孔

有助于減輕阻抗不連續性和EMI 問題

9、對稱布置差分對并保持信號平行

10、差分對走線時,兩條走線應走線在同一層它確保了阻抗要求的實現

在差分對中,走線應該在同一層上布線

11、使用蛇形線實現長度匹配

用來保持不同跡線和信號對之間到達目的地的時間 (時鐘偏差)。

12、將蛇形走線放置在長度不匹配的位置

確保了正負信號分量通過連接同步傳播。

13、在靠近彎曲處添加補償,最大距離為 15 毫米

14、差分對連接的每一段中的失配應單獨匹配

過孔用于將差分對分成兩段,它可以通過過孔同步傳播正信號和負信號。

在高速布局設計中,信號完整性和 EMC法規實施起著重要作用。

審核編輯:湯梓紅

-

電路板

+關注

關注

140文章

4952瀏覽量

97697 -

PCB設計

+關注

關注

394文章

4683瀏覽量

85557 -

高速信號

+關注

關注

1文章

226瀏覽量

17694 -

布局設計

+關注

關注

0文章

9瀏覽量

7397 -

時鐘信號

+關注

關注

4文章

448瀏覽量

28542

原文標題:高速信號布線規則14條總結

文章出處:【微信號:電路一點通,微信公眾號:電路一點通】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

設計規則13條:旁路電容設計指南

14條高速信號布局設計規則

14條高速信號布局設計規則

評論