前面我們介紹過《EMC的三大法寶之一:接地》和《EMC的三大法寶之一:接地(二)》,本次我們就不同接地方案對EFT/B測試的影響進行舉例分析。

Part 1

現象描述

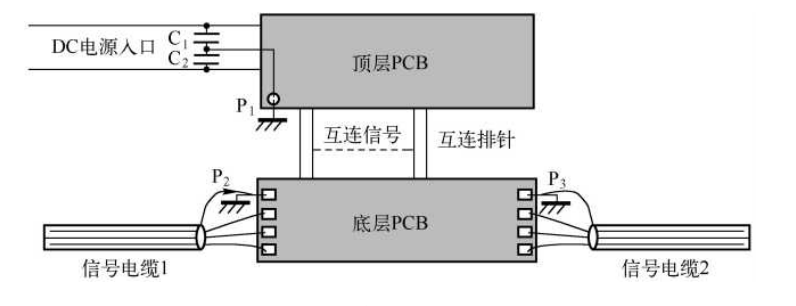

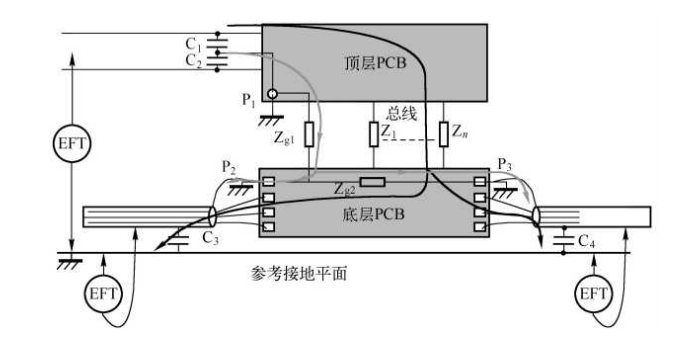

如下圖所示為某產品的結構圖:

在進行電源端口±2kV、信號端口±1kV的EFT/B測試時,有如下現象:

當 P1、P2、P3同時接地時, 測試全部Fail。

當只有P1接地時,電源端口的測試Pass,信號電纜1、2 測試Fail。

當P1、P2接地,P3不接地時,電源端口和電纜1測試Pass,線纜2測試 Fail。

當P1、P3接地,P2不接地時,電源端口和電纜2的測試Pass,信號電纜1測試Fail。

從結果來看,以上接地方式都不能讓測試完全通過。

究竟是什么原因導致的呢?遇到這樣的問題,可以從以下方面去分析:

確認接地是否良好(線的粗細、固定或者搭接方式是否合適),系統是單點接地還是多點接地。

找分布電容位置,畫系統等效原理圖,判斷EFT共模電流的流向,從而有針對性的去改善。

Part 2

原因分析

在分析原因之前,我們首先要了解EFT/B(電快速瞬變脈沖群波形)測試的實質和特點。

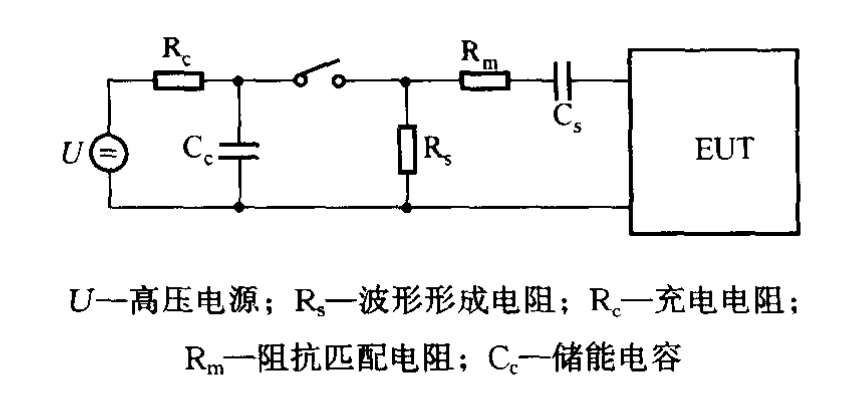

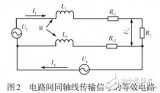

其主要是模擬電路中的感性負載(例如開關電源中的電感、電機等)斷開時產生的一連串的脈沖波形,其模擬發生器原理圖如下圖所示:

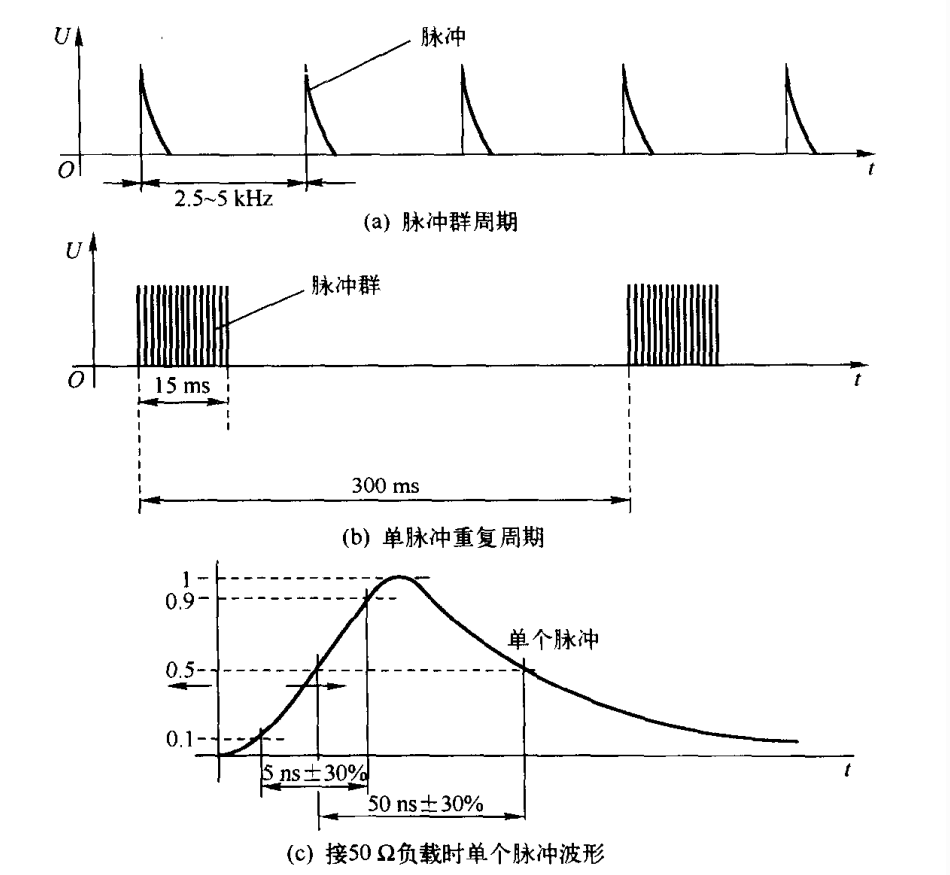

其產生的波形如下圖所示:

由上圖可以看出,其單個脈沖的上升延tr為5ns左右,半寬(歸一化幅值的0.5倍以上的寬度)T在50ns左右。

這樣周期性干擾波形具有豐富的諧波成分,周期性函數的傅里葉變換可得,其幅最大的諧波的頻率(通常為1次諧波)f=1/πtr,經計算約為60MHz。

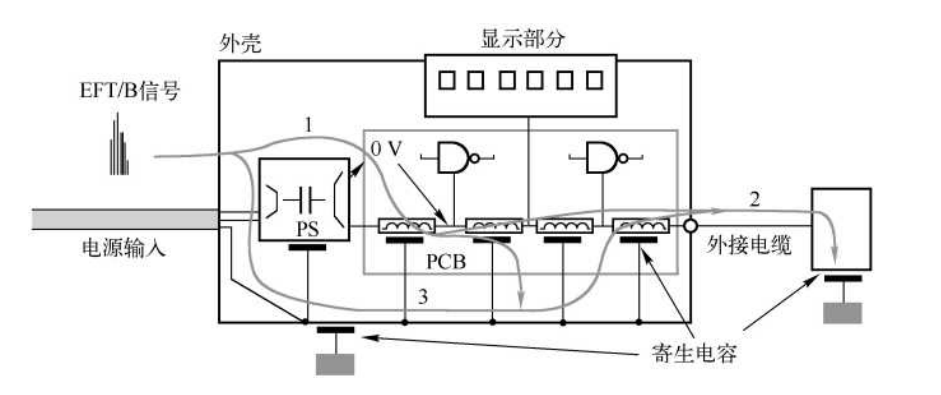

在系統中,電源線、信號線、EUT和參考接地板之間都有寄生電容(或者稱為分布電容)的存在,正是因為有這些等效的電容存在,才會為EFT/B干擾提供了高頻干擾路徑。

而這些干擾,通常是以共模電流的形式流入到電路中的各個單元中,進而對電路產生未知的影響,其影響設備的原理圖如下所示:

周期性的連續干擾脈沖會在電路中產生累積效應,累積到一定程度,超過電路所能夠承受的閾值,就會對電路產生影響。

基于這個理論,脈沖的周期越短(電容電還沒有放完就又開始充電,直至達到最大),對電路的影響越大。

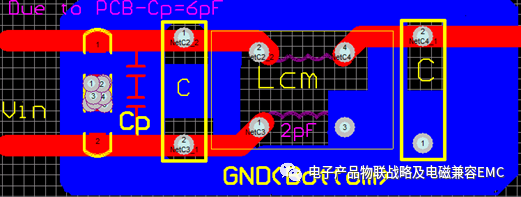

經過前面對EFT/B測試實質的分析,我們可以畫出前面產品EFT/B測試的原理圖:

測試時,EFT干擾脈沖群分別施加在電源端口、信號電纜1和2上,圖中:

C1、C2是產品電源輸入口的Y電容。

C3、C4是信號電纜對參考地的分布電容。

P1、P2、P3分別是三個接地點。

Z1~ Zn表示信號排針的阻抗。

Zg1表示地排針的阻抗。

Zg2表示 P2、P3之間互連PCB印制板布線的阻抗。

圖中的箭頭代表試驗時共模電流的流向,因此,當在EFT/B干擾信號的遠端進行接地(如P3接地)時,共模電流會從電流內部流過。

當共模電流流經電路內部時,內部電路的阻抗大小就決定了干擾電壓是否會超過電路中的某些判別閾值(如邏輯電平)。

在本產品中,上下電路互聯的排針在高頻下的阻抗較大(一般PCB上的接插件,其分布電感有520nH,一個雙列直插的24引腳的IC插座,會引入4-8nH的分布電感,有關分布電容或者分布電感的計算可以參考《PCB之分布電感&分布電容》)。

三個接地點之間是通過排針和PCB印制線接在一起的,阻抗較大,所以,需要通過單點接地來減少流過電路內部的共模電流,還需要想辦法降低三點之間的阻抗,從而使得共模干擾電壓最小。

我們用萬用表直接測量三點之電阻,發現地線電阻都是毫歐級別的,那為什么這么小的電阻和共模電流還會產生足以干擾電路正常運行的電壓呢?

那就不得不提電阻和阻抗的區別。

兩者概念區別如下:

電阻:指的是在直流狀態下導體對電流呈現的阻抗。

阻抗:指的是在交流狀態下導體對電流呈現的阻抗,和頻率有關,這個阻抗通常是由導體的等效電感產生的。

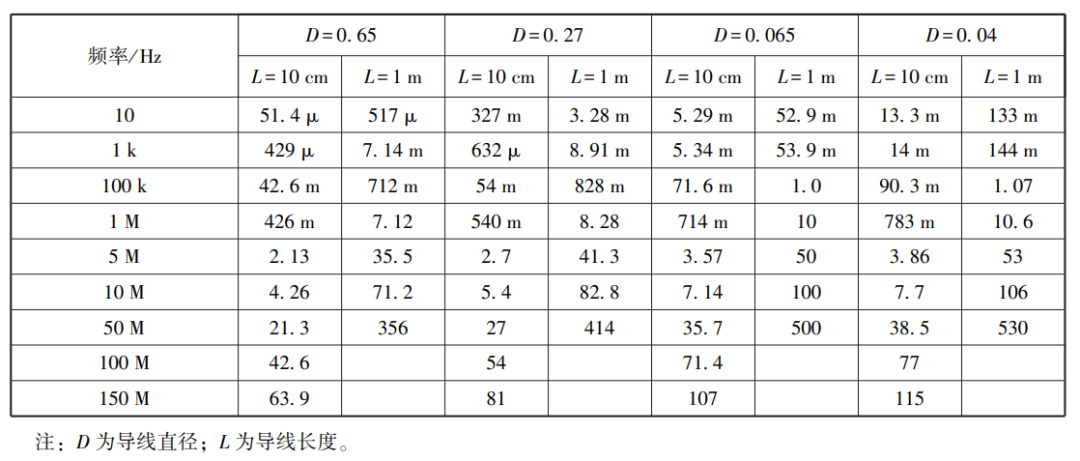

任何導體都有電感,而導體的阻抗和頻率成正相關,當頻率較高時,其阻抗遠遠大于其直流電阻。下面這個表格對比一目了然:

由表格可以看出:

對于1m長的線纜,它在10Hz的阻抗和在10MHz時的阻抗,相差1000倍甚至10萬倍,因此,對于高頻的電流流過地線時,其壓降也會很大。

增加導線的直徑可以有效地減小直流電阻,但是減小交流阻抗的作用有限。為了減少交流阻抗,在電路設計時,通常會采取平面的形式來布置,就像PCB中的完整的地平面。

像前文《EMC案例分析——連接器金屬外殼搭接不良對靜電放電抗擾度的影響》中介紹過的完整的、無過孔的地平面上任何兩點間在100MHz的頻率下, 阻抗可以認為是 3mΩ。

在這種地平面下,TTL電路可以承受600A的脈沖電流(此時的壓降為1.8V),受EFT/B發生器50Ω內阻的限值,其在4kV以下的最大電流只有80A。

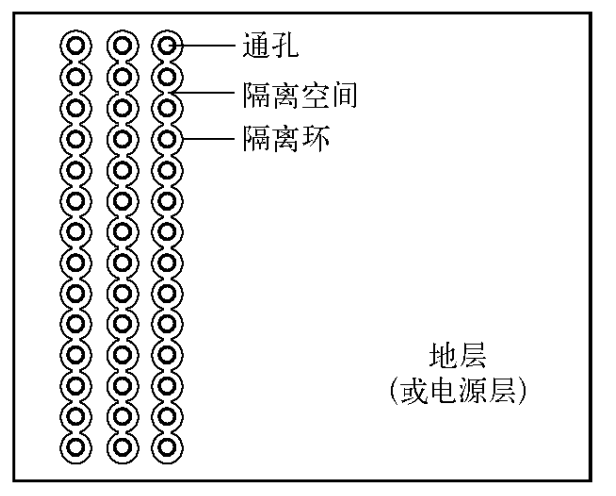

在實際的電路中,地平面上不可避免會有過孔或者縫隙,如下圖所示:

每1cm長的縫隙的等效電感為10nH,那么當80A的電流流過時,產生的壓降為:

U=LdI/dt=160A

式中:

L為縫隙等效電感。

dI為EFT/B產生的電流,此處假設為80A。

dt為EFT/B脈沖電流上升沿,此處假設為5ns。

這個壓降對普通的數字電路是非常危險的,這就需要通過接地、濾波、添加金屬平面等多種組合方式來解決干擾問題了。

可見,完整的地面對提高產品抗干擾能力非常重要,尤其對于不接地的設備來說,完整的地平面顯得尤為重要。

Part 3

處理措施

通過前面的分析,我們可以通過下面的方法來解決EFT/B干擾問題:

將多點接地改為單點接地,即P1接大地(PE),P2、P3僅接信號電纜的屏蔽層。

用一塊長寬比小于3的金屬片(可以認為阻抗比較低)將P1、P2、P3連接在一起。

經過以上整改之后,測試通過。

Part 4

思考和啟示

經過上面的分析,我們可以得到如下啟示:

在高頻,多點接地時的各個接地點之間的導體連接部分長寬比要保證小于5 (長寬比小于3更好)。

EFT/B干擾源的遠端一定不要接地,這會導致共模電流流過電路中的地平面,從而在地平面上產品壓降。

保持地平面的完整性,不但對EMS有很重要的作用,對EMI同樣很重要。

有關接地,要注意以下幾個方面:

對于高頻元件的布局要格外小心,保證其電流環路面積最小。

PCB或者系統分區布局,高頻噪聲電路和低頻電路分開。

PCB設計或者系統設計時,要保證干擾電流不會通過公共接地回路影響其它電路。

選擇接地點時,要保證環路電流、接地阻抗及電路的轉移阻抗最小。

在進行噪聲分析時,可以將流過接地系統的電流看成是噪聲的源頭。

對于非常敏感的電路,要保證將其連接在一個穩定的參考接地平面,并保證接地平面阻抗盡量小。

審核編輯:湯梓紅

-

模擬電路

+關注

關注

125文章

1556瀏覽量

102717 -

接地

+關注

關注

7文章

767瀏覽量

45656 -

PCB設計

+關注

關注

394文章

4683瀏覽量

85545 -

emc

+關注

關注

170文章

3914瀏覽量

183121

原文標題:EMC案例分析——不同接地方案對EFT/B測試的影響

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

YY-0505醫療器械EMC整改測試

脈沖群EFT整改措施和影響?|深圳比創達電子a

PCB設計考慮EMC的接地技巧

電子系統EMC設計中的同軸線接地方法研究

電快速脈沖群(EFT)設計-EMC系列 硬件設計筆記4

EMC案例分析:不同接地方案對EFT/B測試的影響

EMC案例分析:不同接地方案對EFT/B測試的影響

評論