德國慕尼黑,2023年9月5日——RISC-V定制計算領域的領導者Codasip宣布:公司現在可為其定制RISC-V處理器內核提供Tessent Enhanced Trace Encoder增強型追蹤編碼器解決方案,該解決方案即使在最復雜的異構和定制化設計中也能顯著提高生產效率。Tessent Embedded Analytics是西門子EDA嵌入式分析產品線的成員產品。通過這一聯合解決方案,開發人員可以有效地追蹤和調試芯片和軟件之間的問題,并能準確了解基于Codasip RISC-V processor處理器的最復雜定制設計的實時行為。

Codasip的RISC-V處理器完全可定制,并可完全適應應用的獨特需求。系統設計人員可以使用Codasip Studio工具鏈找到最佳軟件和硬件的權衡點,并實現最優功能和PPA(功率、性能、面積)。把針對處理器設計的可定制化處理器IP和工具組合在一起,使實現定制計算的自動化方法成為可能。為了使這種定制化服務對軟件開發人員可用,Codasip確保所有的工具都支持定制,包括編譯器和調試器。現在還包括追蹤解決方案。在SoC中加入追蹤功能可以大大加快曾經非常耗時的軟件調試任務,從而減少項目啟動時間和軟件開發的成本。Codasip之所以選擇與西門子EDA合作開發其Trace Encoder編碼器,是因為兩家公司都堅信在整個產品設計流程中都能有效地實現產品質量。這種對質量的關注使創新成為可能,即使在最復雜的異構和定制設計中,也能幫助客戶顯著提高生產效率。

Tessent Enhanced Trace Encoder增強型追蹤編碼器基于由調試和追蹤工作組(Debug andTrace Working Group)制定的RISC-V標準,該工作組由西門子的代表領導,西門子向RISC-V國際社區捐贈了Trace算法。然而,西門子的解決方案遠遠超出了RISC-V標準,提供了一個更高效的工具,在最復雜系統的開發中提供顯著的生產率效益,并且還支持自定義指令。它對系統進行詳細的檢查,以找到錯誤及其根本原因。它是周期精確的,這意味著開發人員可以深入了解每一條指令。

Codasip戰略和生態系統副總裁Mike Eftimakis評論道:“Codasip對自己的處理器IP提出了很高的質量標準。為了確保其成果可支持出色的系統,我們需要一個超越RISC-V標準的追蹤解決方案。Tessent Enhanced Trace Encoder增強型追蹤編碼器專為我們客戶正在開發的復雜型和定制化系統進行了優化。”

“Tessent Embedded Analytics嵌入式分析工具可實現全系統實時調試和部署后的分析,從而幫助SoC提供商專注于產出高質量的、創新的產品等關鍵任務,并將其快速推向市場,”Siemens EDA Tessent部門副總裁兼總經理Ankur Gupta說道。“Codasip在幫助客戶滿足這些要求方面享有卓越的聲譽,我們很高興能夠與其成為合作伙伴關系。”

此外,Codasip將直接向客戶提供Tessent Enhanced Trace Encoder增強型追蹤編碼器解決方案,以簡化合同的復雜性。

審核編輯:彭菁

-

編碼器

+關注

關注

45文章

3639瀏覽量

134429 -

軟件開發

+關注

關注

0文章

612瀏覽量

27353 -

RISC-V

+關注

關注

45文章

2271瀏覽量

46131 -

codasip

+關注

關注

0文章

37瀏覽量

6232

原文標題:Codasip與西門子EDA再度攜手,共同為定制處理器提供追蹤解決方案

文章出處:【微信號:Codasip 科達希普,微信公眾號:Codasip 科達希普】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

增量式拉線編碼器:精準測量與位移控制的優選解決方案

二進制編碼器的種類及特點

磁電編碼器和光電編碼器的區別

自編碼器的原理和類型

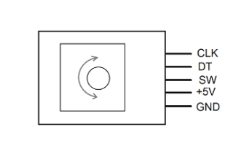

帶Arduino的旋轉編碼器設計 旋轉編碼器的工作原理和特點

STM32F4沒有Encoder Mode+Index的模式只有Encoder Mode,還可以使用ABZ相的編碼器嗎?

永磁同步電機的矢量控制 帶編碼器的電機-AB增量型編碼器應用指南

編碼器好壞怎么判斷,編碼器原理

編碼器的6種常見問題

磁性編碼器和光電編碼器的比較

編碼器:6種常見問題 選擇合適的解決方案 有效延長使用壽命

編碼器:受干擾的方法及解決方案

Codasip向客戶提供Tessent Enhanced Trace Encoder增強型追蹤編碼器解決方案

Codasip向客戶提供Tessent Enhanced Trace Encoder增強型追蹤編碼器解決方案

評論