在數字設計中,fifo是數據操作任務所需的普遍結構,如跨時鐘域、低延遲內存緩沖和總線寬度轉換。

XILINX FIFO Generator IP生成先進先出(FIFO)存儲器隊列,特別適于需要按次序進行數據存儲和檢索的應用。該IP為 FIFO 配置提供優化的解決方案,使用少量資源實現最高的性能(高達 500MHz)。用戶可自定義:寬度、深度、狀態標志、存儲器類型以及讀寫端口長寬比等。

該IP的主要特性為:

- FIFO 深度可達 4,194,304 個字

- 原生 FIFO 配置支持從 1 到 1,024 位的 FIFO 數據寬度,而 AXI FIFO 配置的該數據寬度則高達 4,096 位

- 非對稱長寬比(讀寫端口比可從 1:8 到 8:1)

- 支持獨立或通用時鐘域

- 可選存儲器類型(Block RAM、分布式 RAM、移位寄存器或內建 FIFO)

- 原生接口或 AXI 接口(AXI4、AXI4-Lite 或 AXI4-Stream)

- 同步或異步復位選項

- 支持數據包模式

- 支持糾錯 (ECC) 和注入特性,適用于特定配置

- 支持首字直接通過 (FWFT)

- 支持嵌入式寄存器選項,適用于基于 Block RAM 和內建 FIFO 原語的實現方案

- 支持 — 空/滿、基本空/滿和可編程空/滿信號

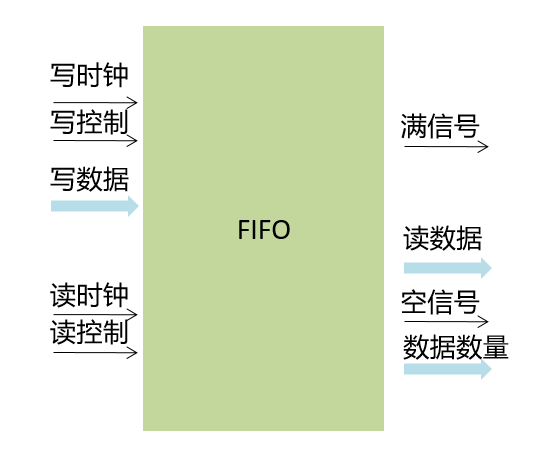

原始接口下該IP的接口為:

AXI 接口派生自本來接口fifo,因此它們之間的許多行為是共同的。ready信號是基于FIFO中空間的可用性生成的,并且 保持高位以允許對FIFO進行寫操作。只有在FIFO中沒有剩余空間來執行額外的寫操作時,ready信號才會被拉低。根據FIFO中數據的可用性生成vaild信號,并保持高電平以允許從 FIFO執行讀取。只有當沒有數據可從 FIFO讀取時,vaild信號才被拉低。AXI接口如下圖:

將information信號映射到Native 接口fifo的din和dout總線上。AXI FIFO的寬度是通過連接AXI接口的所有information信號來確定的。information信號包括所有的AXI 信號,除了有效的和準備好的握手信號。

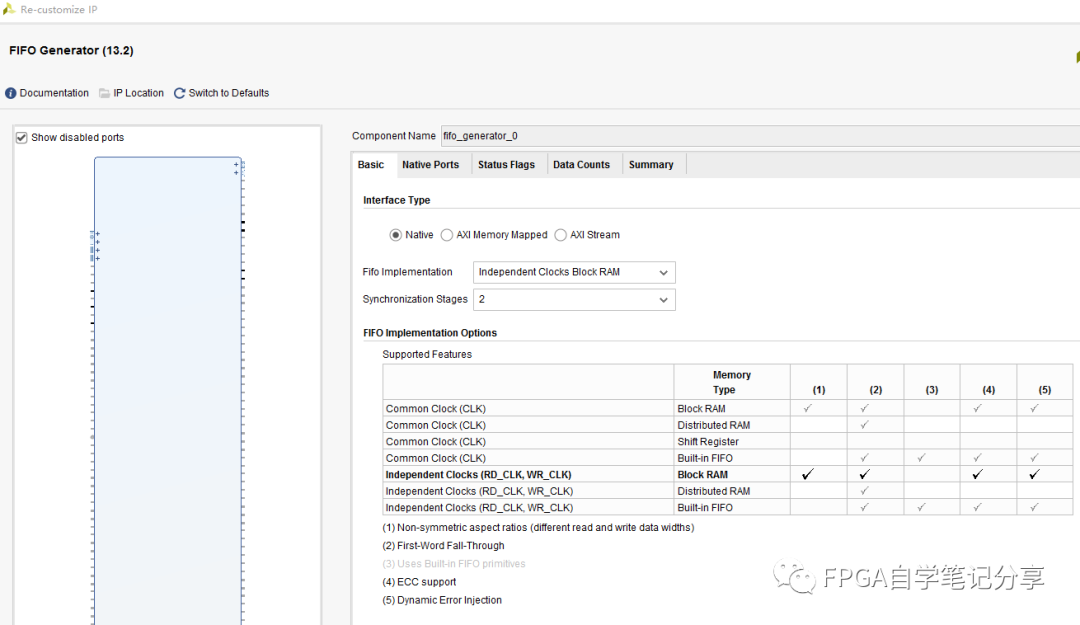

XILINX FIFO Generator IP支持Block RAM、分布式 RAM、移位寄存器或內建 FIFO,每種ram夠成特性如下:

在ip的gui界面上同樣有上述信息的詳細描述如下圖,在實際使用時根據需要使用的特性,選擇一種合適的底層資源即可。

FPGA使用FIFO最常用的就是跨時鐘域處理,處理流程如下圖。寫時鐘域,根據限寫使能wr_en產生寫數據計數器然后將其轉換為gray碼,多bit跨時鐘域到讀側。讀時鐘域,根據限讀使能rd_en產生讀數據計數器然后將其轉換為gray碼,多bit跨時鐘域到讀側。讀側根據自己時鐘域產生的讀計數器和跨時鐘域過來的寫計數器值,得到fifo內的數據量,從而產生相應的empty/almost empty/prog empty/rd_data_count.寫側根據自己時鐘域產生的寫計數器和跨時鐘域過來的讀計數器值,得到fifo內的數據量,從而產生相應的full/almost full/prog full/wr_data_count.

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603805 -

Xilinx

+關注

關注

71文章

2167瀏覽量

121551 -

fifo

+關注

關注

3文章

389瀏覽量

43701 -

總線

+關注

關注

10文章

2888瀏覽量

88128 -

數字設計

+關注

關注

0文章

47瀏覽量

22304

發布評論請先 登錄

相關推薦

XILINX FPGA IP之Clocking Wizard詳解

XILINX FPGA IP之MMCM PLL DRP時鐘動態重配詳解

Xilinx FPGA IP之Block Memory Generator功能概述

XILINX FPGA IP之AXI Traffic Generator

XILINX FPGA IP之FIFO Generator

XILINX FPGA IP之FIFO Generator

評論