點擊上方藍字關注我們

系統的復位對于系統穩定工作至關重要,最佳的復位方式為:異步復位,同步釋放。以下是轉載博客,原文標題及鏈接如下:復位最佳方式:異步復位,同步釋放

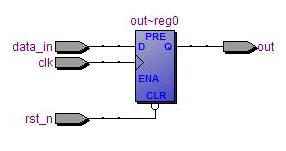

異步復位;

異步:

always@(posedgeclkornegedgerst_n)

if(!rst_n)

(優點:占用較少邏輯單元

缺點:可能會產生競爭冒險)

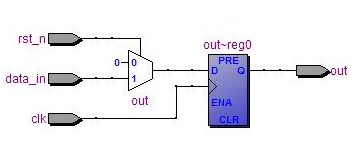

同步:always @(posege clk or posedge rst_n)

If(!rst_n)

(優點:可以盡量點少競爭冒險的可能

缺點:會占用更多的邏輯單元)

Altera 最佳解決辦法:異步復位,同步釋放

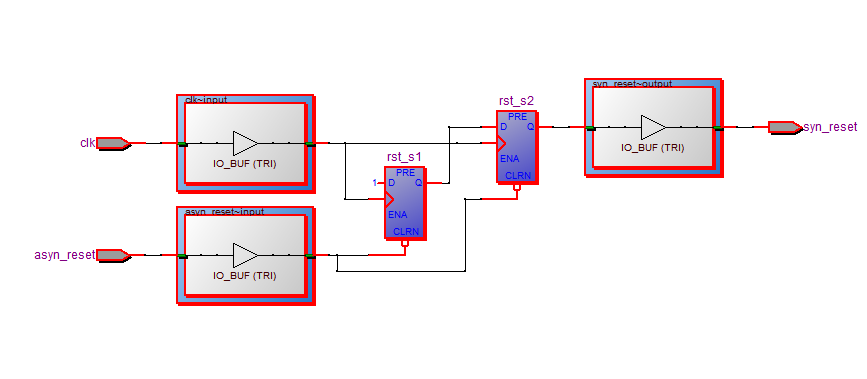

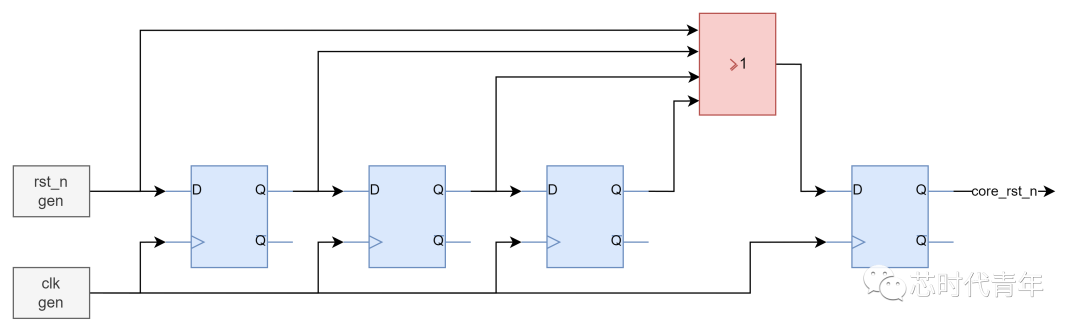

//異步復位 同步釋放rtl視圖

原理:

所謂異步復位和同步釋放,是指復位信號是異步有效的,即復位的發生與clk無關。后半句“同步釋放”是指復位信號的撤除(釋放)則與clk相關,即同步的。

下面說明一下如何實現異步復位和同步釋放的。

異步復位:顯而易見,rst_async_n異步復位后,rst_sync_n將拉低,即實現異步復位。

同步釋放:這個是關鍵,看如何實現同步釋放,即當復位信號rst_async_n撤除時,由于雙緩沖電路的作用,rst_sync_n復位信號不會隨著rst_async_n的撤除而撤除。

假設rst_async_n撤除時發生在clk上升沿,如果不加此電路則可能發生亞穩態事件(在始終上升沿附近rst置1,這時候建立時間還不夠長,數據可能還未打入寄存器,導致輸出不確定)。但是加上此電路以后,假設第一級D觸發器clk上升沿時rst_async_n正好撤除,則D觸發器1輸出高電平“1”,此時第二級觸發器也會更新輸出,但是輸出值為前一級觸發器次clk來之前時的Q1輸出狀態。顯然Q1之前為低電平,顧第二級觸發器輸出保持復位低電平,直到下一個clk來之后,才隨著變為高電平。即同步釋放。

代碼實現:(Altera 官方資料)

module reset_best(clk,asyn_reset,syn_reset);

input clk;

input asyn_reset;

output syn_reset;

reg rst_s1;

reg rst_s2;

always @( posedge clk ,posedge asyn_reset)

begin

if(asyn_reset)

begin

rst_s1<=1'b0;

rst_s2<=1'b0;

end

else

begin

rst_s1<=1'b1;

rst_s2<=rst_s1;

end

end

assign syn_reset=rst_s2;

endmodule

有你想看的精彩 至芯科技FPGA就業培訓班——助你步入成功之路、9月23號北京中心開課、歡迎咨詢! FPGA學習:精簡指令集RISC_CPU 至芯FPGA初級課程之 FIFO

掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:FPGA學習-異步復位,同步釋放

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

602997

原文標題:FPGA學習-異步復位,同步釋放

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

怎么判斷同步清零和異步清零

異步線路和同步線路怎么區分

FPGA同步復位和異步復位

FPGA異步信號處理方法

L431采用PLL異步時鐘,復位后ADC采樣值發生偏差的原因?

同步級聯和異步級聯的區別 異步級聯和同步級聯分別要注意什么

什么是復位同步電路 reset synchronizer?

SPWM脈寬調制是異步還是同步?

異步復位異步釋放會有什么問題?FPGA異步復位為什么要同步釋放呢?

FPGA學習-異步復位,同步釋放

FPGA學習-異步復位,同步釋放

評論