DC/DC開關電源由于其效率高、體積小等優點是現代電子產品設計中不可或缺的一環,其重要性不言而喻。由于設計上采用的開關型器件會導致出現快速的電壓變化率和電流變化率,產品在電磁兼容性的測試上容易出現問題并使得開發周期變長,影響產品上市時間,對于應用環境比較復雜的工業類產品此問題顯得尤為突出。

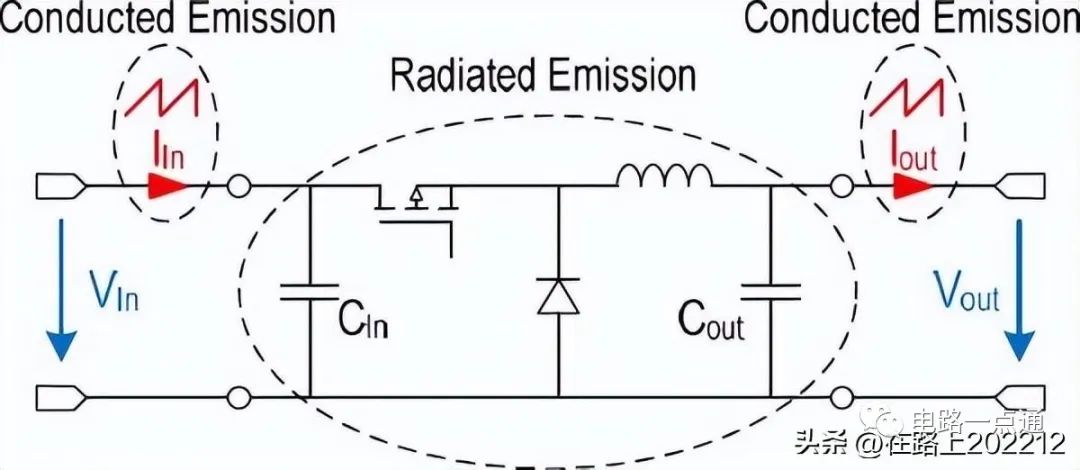

本文將從干擾源、元器件、濾波器以及布局等幾個方面對DC/DC開關電源設計提出相關的注意事項,幫助工程師們了解如何設計出符合電磁兼容性的DC/DC開關電源。一、 了解DC/DC開關電源中噪聲源要處理DC/DC開關電源產生的電磁兼容問題,首先需要對電源產生的噪聲源進行分析,找到造成輻射發射和傳導發射超標的源頭。在使用開關電源的情況下,除去開關頻率及其諧波造成的干擾外,暗室測量中還會顯示30 MHz至400 MHz的寬帶干擾頻譜,原因之一是開關管陡峭的開關沿,例如MOSFET輸出電容CDS、結電容和反向恢復肖特基二極管的寄生電容和導體走線的寄生電感共同導致高頻LC振蕩電路。下圖所示為造成輻射發射和傳導發射的噪聲源。

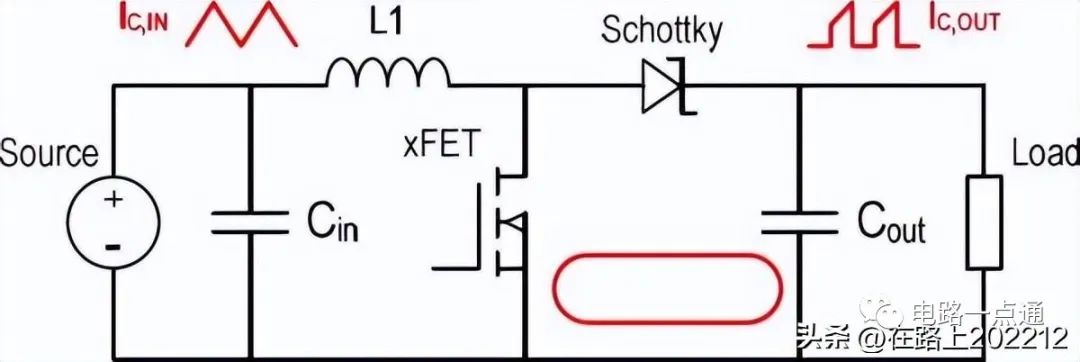

此外,根據DC/DC開關電源不同的拓撲結構,需要關注的著重點會存在一定差異,比如下圖所示的BUCK電路由于輸入端電流的不連續性,其含有高頻成分更多,因此輸入端的環路控制及濾波器會更加關鍵。

而如下圖所示的BOOST電路由于關鍵環路的不同,其著重點應該放在輸出環路上。當然重點關注關鍵環路并不意味著其他環路部分可以忽略。

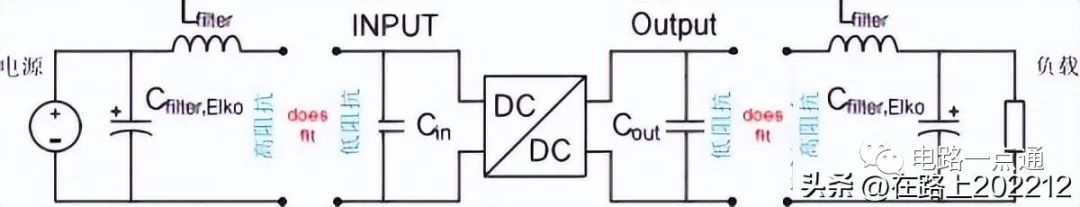

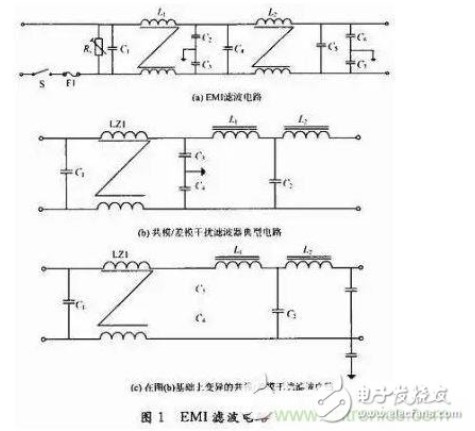

二、 設計DC/DC開關電源中輸入濾波器現代DC/DC開關電源中通常具有從250 kHz到4 MHz的開關頻率。如下圖所示,LC濾波器特別適合于控制基波及其高次諧波,理論上能夠實現每十倍頻最高40 dB的抑制,并且還可以達到低至kHz范圍的截止頻率。在實際應用中,合適的經驗法則是將濾波器的截止頻率設置為開關頻率的約十分之一,當然在電磁兼容性測試中如果存在超出限值仍然過高的情況下,還可考慮將截止頻率設置得更低,從而增加抑制效果。

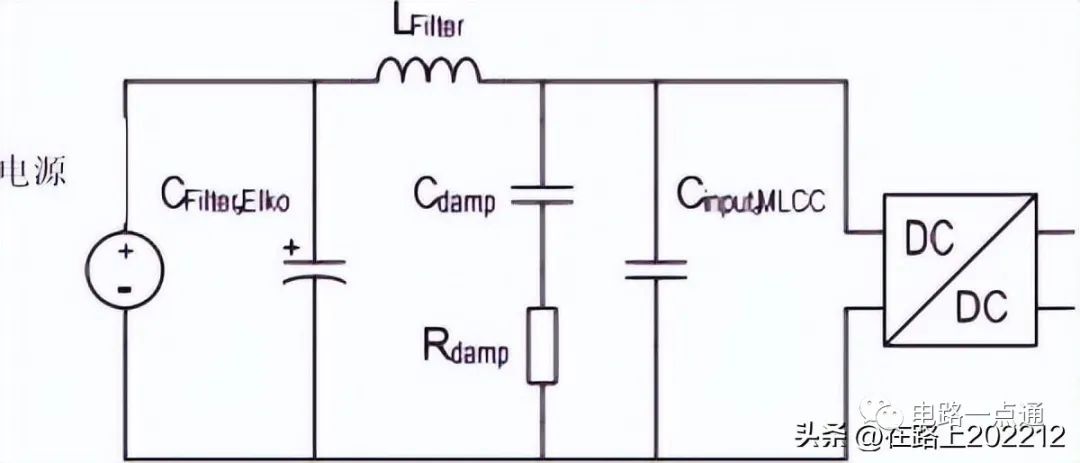

在加入濾波器設計后,實際在某些情況下,DC/DC開關電源的輸入端可能會發生振蕩。這種振蕩是由所謂的負輸入阻抗及加入的LC濾波器電路共同引起的,此時濾波器電路的電感和電容作為一個放大諧振峰的諧振電路。當前處理這種不良影響的最佳方法是主動抑制LC濾波器電路,通常會通過如下圖所示加入RC串聯電路來實現。

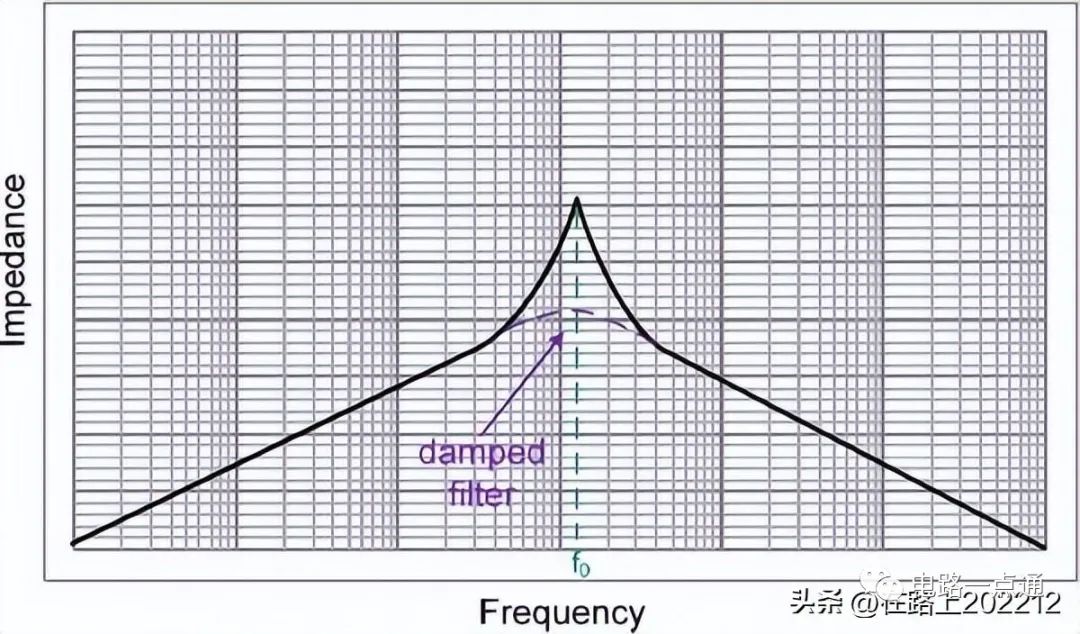

這種方法的目的是使諧振電路因子Q 值降低,從而減小發生諧振時的濾波器阻抗,如下圖所示,可以看到加入RC串聯電路之后濾波器的阻抗在諧振頻點已經下降。

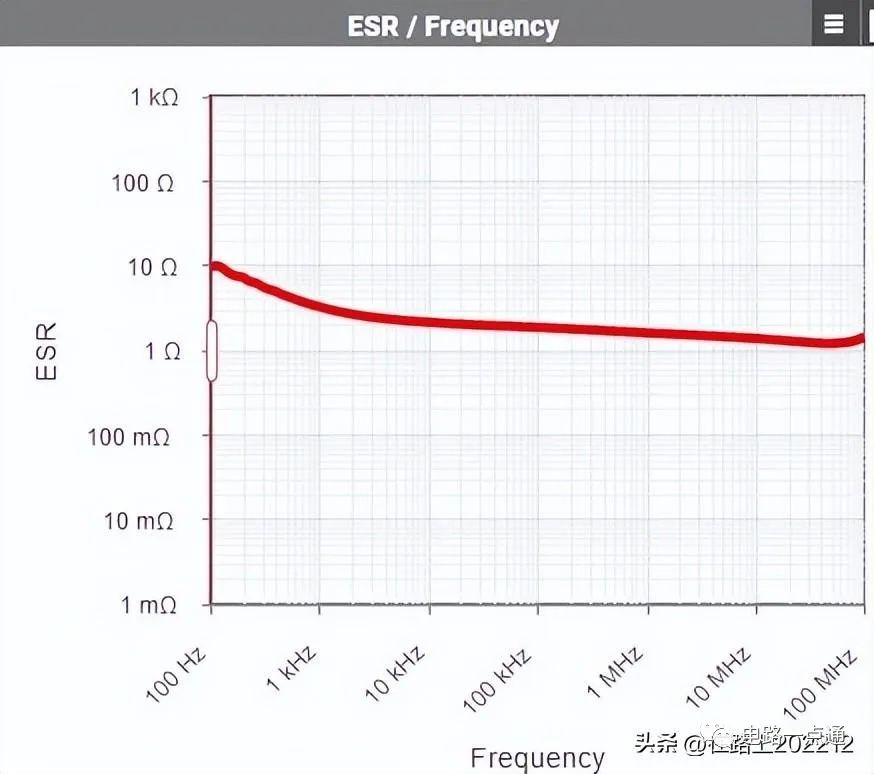

在許多情況下,也有使用具有較高ESR的電解電容器代替,但需要注意的是,ESR是一個會隨頻率和溫度發生變化的參數。采用伍爾特的REDEXPERT在線平臺可以看到頻率對于ESR帶來的影響,如下圖所示,圖中是一顆10uF/ 50V的鋁電解液電容對應ESR隨頻率的變化曲線。

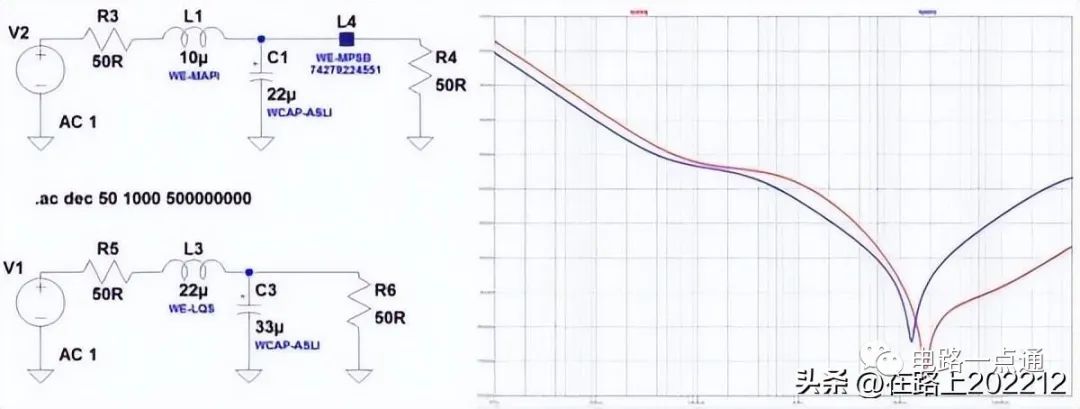

此外,如果要增加濾波器高頻處(例如大于10MHz)的濾波效果,可以考慮加入磁珠,下圖中通過仿真軟件LTspice給出了LC濾波器以及加入磁珠L4之后組成的LCL濾波器在噪聲抑制特性上的差異,可以看到增加磁珠之后對于濾波器在高頻處噪聲抑制效果帶來的好處,但在實際應用時需要注意電流對于磁珠阻抗的影響。

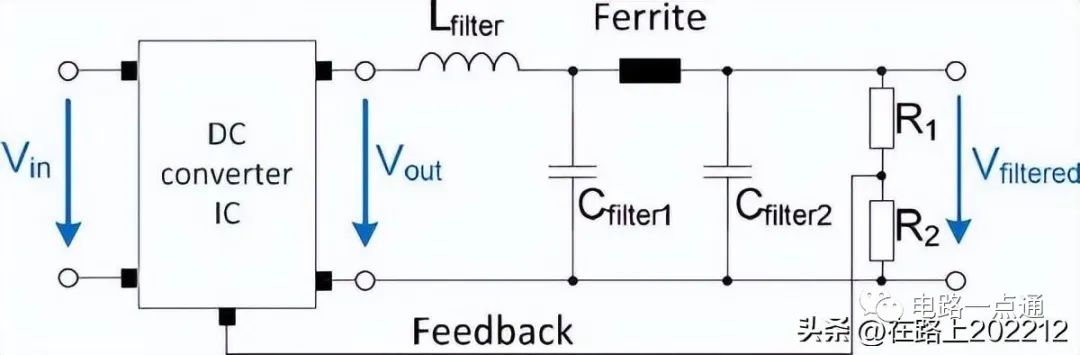

三、 設計DC/DC開關電源中輸出濾波器輸出端濾波器同樣有其需要注意的地方,如下圖所示,為了增強高頻抑制特性,輸出端加入了包含磁珠的濾波器,但考慮在輸出電流較大的情況下電感以及磁珠的直流電阻RDC帶來的影響,將濾波器放入了DC/DC開關電源的反饋網絡之內,從而消除直流壓降帶來的影響。

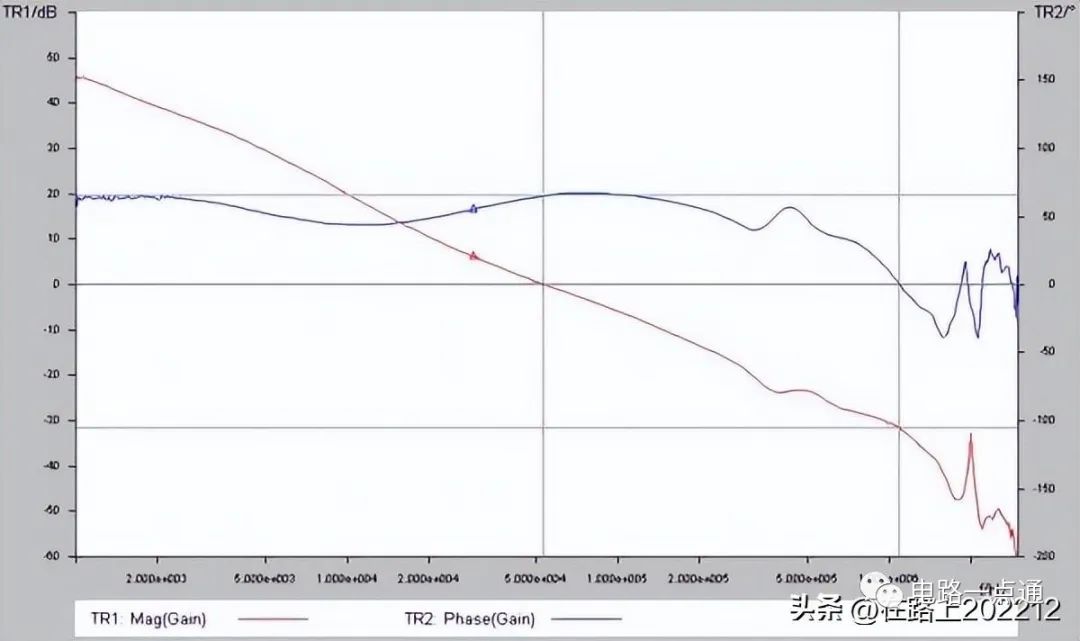

但反饋網絡內的濾波器件可能會帶來不希望的相移,從而使得開關電源的環路穩定性出現問題,降低環路的增益裕量和相位裕量。在極端情況下,甚至會使得環路不穩定并導致輸出電壓產生振蕩。實際設計中,增益裕量要求大于12dB且相位裕量大于45°的環路能夠保證環路的穩定性,從而使得在外界的激勵下輸出不會產生振蕩。下圖中是針對一個穩定的BUCK電路進行反饋環路測試之后繪制的伯德圖,從中可以看出增益裕量為32dB和相位裕量為56°。

環路補償通常可以作為環路穩定性出現問題的主要措施,但需要硬件工程師掌握一定的自動控制理論知識,同時熟悉不同補償電路的方案以及結合實際操作經驗。此外,所有工作在連續模式下的BOOST電路在做環路補償時還需要考慮到右半平面零點RHPZ的問題,進一步加大了環路補償的難度。所以,可以嘗試將濾波器電路放置在反饋環路網絡之外,通過挑選直流電阻RDC更小的磁性器件來減小壓降帶來的影響。四、DC/DC開關電源中如何器件選型電感作為DC/DC開關電源中的關鍵器件之一,不僅發揮著儲存傳遞能量、濾波等作用,對于開關電源的效率及成本也有較大的影響,此外電感的發熱及損耗問題是工程師們很關注的問題,利用REDEXPERT在線平臺,可以快速、輕松、精確地選擇合適的電感(功率電感選型請參考文檔ANP039),同時還可以根據不同器件復雜的交流和直流損耗、器件產生的溫升以及它們的規格參數如尺寸、額定電流等,對它們進行比較。下圖中是對電感的在BUCK-BOOST電路中一個應用案例,當輸入相應的設計參數,即可方便得到電感的損耗及溫升等,由于平臺中采用了更符合實際工況的模型以及加入了實測數據,相比傳統的公式法其給出的結果會更貼近實際情況,電路詳細設計請參考ANP049。

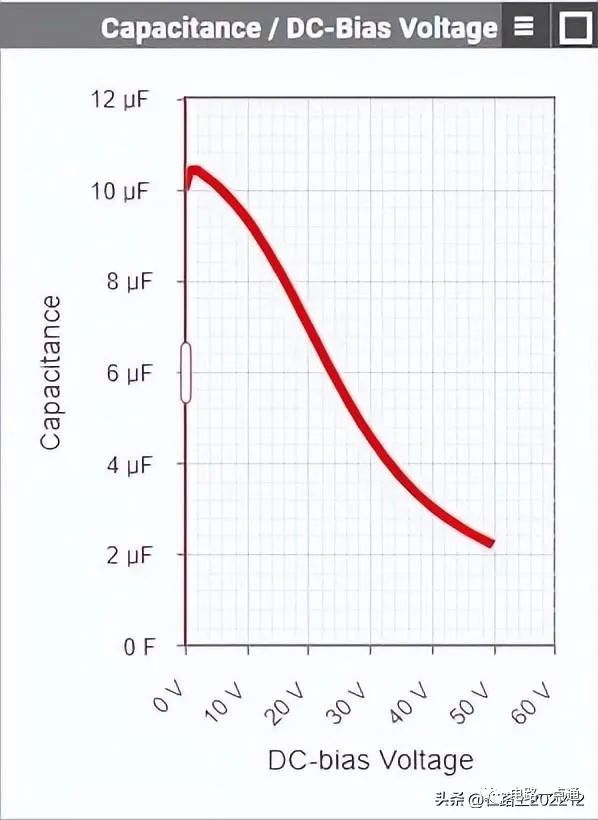

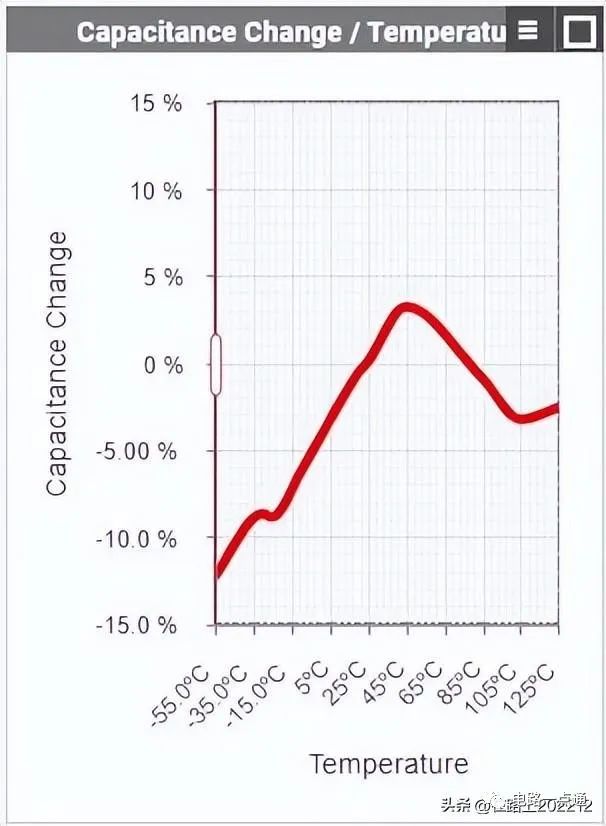

陶瓷電容MLCC由于體積小,寄生參數ESL及ESR小等優勢常常會受到工程師們的青睞,但當使用二類MLCC(如X7R及X5R等)作為濾波器時,需要考慮陶瓷電容實際工作時受到電壓偏置及溫度等帶來的影響。下圖中為通過REDEXPERT在線平臺看到的一顆10uF/ 50V的X7R電容容值隨外部施加電壓及溫度的變化曲線。

可以看到使用二類陶瓷電容受電壓及溫度的影響會使得濾波器截止頻率將在工作中發生較大程度的偏差,這也是在設計用于DC/DC開關電源的濾波器,當二者容量相當時,還會經常見到使用體積較大的鋁電解質電容器的原因。五、 DC/DC開關電源中器件的布局布線為降低DC/DC開關電源造成的傳導發射及輻射發射等電磁兼容性問題概率,對于開關電源而言從器件布局布線的角度來減小環路面積以及保證濾波器的性能發揮至關重要。通常這些措施包含但不限于: 1. 將關鍵環路涉及的器件盡量擺放在一起從而減小環路面積; 2. 針對高頻濾波的陶瓷電容盡量放置在開關管或IC等產生快速的電壓變化率和電壓變化率的地方; 3. 通過短而粗的走線來減小走線寄生感抗,特別是接地線的處理; 4. 通過加入多個過孔來減小其寄生電感; 5. 合理連接信號地和功率地,通過單點連接能夠保證信號地盡量少得被功率地干擾; 6. 對于表層大面積覆銅需要合理使用以免形成不必要的天線; 7. 布置輸入和輸出濾波器電路時,盡可能消除與電路主要部分的容性和感性耦合; 8. 濾波器電路下面沒有覆銅,如有中間層也是如此處理,從而避免高頻噪聲的耦合; 9. 設計LCL的T型濾波器時,盡可能消除三個器件內不必要的容性和感性耦合。

審核編輯:彭菁

-

電磁兼容

+關注

關注

54文章

1872瀏覽量

97866 -

開關電源

+關注

關注

6459文章

8328瀏覽量

481758 -

電容

+關注

關注

100文章

6036瀏覽量

150269 -

濾波器

+關注

關注

161文章

7796瀏覽量

177996

原文標題:DC/DC 開關電源設計中的EMC考慮(干擾源、元器件、濾波器)

文章出處:【微信號:電路一點通,微信公眾號:電路一點通】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

進行開關電源的電磁兼容性設計

深度剖析:通信開關電源電磁兼容性問題

開關電源的PCB電磁兼容設計要點分析

開關電源的PCB電磁兼容設計要點分析

如何設計出符合電磁兼容性的DC/DC開關電源

如何設計出符合電磁兼容性的DC/DC開關電源

評論