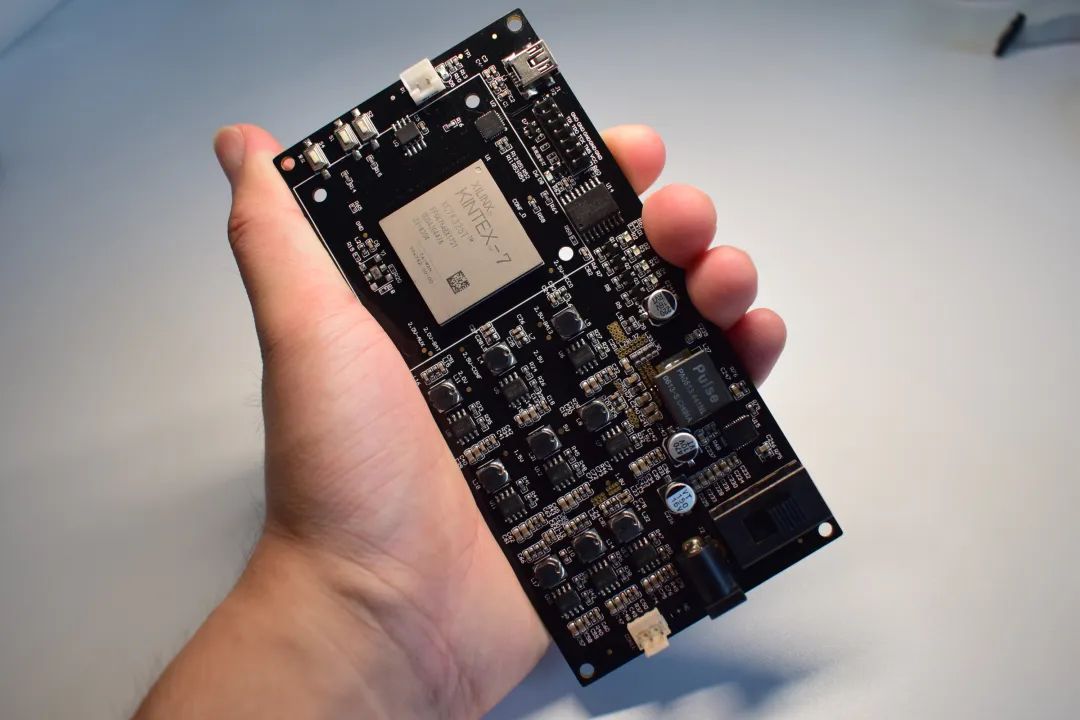

板子的整體尺寸很小巧,和手掌差不多大,外設(shè)也很簡單:

板子的整體尺寸很小巧,和手掌差不多大,外設(shè)也很簡單:-

12v供電,帶一個(gè)散熱器

-

FPGA芯片是Xilinx XC7K325T,F(xiàn)FG676封裝,芯片等級(jí)2I,生產(chǎn)日期是2017年21周

-

4路LED

-

3路輕觸按鍵,其中一路是Config

-

1路USB串口,CP2102轉(zhuǎn)換芯片

-

1顆Spansion 128Mb QSPI Flash S25F128

-

1顆有源差分時(shí)鐘200MHz

-

標(biāo)準(zhǔn)2.54mm 14P下載接口

1. 什么是邊界掃描?

提到邊界掃描,就不得不提JTAG,因?yàn)檫吔鐠呙枋荍TAG接口的功能之一。JTAG,是Joint Test Action Group的簡稱,即聯(lián)合測(cè)試行為小組。JTAG,對(duì)于電子行業(yè)的工程師們來說再熟悉不過了,無論是搞單片機(jī)、ARM開發(fā),還是FPGA、DSP開發(fā),都離不開這個(gè)接口,它不僅可以進(jìn)行程序下載,還能在線調(diào)試Debug,簡簡單單幾根線就完成了如此強(qiáng)大的功能,大大的提高了開發(fā)效率。但是,你知道嗎?JTAG協(xié)議的設(shè)計(jì)初衷,并不是用來下載程序的。JTAG中的'T',是Test的縮寫,沒錯(cuò)!JTAG接口被設(shè)計(jì)之初,就是用來測(cè)試的!上世紀(jì)90年代,集成電路、芯片設(shè)計(jì)產(chǎn)業(yè)開始迅速發(fā)展,同時(shí),也面臨著諸多問題:芯片管腳和晶圓之間的連接如何確定是正常的?芯片管腳之間是沒有短路的?芯片被焊接到PCB板上之后,如何保證焊接是良好的,沒有短路、開路?芯片外圍的電路和與之互聯(lián)的芯片是正常的呢?尤其是一些BGA封裝的芯片,無法使用探針等方式來直接測(cè)量芯片的管腳。面對(duì)這些問題,Philips、TI等半導(dǎo)體廠商在1985年成立了聯(lián)合測(cè)試行動(dòng)小組 ,即JTAG,用來解決這些問題。盡管人們認(rèn)為 IEEE 1149.1 標(biāo)準(zhǔn)實(shí)際上就是JTAG,不過該標(biāo)準(zhǔn)的官方稱謂是“標(biāo)準(zhǔn)測(cè)試訪問端口與邊界掃描架構(gòu) (Standard Test Access Port and Boundary-Scan Architecture)”。它定義了利用邊界掃描檢測(cè) PC 電路板的檢測(cè)訪問端口 (TAP) 等。JTAG協(xié)議發(fā)展到現(xiàn)在,目前主要有三個(gè)典型應(yīng)用:-

程序下載。即目前最常用的一個(gè)功能,它可以把用戶程序下載到芯片內(nèi)部的Flash中。

-

程序調(diào)試。即實(shí)時(shí)監(jiān)控程序的運(yùn)動(dòng)狀態(tài),并且可以通過加入斷點(diǎn)的方式來實(shí)時(shí)調(diào)試程序。

-

邊界掃描。即Boundary-scan,也就是JTAG設(shè)計(jì)的初衷,主要用于芯片本身和PCB電路板的硬件測(cè)試。

2. JTAG硬件接口

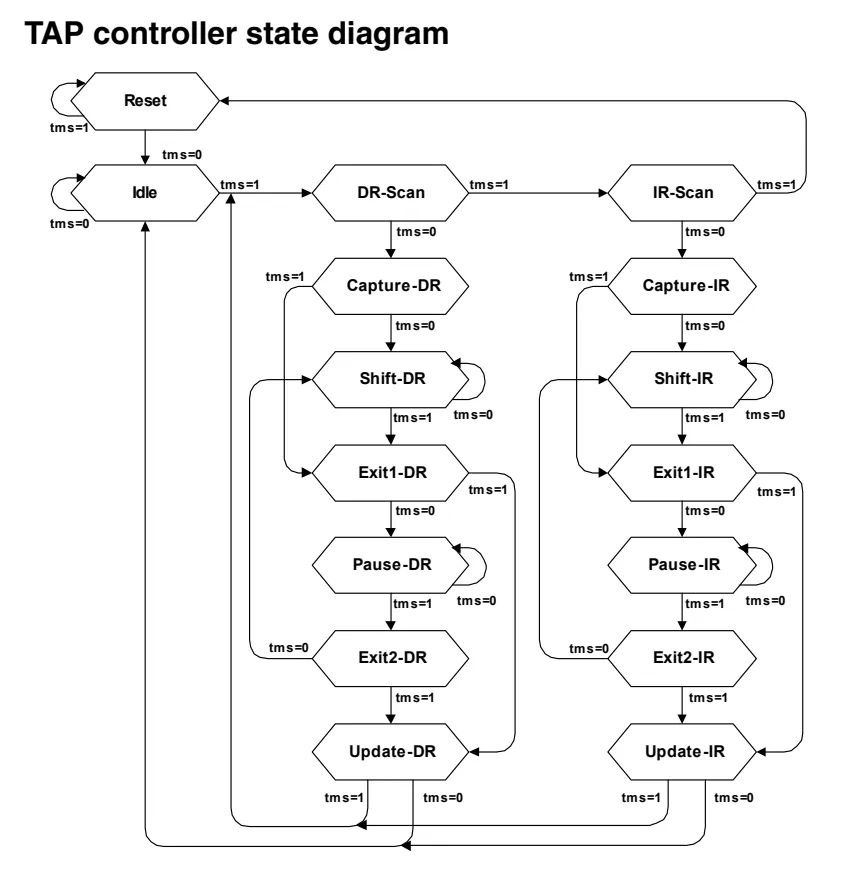

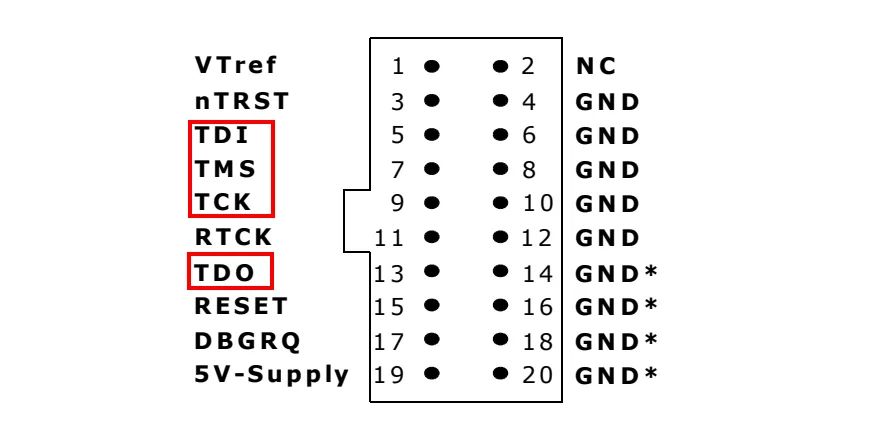

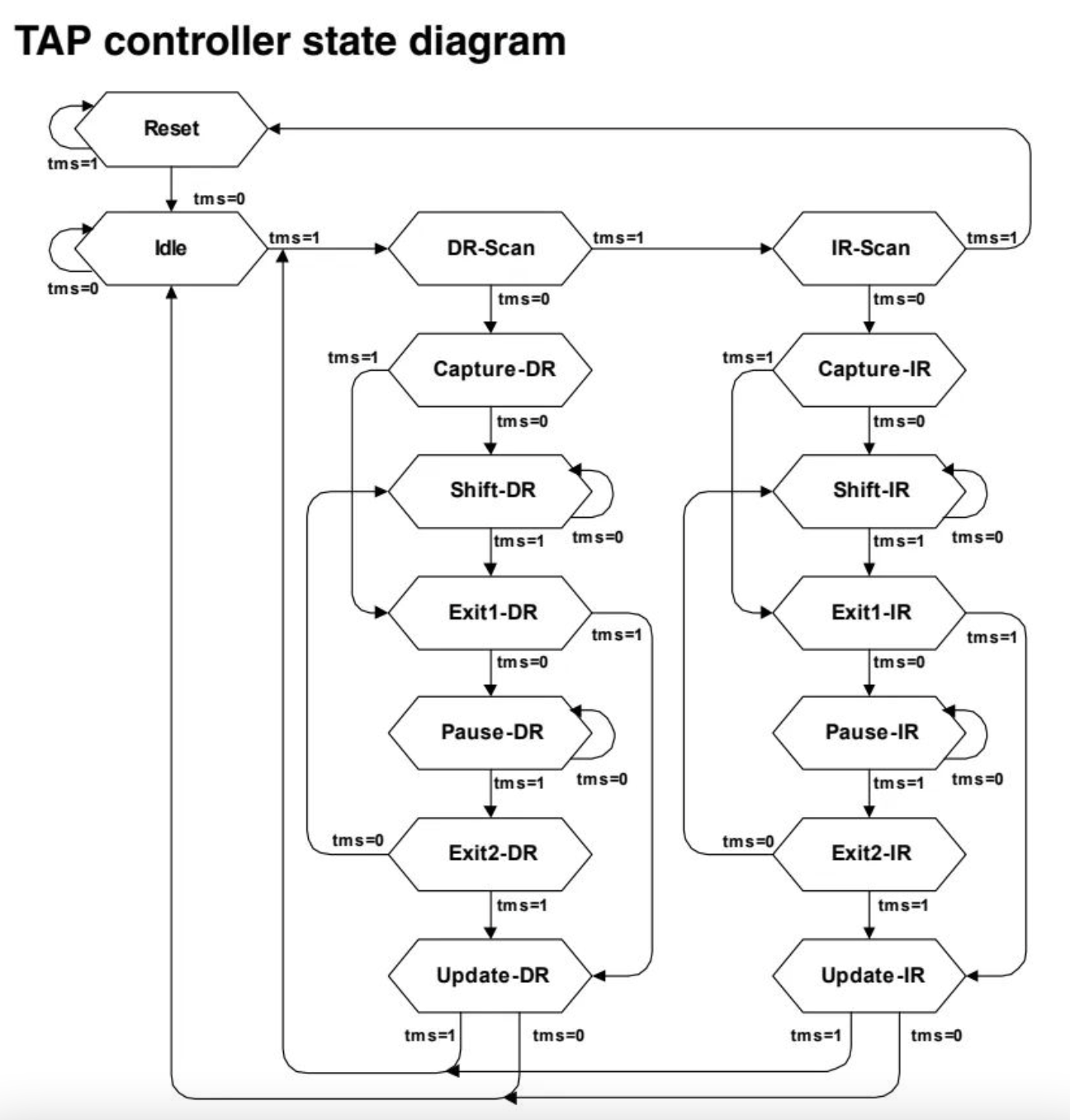

JTAG協(xié)議工作的基本邏輯全依賴內(nèi)部的TAP控制器(Test Access Port),其實(shí)就是一個(gè)狀態(tài)機(jī),通過TMS信號(hào)來切換不同的狀態(tài)。 標(biāo)準(zhǔn)的JTAG接口最少需要4個(gè)引腳,即:TCK、TDI、TDO和TMS,在IEEE1149.1標(biāo)準(zhǔn)中,TRST信號(hào)是可選的。下面是每個(gè)信號(hào)的定義和功能:

標(biāo)準(zhǔn)的JTAG接口最少需要4個(gè)引腳,即:TCK、TDI、TDO和TMS,在IEEE1149.1標(biāo)準(zhǔn)中,TRST信號(hào)是可選的。下面是每個(gè)信號(hào)的定義和功能:-

Test Clock Input (TCK)

TCK 為 TAP 的操作提供了一個(gè)獨(dú)立的、基本的時(shí)鐘信號(hào),TAP 的所有操作都是通過這個(gè)時(shí)鐘信號(hào)來驅(qū)動(dòng)的。TCK 在 IEEE 1149.1 標(biāo)準(zhǔn)里是強(qiáng)制要求的。 -

Test Mode Selection Input (TMS)

TMS 信號(hào)用來控制 TAP 狀態(tài)機(jī)的轉(zhuǎn)換。通過 TMS 信號(hào),可以控制 TAP 在不同的狀態(tài)間相互轉(zhuǎn)換。TMS 信號(hào)在 TCK 的上升沿有效。TMS 在 IEEE 1149.1 標(biāo)準(zhǔn)里是強(qiáng)制要求的。 -

Test Data Input (TDI)

TDI 是數(shù)據(jù)輸入的接口。所有要輸入到特定寄存器的數(shù)據(jù)都是通過 TDI 接口一位一位串行輸入的(由 TCK 驅(qū)動(dòng))。TDI 在 IEEE 1149.1 標(biāo)準(zhǔn)里是強(qiáng)制要求的。 -

Test Data Output (TDO)

TDO 是數(shù)據(jù)輸出的接口。所有要從特定的寄存器中輸出的數(shù)據(jù)都是通過 TDO 接口一位一位串行輸出的(由 TCK 驅(qū)動(dòng))。TDO 在 IEEE 1149.1 標(biāo)準(zhǔn)里是強(qiáng)制要求的。 -

Test Reset Input (TRST)

TRST可以用來對(duì)TAP Controller進(jìn)行復(fù)位(初始化)。不過這個(gè)信號(hào)接口在IEEE 1149.1標(biāo)準(zhǔn)里是可選的,并不是強(qiáng)制要求的。因?yàn)橥ㄟ^ TMS 也可以對(duì) TAP Controller 進(jìn)行復(fù)位(初始化)。

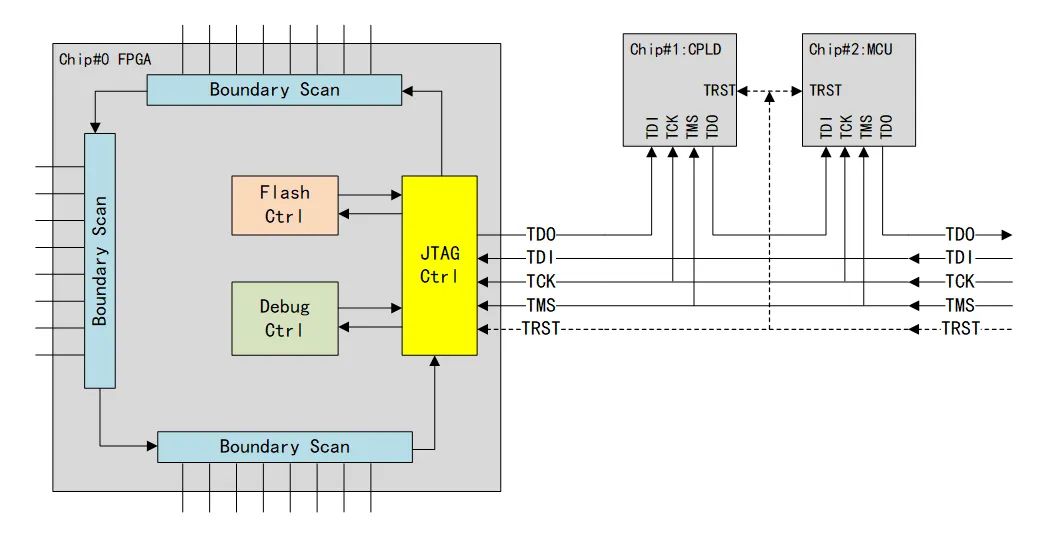

以下是JTAG接口的使用示意:

以下是JTAG接口的使用示意: 每個(gè)管腳都有一個(gè)邊界掃描寄存器單元,在時(shí)鐘的驅(qū)動(dòng)下,每個(gè)管腳的信號(hào)在寄存器單元之間依次流動(dòng),從而實(shí)現(xiàn)每個(gè)管腳狀態(tài)的控制和讀取。

每個(gè)管腳都有一個(gè)邊界掃描寄存器單元,在時(shí)鐘的驅(qū)動(dòng)下,每個(gè)管腳的信號(hào)在寄存器單元之間依次流動(dòng),從而實(shí)現(xiàn)每個(gè)管腳狀態(tài)的控制和讀取。3. 邊界掃描相關(guān)的軟硬件

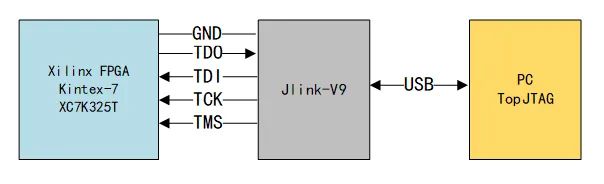

理論上只要支持JTAG協(xié)議的調(diào)試器、下載器,都可以用來進(jìn)行邊界掃描測(cè)試,不過可能需要開發(fā)相對(duì)應(yīng)的上位機(jī)軟件。本文介紹常見的兩款邊界掃描測(cè)試方案。-

JLink + TopJTAG Probe

-

X-JTAG

4. 學(xué)習(xí)資料

一位國外小哥在YouTube發(fā)布的視頻:EEVblog#449-什么是JTAG以及邊界掃描,B站有人搬運(yùn)了,地址是:-

https://www.bilibili.com/video/BV1TT4y1e7HU

-

http://www.micetek.com.cn/technic/jtag.pdf

-

https://fiona.dmcs.pl/~rkielbik/nid/JTAG_IEEE-Std-1149.1-2001.pdf

5. 總結(jié)

對(duì)了,開頭介紹的那款板卡,我使用邊界掃描獲取到的管腳定義如下:#################################################################### #Copyright(C),2010-2023,https://blog.csdn.net/whik1194 #ModuleName:top.xdc #Date:2023-03-04 #Time:2300 #Author:whik1194 #Function:Pinconstraint #Version:v1.0 #Version|Modify #---------------------------------- #v1.0firstversion #################################################################### set_propertyPACKAGE_PINAA10[get_portsgclk_p] set_propertyPACKAGE_PIND9[get_portsgreset] set_propertyPACKAGE_PIND8[get_portskey] set_propertyPACKAGE_PING20[get_portsled1] set_propertyPACKAGE_PINH19[get_portsled2] set_propertyPACKAGE_PINE20[get_portsled3] set_propertyPACKAGE_PINF19[get_portsled4] set_propertyPACKAGE_PINF8[get_portsuart_rxd] set_propertyPACKAGE_PINF9[get_portsuart_txd] set_propertyPACKAGE_PING14[get_portscan_rx] set_propertyPACKAGE_PINH14[get_portscan_tx] set_propertyIOSTANDARDDIFF_SSTL12[get_portsgclk_p] set_propertyIOSTANDARDDIFF_SSTL12[get_portsgclk_n] set_propertyIOSTANDARDLVCMOS33[get_portsgreset] set_propertyIOSTANDARDLVCMOS25[get_portsled1] set_propertyIOSTANDARDLVCMOS25[get_portsled2] set_propertyIOSTANDARDLVCMOS25[get_portsled3] set_propertyIOSTANDARDLVCMOS25[get_portsled4] set_propertyIOSTANDARDLVCMOS33[get_portskey] set_propertyIOSTANDARDLVCMOS33[get_portsuart_rxd] set_propertyIOSTANDARDLVCMOS33[get_portsuart_txd] set_propertyIOSTANDARDLVCMOS33[get_portscan_rx] set_propertyIOSTANDARDLVCMOS33[get_portscan_tx] #QSPI set_propertyBITSTREAM.GENERAL.COMPRESSTRUE[current_design] set_propertyBITSTREAM.CONFIG.CONFIGRATE50[current_design] set_propertyBITSTREAM.CONFIG.SPI_BUSWIDTH4[current_design]

-

JTAG

+關(guān)注

關(guān)注

6文章

401瀏覽量

72114 -

焊接

+關(guān)注

關(guān)注

38文章

3292瀏覽量

60386 -

轉(zhuǎn)換芯片

+關(guān)注

關(guān)注

0文章

75瀏覽量

11478

原文標(biāo)題:強(qiáng)大的JTAG邊界掃描1-基本原理

文章出處:【微信號(hào):mcu149,微信公眾號(hào):電子電路開發(fā)學(xué)習(xí)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

什么是邊界掃描?JTAG邊界掃描測(cè)試方案介紹

邊界掃描測(cè)試技術(shù)簡介及原理

JTAG的基本原理(共31頁pdf課件下載)

JTAG的基本原理與測(cè)試總結(jié)

關(guān)于 RK3568 JTAG 邊界掃描的問題

ARM JTAG調(diào)試的基本原理

JTAG邊界掃描技術(shù)設(shè)計(jì)方案

基于JTAG邊界掃描方式的重構(gòu)控制器的設(shè)計(jì)

Cyclone_IV器件的JTAG邊界掃描測(cè)試

邊界掃描測(cè)試的基本原理及其測(cè)試系統(tǒng)的設(shè)計(jì)

JTAG(四) 邊界掃描測(cè)試技術(shù)

邊界掃描測(cè)試軟件XJTAG和TopJTAG介紹

基于Xilinx FPGA的邊界掃描應(yīng)用

強(qiáng)大的JTAG邊界掃描1-基本原理

強(qiáng)大的JTAG邊界掃描1-基本原理

評(píng)論