早期,電路設計工程師經常需要手工標注相關的信息在原理圖上用于提醒版圖工程師相關器件的版圖設計要求,比如匹配,對稱等。其實VSE早就引入了設計約束功能,并且通過layout 同步schematic的約束,還可以快速的檢查約束規則是否匹配。

有了這項功能后,就不需要和牛逼哄哄的版圖工程師費口水了。

主要的方法如下

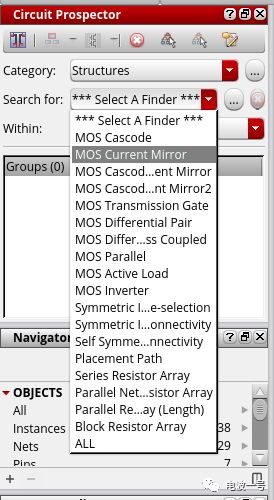

1, windows-assistant-> Circuit Prospect可以調用出電路模塊的匹配功能,快速查找出常用的需要約束的地方比如Power Nets,current mirror以及differential pair這些模塊。主要分為Structure, Devices, Nets, Pins, inst Terms, 比較常用的還是Structure和Device,雖然經常匹配不到。

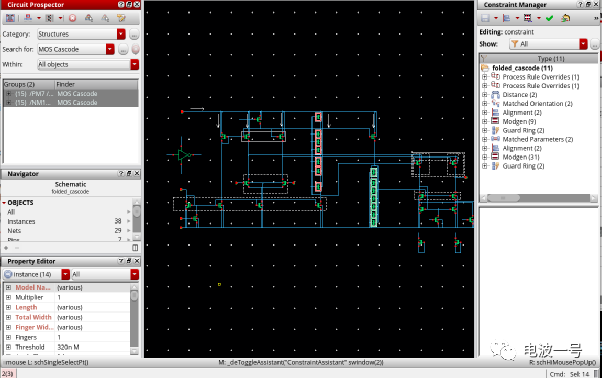

2, Windows--> assistant -->Constraint Manager

可以調出相應的約束菜單,支持的約束類型可以分為三大類,Electrical, Placement 和Routing。比如常用器件參數匹配就在Electrical中的Parameter Match

點擊設置好的約束,可以高亮原理圖對應的管子。

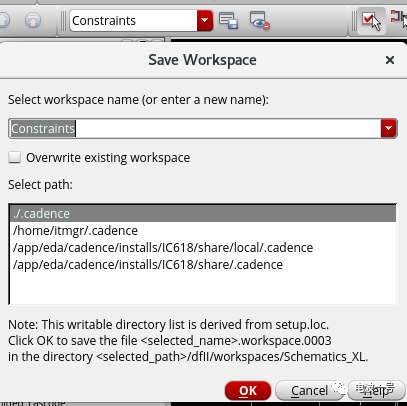

正常開啟之后設計的界面如下,可以通過windows-workspace-->save workspace,方便下次快速調用。

比較常見的約束方法有,

1, VDD/VSS power net用Process Rule overide 使用更粗的線寬, 比如4X,6X minimum width

2,current-mirror 用modGen 自動生成。

3, 等等等

Lanuch layout -XL后,原理圖的constraint 可以自動同步過來,也可以手動將更新部分同步。Check Constraint開了之后,版圖中是否違法constraint可以直接發現。

總體來說,Constraint Manager是一個相當能減少溝通成本的好工具,也是模擬設計向數字設計方法學習的一個體現,不知道貴司是否已經在生產中應用。

-

原理圖

+關注

關注

1298文章

6343瀏覽量

233982 -

電路設計

+關注

關注

6673文章

2452瀏覽量

204320 -

Layout

+關注

關注

14文章

404瀏覽量

61762 -

約束

+關注

關注

0文章

82瀏覽量

12729 -

Virtuoso

+關注

關注

4文章

17瀏覽量

25073

發布評論請先 登錄

相關推薦

人工智能中常見的數據標注方法

linux系統中常見注冊函數的使用方法

分頻器的相位問題_音響中常見的相位問題及解決方法

WillSemi采用的Cadence Virtuoso定制IC設計平臺有哪些優點?

PCB阻焊工序中常見品質問題及解決方法

Virtuoso軟件中常見的約束方法

Virtuoso軟件中常見的約束方法

評論