今天是畫師本人第一次和各位大俠見面,執筆繪畫FPGA江湖,本人寫了篇關于FPGA的偽隨機數發生器學習筆記,這里分享給大家,僅供參考。

基于FPGA的偽隨機數發生器

(附代碼)

1、概念

隨機數是專門的隨機試驗的結果,產生隨機數有多種不同的方法。這些方法被稱為隨機數生成器。隨機數最重要的特性是它在產生時后面的那個數與前面的那個數毫無關系。隨機數分為三類,分別是偽隨機數、密碼學安全的偽隨機數以及真隨機數。

本次設計為基于FPGA生成的偽隨機數發生器,什么是偽隨機數呢?統計學偽隨機性指的是在給定的隨機比特流樣本中,1的數量大致等于0的數量,同理,“10”“01”“00”“11”四者數量大致相等。類似的標準被稱為統計學隨機性。滿足這類要求的數字在人類“一眼看上去”是隨機的。

在實際應用中往往使用偽隨機數就足夠了。這些數列是“似乎”隨機的數,實際上它們是通過一個固定的、可以重復的計算方法產生的。計算機或計算器產生的隨機數有很長的周期性。它們不真正地隨機,因為它們實際上是可以計算出來的,但是它們具有類似于隨機數的統計特征。這樣的發生器叫做偽隨機數發生器。

2、設計原理

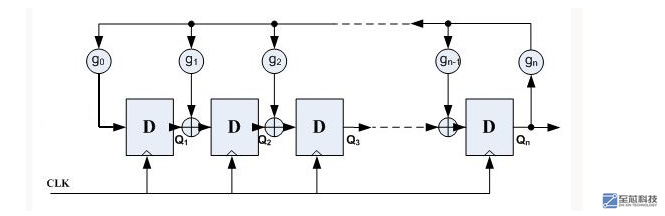

本次設計采用線性反饋移位寄存器(Linear Feedback Shift Register, LFSR)來實現偽隨機數發生器。線性反饋移位寄存器是指,給定前一狀態的輸出,將該輸出的線性函數再用作輸入的移位寄存器。異或運算是最常見的單比特線性函數:對寄存器的某些位進行異或操作后作為輸入,再對寄存器中的各比特進行整體移位。

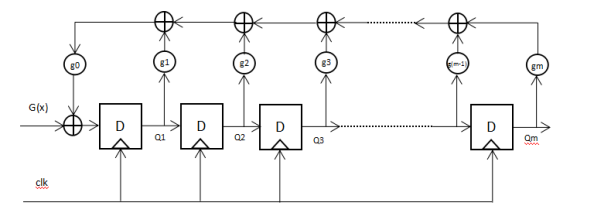

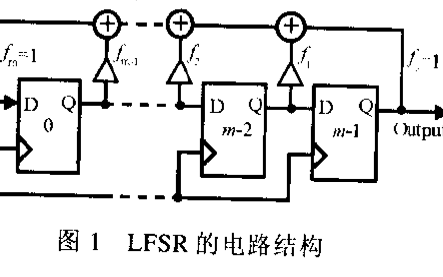

線性反饋移位寄存器通常由動態或靜態主從型觸發器構成。反饋回路由異或門構成。其特性通常由一個特征多項式表征。LFSR結構如下圖所示:

圖1 LFSR結構示意圖

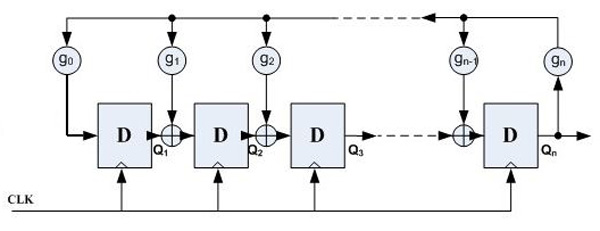

對應的特征多項式為:

Gm為多項式的系數,而多項式系數只能為1或0。

利用LFSR生成偽隨機數,需要給它一個隨機種子(seed),由于它是由N個觸發器和異或門組成,所以種子不能給全0,如果給的全0,將會陷入0的死循環一直出不來,就得不到我們想要的偽隨機數,在設計時,我們可以給一個任意不為0的數。

基于以上原理,我們使用本原多項式x^32+x^7+x^5+x^3+x^2+x+1來構造最大周期的LFSR。

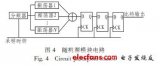

3、架構設計

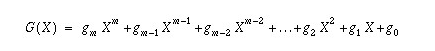

設計架構如下圖:

將輸入時鐘命名為clk,復位信號命名為rst_n,輸入有效信號命名為ivalid,輸入的隨機種子命名為seed[31:0],生成的隨機數命名為data[31:0]。

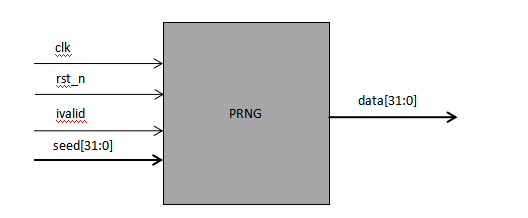

4、Verilog代碼實現

代碼中data <= seed部分也可以不需要,不用輸入有效信號以及隨機種子,直接初始化為非零值也可。如直接初始化為非零值,則仿真代碼只需進行復位即可。

設計實現代碼如下:

5、仿真測試結果

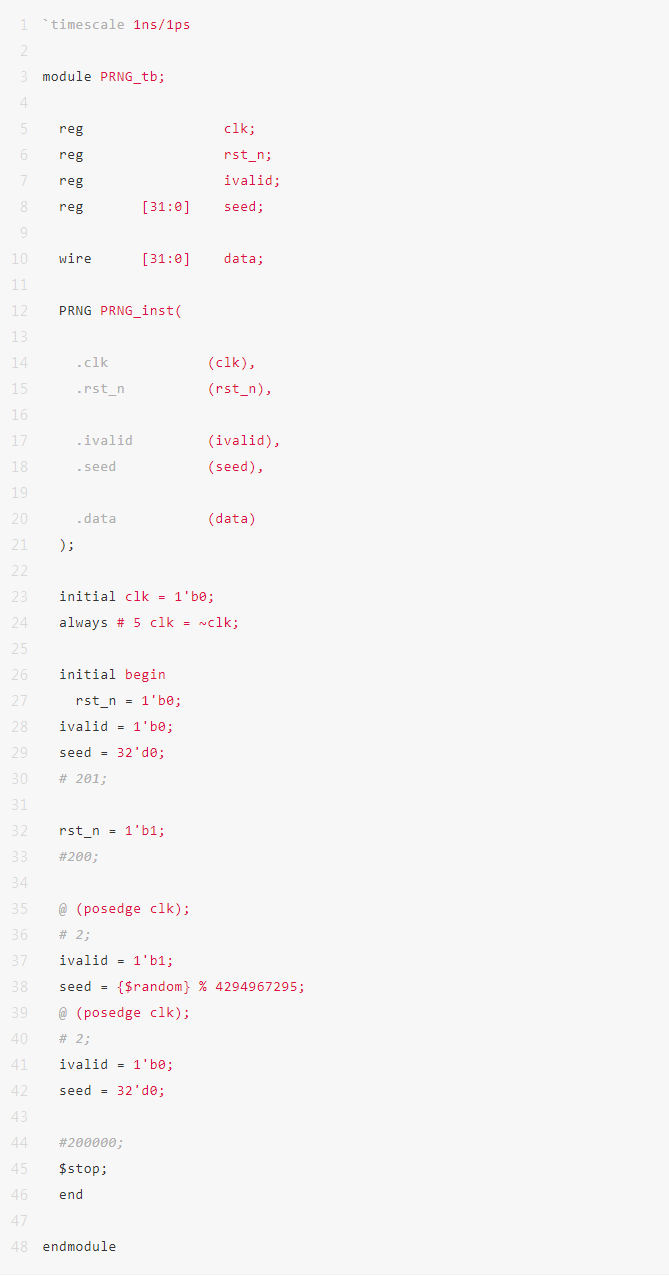

仿真代碼如下:

本次仿真采用100M時鐘進行,輸入種子為非零隨機數。

6、總結

以上是經過學習,集合了各家所長得到的結果。由于想做一個32位的偽隨機數發生器,在網上找了各種資料,并沒有找到有規定的標準多項式,于是隨意定了一個。在實際運用當中,如果有標準的多項式系數,可能得到了一個偽隨機數,就可以根據已知的特征式得出后面的結果,安全性也就大大降低了。

審核編輯:彭菁

-

FPGA

+關注

關注

1629文章

21729瀏覽量

602993 -

計算機

+關注

關注

19文章

7488瀏覽量

87849 -

發生器

+關注

關注

4文章

1368瀏覽量

61677 -

函數

+關注

關注

3文章

4327瀏覽量

62571

原文標題:【學習教程】基于FPGA的偽隨機數發生器(附代碼)

文章出處:【微信號:gh_9b9470648b3c,微信公眾號:電子發燒友論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【assingle分享】labview隨機數發生器

【總結】LabVIEW隨機數發生器

怎么設計基于USB和FPGA的隨機數發生器驗證平臺?

偽隨機數發生器的FPGA實現與研究

基于FPGA的真隨機數發生器設計

利用FPGA的自身特性實現隨機數發生器

補充: FPGA產生基于LFSR的偽隨機數

如何使用FPGA實現偽隨機數發生器

FPGA產生基于LFSR的偽隨機數概念

FPGA的偽隨機數發生器學習介紹

FPGA的偽隨機數發生器學習介紹

評論