英諾達發布了自主研發的靜態驗證EDA工具EnAltius?昂屹? DFT Checker,該工具可以在設計的早期階段發現與DFT相關的問題或設計缺陷。

(2023年9月13日,四川成都)英諾達(成都)電子科技有限公司發布了自主研發的靜態驗證EDA工具EnAltius?昂屹? DFT Checker,該工具可以在設計的早期階段發現與DFT相關的問題或設計缺陷。

隨著芯片規模和復雜度的提升,芯片各種邏輯和電氣功能驗證的要求越來越高,多種RTL編碼風格、以及存在于電路設計中的結構性和功能性問題更容易成為設計上的缺陷,導致設計不斷修改,甚至造成流片失敗的風險。此外,設計重用性和IP的高集成度對模塊設計在正確性和一致性方面提出了更嚴格的要求,以提高IP集成的可靠性和成功率。

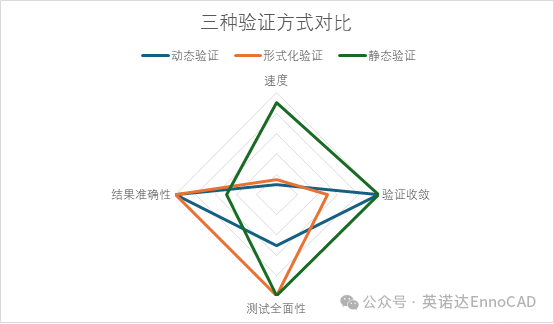

上述芯片設計的挑戰可以通過傳統的基于仿真的動態驗證工具和技術得到一定程度的解決,然而,現代的SoC設計需要強大的靜態驗證技術作為補充,以縮短設計時間并提高首次流片的成功率。更為難得的是這種技術可在設計的早期階段發現設計缺陷,從而避免設計團隊大量無效時間和精力的投入。

英諾達是國內第一家專注于開發以IC設計代碼分析和規則檢查為基礎的靜態驗證工具的EDA企業,可提供全面的用于分析、查錯和修復的EDA解決方案,可在設計的早期階段(RTL階段或邏輯綜合階段)對結構性、功能性和電氣性等電路問題進行深入的分析。繼EnFortius?凝鋒?系列兩款低功耗靜態驗證工具發布之后,英諾達此次發布的昂屹?DFT Checker靜態檢查工具,可以對RTL或網表設計進行結構性和功能性分析,在設計早期階段提高IC設計的質量。

DFT(可測試性設計,Design-For-Test)是設計收斂的關鍵一環,通過在設計上增加邏輯,使芯片的測試更高效和更容易,此外,還可以提高良品率、降低成本。因此,確保芯片設計符合DFT設計規則,提高測試覆蓋率是所有設計團隊都要面對和解決的問題。當前,DFT測試覆蓋率通常要求達到99%以上,因為任何漏掉的測試向量都可能導致芯片在實際應用中出現故障。而在設計后期增加DFT邏輯會對性能、功耗和面積產生較大影響,會導致設計迭代甚至重新設計。所以,在設計的早期階段提高代碼的質量至關重要。

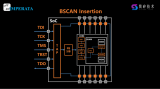

昂屹?DFT Checker基于英諾達首款EDA工具凝鋒? LPC的底層架構和先進算法,該款工具可提供早期RTL可測試性分析功能,同時也支持傳統的基于網表的流程。除了對可測試性問題的早期分析之外,該工具還可以縮短完成DFT設計的時間,并確保設計在可測試性部分達到交付標準。

該款工具涵蓋了全面的結構、功能和電路規則檢查,可有效提高測試覆蓋率。基于先進的SoC設計規則和方法學,昂屹?DFT Checker可驗證芯片在不同模式下所有連線的正確性、完整性和集成性。此外,為了提高設計效率,該工具提供以目標為導向的報錯信息,幫助設計師快速過濾、定位和調試設計上的問題。對此,益昂半導體副總范學鋒表示:“DFT設計是IC設計不可缺少的一環,英諾達DFT Checker可以幫助設計師在設計的早期階段發現并更正對DFT不友好的設計,使得后期的DFT綜合與實現更快速收斂,從而提高設計效率。”

英諾達副總經理熊文表示:“在IC設計早期應用靜態驗證工具可以幫助IC工程師進行高效的設計驗證及關鍵性的優化,英諾達已發布了兩款低功耗領域的靜態驗證工具,在超大規模電路設計上可以快速完成低功耗設計的檢查及功耗的分析與驗證。除低功耗設計領域之外,靜態驗證可應用的領域還有很多,昂屹?DFT Checker就是我們的又一突破創新產品。英諾達將把握這一優勢,不斷開拓,繼續為國產EDA靜態驗證工具補齊短板,為IC工程師的設計效率和芯片良率保駕護航。”

審核編輯:劉清

-

LPC

+關注

關注

8文章

136瀏覽量

77623 -

IC設計

+關注

關注

38文章

1295瀏覽量

103918 -

EDA工具

+關注

關注

4文章

267瀏覽量

31785 -

SoC設計

+關注

關注

1文章

148瀏覽量

18774 -

DFT

+關注

關注

2文章

231瀏覽量

22712

原文標題:英諾達發布DFT靜態驗證工具,提高IC設計質量及可靠性

文章出處:【微信號:gh_387c27f737c1,微信公眾號:英諾達EnnoCAD】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DFT與離散時間傅里葉變換的關系 DFT在無線通信中的應用

DFT在圖像處理中的作用 DFT在音頻信號處理中的應用

DFT在信號處理中的應用 DFT與FFT的區別

英諾達受邀參加IIC Shenzhen 2024

英諾達低功耗設計研討會圓滿結束

Lint靜態驗證工具如何助力IC設計

英飛凌對英諾賽科提起追加訴訟,并向美國國際貿易委員會起訴

英諾賽科營業收入實現跨越式增長,持續推動技術創新

英飛凌起訴英諾賽科專利侵權

英諾達發布DFT靜態驗證工具

英諾達發布DFT靜態驗證工具

評論