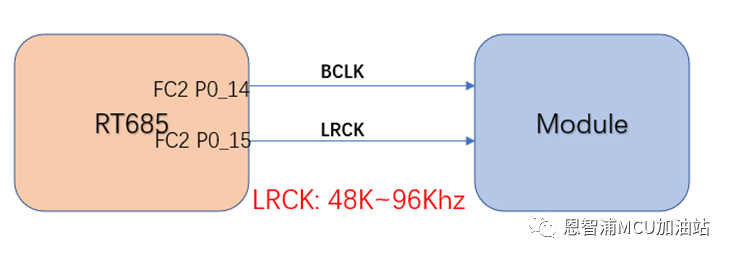

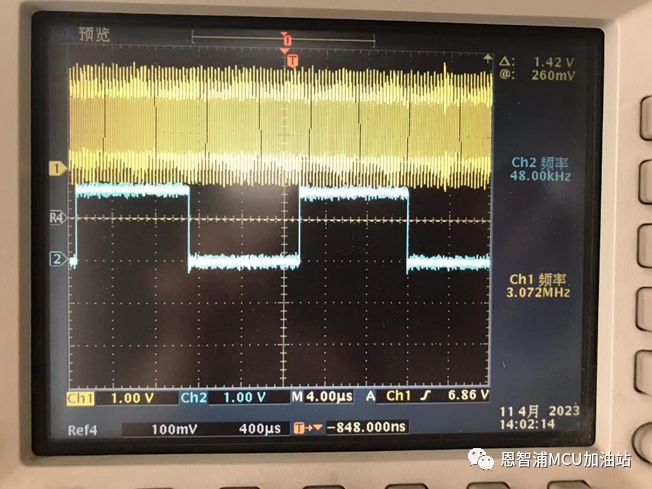

48Khz 采樣率,32bit, 2通道, BCLK輸出3.072Mhz。

測試發現現象很奇怪,如果BCLK連接的模塊阻抗改變,會導致正常應該輸出48K的LRCK(WS)頻率會變動,有時候變成96Khz,客戶的模塊是專用的ASIC。

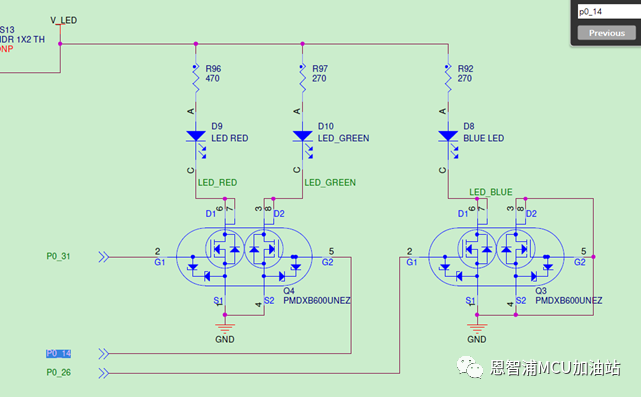

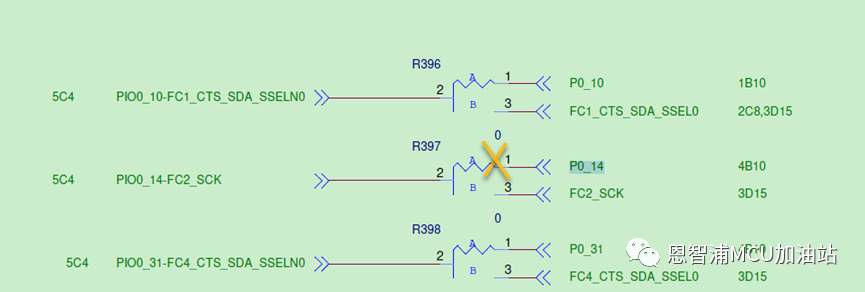

客戶反應,這個問題同樣可以在NXP MIMXRT685-AUD-EVK板子上復現,因為AUD-EVK FC2P0_14連接到了外部LED的驅動電路:

如果是官方的代碼配置,不會復現問題,如果是使用客戶的代碼,能夠復現問題。

如果斷開R397 1_2的電阻,問題就不會復現,連接之后就會復現。

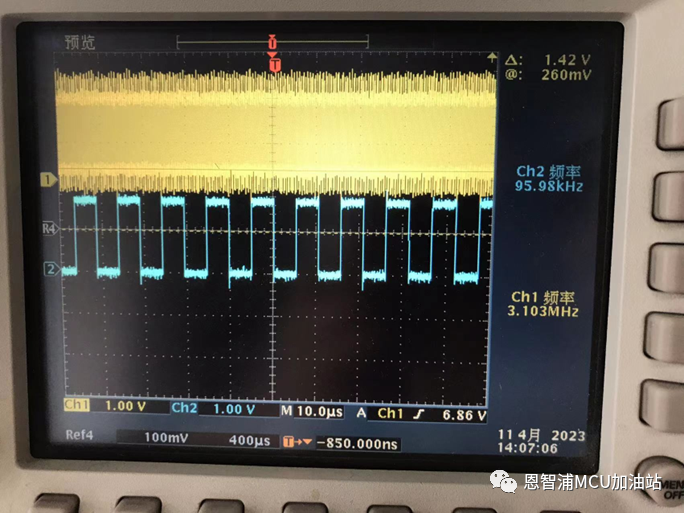

所謂復現:測試P0_15 LRCK采樣率從期望的48Khz變成了96Khz:

所謂不復現:測試P0_15 LRCK采樣率就是期望的48Khz:

從I2S的構架上講,不應該出現具體I2S IP的配置因為外部的驅動情況導致不同的輸出頻率,而且官方的代碼直接修改接口和引腳也不會出現,那么問題究竟出在哪里呢?

問題分析與解決方案經過查看官方SDK的配置和客戶提供的代碼,發現差別很簡單,在于pinmux.c對于P0_14, P0_15的配置,客戶復現問題的配置如下:

const uint32_t port0_pin14_config = (/* Pin is configured as FC2_SCK */

IOPCTL_PIO_FUNC1 |

/* Disable pull-up / pull-down function */

IOPCTL_PIO_PUPD_DI |

/* Enable pull-down function */

IOPCTL_PIO_PULLDOWN_EN |

/* Enables input buffer function */

IOPCTL_PIO_INBUF_EN |

/* Normal mode */

IOPCTL_PIO_SLEW_RATE_NORMAL |

/* Normal drive */

IOPCTL_PIO_FULLDRIVE_DI |

/* Analog mux is disabled */

IOPCTL_PIO_ANAMUX_DI |

/* Pseudo Output Drain is disabled */

IOPCTL_PIO_PSEDRAIN_DI |

/* Input function is not inverted */

IOPCTL_PIO_INV_DI);

/* PORT0 PIN14 (coords: A3) is configured as FC2_SCK */

IOPCTL_PinMuxSet(IOPCTL, 0U, 14U, port0_pin14_config);

const uint32_t port0_pin15_config = (/* Pin is configured as FC2_TXD_SCL_MISO_WS */

IOPCTL_PIO_FUNC1 |

/* Disable pull-up / pull-down function */

IOPCTL_PIO_PUPD_DI |

/* Enable pull-down function */

IOPCTL_PIO_PULLDOWN_EN |

/* Enables input buffer function */

IOPCTL_PIO_INBUF_EN |

/* Normal mode */

IOPCTL_PIO_SLEW_RATE_NORMAL |

/* Normal drive */

IOPCTL_PIO_FULLDRIVE_DI |

/* Analog mux is disabled */

IOPCTL_PIO_ANAMUX_DI |

/* Pseudo Output Drain is disabled */

IOPCTL_PIO_PSEDRAIN_DI |

/* Input function is not inverted */

IOPCTL_PIO_INV_DI);

/* PORT0 PIN15 (coords: A5) is configured as FC2_TXD_SCL_MISO_WS */

IOPCTL_PinMuxSet(IOPCTL, 0U, 15U, port0_pin15_config);

官方不復現問題的配置如下:

const uint32_t port0_pin14_config = (/* Pin is configured as FC2_SCK */

IOPCTL_PIO_FUNC1 |

/* Disable pull-up / pull-down function */

IOPCTL_PIO_PUPD_DI |

/* Enable pull-down function */

IOPCTL_PIO_PULLDOWN_EN |

/* Enables input buffer function */

IOPCTL_PIO_INBUF_EN |

/* Normal mode */

IOPCTL_PIO_SLEW_RATE_NORMAL |

/* Normal drive */

IOPCTL_PIO_FULLDRIVE_EN |

/* Analog mux is disabled */

IOPCTL_PIO_ANAMUX_DI |

/* Pseudo Output Drain is disabled */

IOPCTL_PIO_PSEDRAIN_DI |

/* Input function is not inverted */

IOPCTL_PIO_INV_DI);

/* PORT0 PIN14 (coords: A3) is configured as FC2_SCK */

IOPCTL_PinMuxSet(IOPCTL, 0U, 14U, port0_pin14_config);

const uint32_t port0_pin15_config = (/* Pin is configured as FC2_TXD_SCL_MISO_WS */

IOPCTL_PIO_FUNC1 |

/* Disable pull-up / pull-down function */

IOPCTL_PIO_PUPD_DI |

/* Enable pull-down function */

IOPCTL_PIO_PULLDOWN_EN |

/* Enables input buffer function */

IOPCTL_PIO_INBUF_EN |

/* Normal mode */

IOPCTL_PIO_SLEW_RATE_NORMAL |

/* Normal drive */

IOPCTL_PIO_FULLDRIVE_EN |

/* Analog mux is disabled */

IOPCTL_PIO_ANAMUX_DI |

/* Pseudo Output Drain is disabled */

IOPCTL_PIO_PSEDRAIN_DI |

/* Input function is not inverted */

IOPCTL_PIO_INV_DI);

/* PORT0 PIN15 (coords: A5) is configured as FC2_TXD_SCL_MISO_WS */

IOPCTL_PinMuxSet(IOPCTL, 0U, 15U, port0_pin15_config);

實際上,只要BCLK P0_14的引腳配置為FULL drive即可。

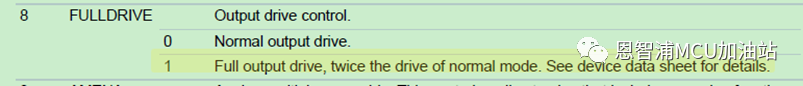

可以看到,如果配置為Full output driver,驅動能力是normal輸出的兩倍。所以,問題出在BCLK的引腳驅動能力這塊。

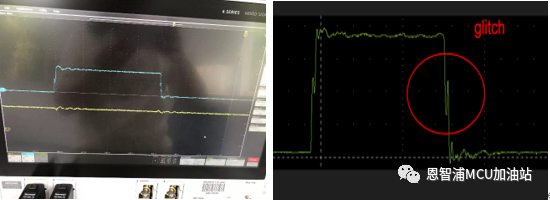

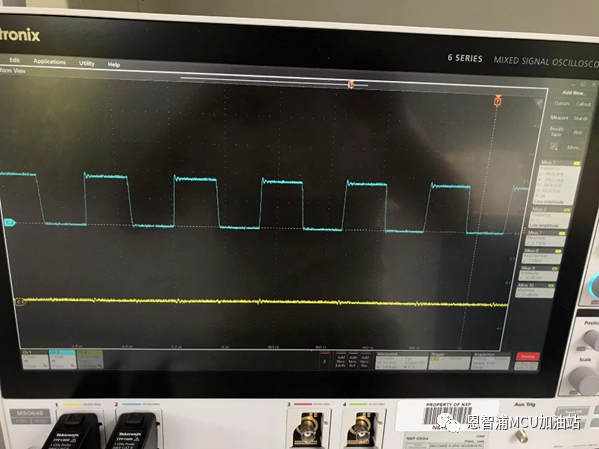

然而,推薦客戶改變驅動能力的方式,縱然可以輸出正確的48Khz采樣率波形,客戶并不接受,認為高驅動能力也代表著功耗的加大,而他們的產品是對功耗要求極高的,必須要在普通驅動能力下解決問題。所以進一步分析波形,通過使用高采樣率的示波器20Gsa/s,2G探頭抓取出問題時候的BCLK,可以發現有一些毛刺:

通過內部的溝通,也認為這個BCLK毛刺是導致問題的原因。這里需要注意的是,有些示波器,如果采樣率低可能抓不到這個毛刺,還有些探頭,阻抗比較小,導致探頭加上到BCLK,直接問題消失的情況,所以建議使用高阻抗探頭,比如1M歐,1G采樣率以上的探頭即可抓到。

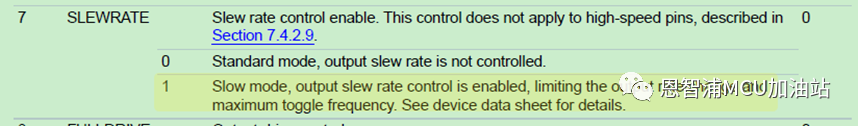

由于客戶不接受驅動能力的改變,所以這里還可以考慮改變斜率,讓上升下降變緩,濾掉毛刺區域,改變配置如下:

const uint32_t port0_pin14_config = (/* Pin is configured as FC2_SCK */

IOPCTL_PIO_FUNC1 |

/* Disable pull-up / pull-down function */

IOPCTL_PIO_PUPD_DI |

/* Enable pull-down function */

IOPCTL_PIO_PULLDOWN_EN |

/* Enables input buffer function */

IOPCTL_PIO_INBUF_EN |

/* Normal mode */

IOPCTL_PIO_SLEW_RATE_SLEW|//0X80|// IOPCTL_PIO_SLEW_RATE_NORMAL |

/* Normal drive */

IOPCTL_PIO_FULLDRIVE_DI |

/* Analog mux is disabled */

IOPCTL_PIO_ANAMUX_DI |

/* Pseudo Output Drain is disabled */

IOPCTL_PIO_PSEDRAIN_DI |

/* Input function is not inverted */

IOPCTL_PIO_INV_DI);

/* PORT0 PIN14 (coords: A3) is configured as FC2_SCK */

IOPCTL_PinMuxSet(IOPCTL, 0U, 14U, port0_pin14_config);

const uint32_t port0_pin15_config = (/* Pin is configured as FC2_TXD_SCL_MISO_WS */

IOPCTL_PIO_FUNC1 |

/* Disable pull-up / pull-down function */

IOPCTL_PIO_PUPD_DI |

/* Enable pull-down function */

IOPCTL_PIO_PULLDOWN_EN |

/* Enables input buffer function */

IOPCTL_PIO_INBUF_EN |

/* Normal mode */

IOPCTL_PIO_SLEW_RATE_NORMAL |

/* Normal drive */

IOPCTL_PIO_FULLDRIVE_DI |

/* Analog mux is disabled */

IOPCTL_PIO_ANAMUX_DI |

/* Pseudo Output Drain is disabled */

IOPCTL_PIO_PSEDRAIN_DI |

/* Input function is not inverted */

IOPCTL_PIO_INV_DI);

/* PORT0 PIN15 (coords: A5) is configured as FC2_TXD_SCL_MISO_WS */

IOPCTL_PinMuxSet(IOPCTL, 0U, 15U, port0_pin15_config);

測試結果如下:

測試結果如下:

可以看到波形很光滑,毛刺消失,輸出也是穩定的48Khz,滿足客戶不改變驅動能力的要求。

小結

在使用i.MX RT600 FC2做I2S的時候,為了BCLK不受外部電路影響,從而影響到WS的波形頻率,建議引腳配置以下二選一:

1.使用Full output drive,提高驅動能力2.使用慢slewrate,濾掉BCLK上升下降小毛刺

最后,特別感謝NXP 蘇州SE團隊 James Fan 在該解決方案上提供的大力支持!作者:周晶晶

-

mcu

+關注

關注

146文章

17123瀏覽量

350986 -

恩智浦

+關注

關注

14文章

5857瀏覽量

107318 -

WS

+關注

關注

0文章

3瀏覽量

9940 -

i.MX

+關注

關注

1文章

47瀏覽量

35607 -

I2S

+關注

關注

1文章

64瀏覽量

41902

原文標題:i.MX RT600 BCLK受干擾影響WS頻率解決方案

文章出處:【微信號:NXP_SMART_HARDWARE,微信公眾號:恩智浦MCU加油站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

NXP專為邊緣AI打造的i.MX RT700跨界MCU到底強在哪?

NXP推出基于i.MX RT106F本地人臉識別解決方案

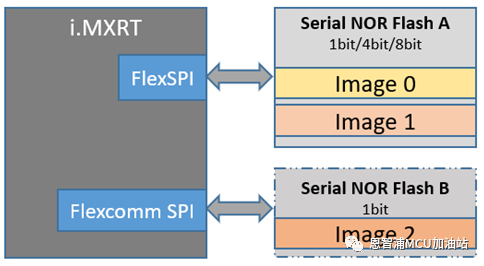

i.MX RT500/600應用案例 串行NOR Flash雙程序可交替啟動設計

恩智浦i.MX RT600跨界微控制器在功耗、性能和存儲器方面有顯著特點

i.MX RT開發筆記-08 | i.MX RT1062嵌套中斷向量控制器NVIC(按鍵中斷檢測)

RT-Thread & NXP 發布 i.MX RT 系列 BSP 新框架

i.MX RT600 BCLK受干擾影響WS頻率解決方案

i.MX RT600 BCLK受干擾影響WS頻率解決方案

評論