電源是最容易被忽視的,電源是系統運行的重要組成部分,電源就像“人體的心臟”,為系統的硬件輸送血液(電),要是心臟(電源)運行不正常或供血(電)不足,會導致系統不運行或運行不穩定,在設計之前應該對核心模塊峰值電流表進行知悉,供PCB Layout時評估線寬作用,如表6-1,值得注意的是不能簡單的全部加起來算成SOC的峰值電流,要評估散熱方案,請根據實際場景的工作平均電流進行,表格參數值僅供參考。(文末附《RK3588PCB設計指導白皮書》下載入口)

3588電源的PCB設計主要注意以下幾個方面:

1.1 RK806電源方案的PCB設計

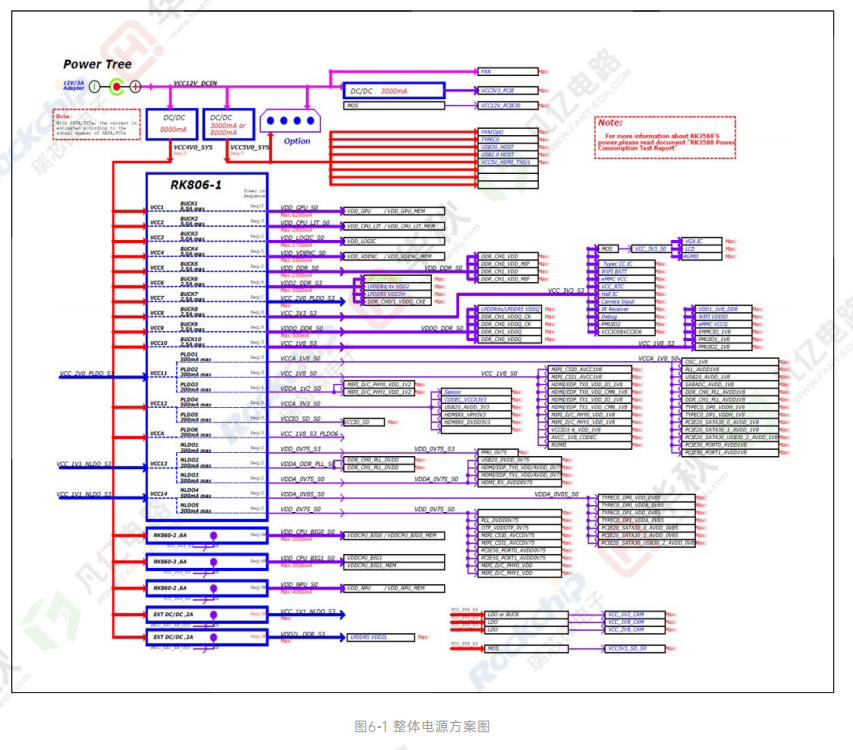

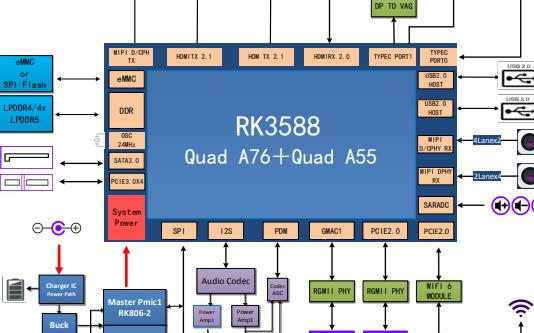

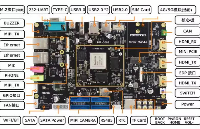

RK3588系統采用PMIC芯片RK806來進行整體供電,如圖6-1所示。整體布局時在滿足結構和特殊器件的布局同時RK806盡量靠近RK3588,如需要考慮散熱設計,可以適當保持間距不要太靠近也不能離的太遠,擺放方向時,盡量優先考慮 RK806的BUCK1、BUCK2、BUCK3、BUCK4這些輸出電流比較大的電源到RK3588的信號流向是順暢的。

1、RK806電源PCB總體要求

① 過孔數量以0.5*0.3mm尺寸的過孔為例,高壓電源單個過孔推薦走0.8A,低壓電源(1V 以下)按0.5A計算,當然也可以通過專業的計算工具進行計算。

② 不建議電源部分器件焊盤及過孔做十字連接處理,應該用鋪銅全覆蓋連接才能更好的散熱和載流。

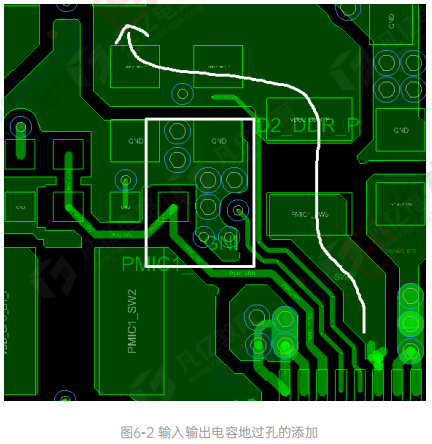

③ 大電流電路比如Buck輸入輸出電容的GND過孔應該要和電源輸入端過孔數量多,如圖6-2所示,這樣才能起到較好的濾波效果(很多客戶容易忽略電容GND端的過孔數量)。

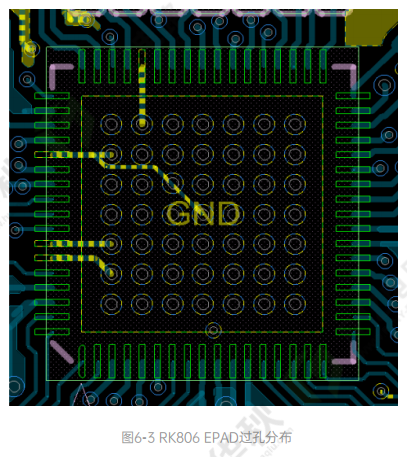

④ RK806的EPAD 接地焊盤要優先保證有足夠的過孔,建議保證5*5個0.5*0.3mm 或是6*6 個0.4*0.2mm的過孔以上,降低接地阻抗和加強熱量傳導;盲埋孔的板子再打一些盲孔輔助降低阻抗,如圖6-3所示。

2、RK806的BUCK13電路PCB要求

① 輸入電容必須離芯片盡可能近,如果輸入電容放在芯片的背面,需保證電容的GND端朝向芯片,這樣讓輸入電容與VCC和GND的連接環路盡可能小。

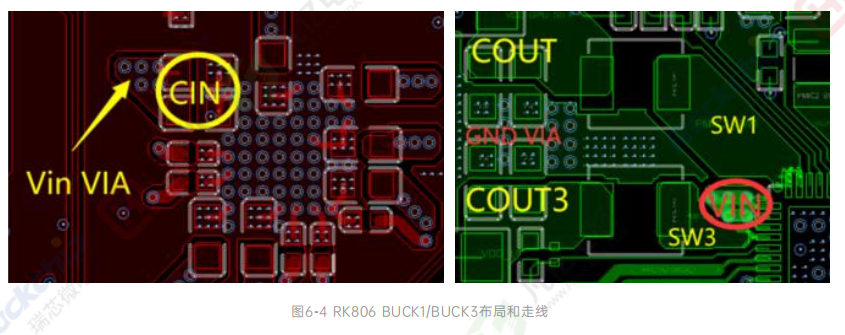

② 應當保證SW的走線出焊盤后盡可能短粗以提高載流能力及電源效率,對于需要打孔的地方,VCC1/3如果合并供電至少需要5 個0.5*0.3mm的過孔,如果分開各自需要3個及以上的0.5*0.3mm的過孔。

③ BUKC1和BUCK3的輸出電容的GND端可以靠在一起共用但至少要15個以上的0.5*0.3mm過孔,如果空間不足可以打小過孔或盲孔補充。

④ BUCKl輸出如果有換層至少保證15個及以上的0.5*0.3mm過孔,同樣的BUCK3要保證12個及以上的0.5*0.3mm 過孔,如圖6-4所示。

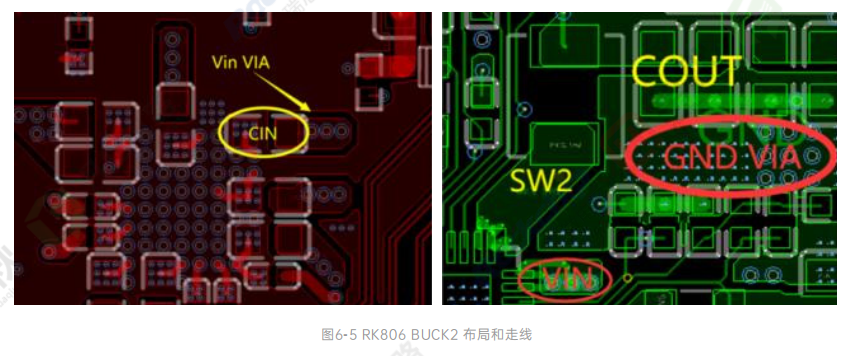

3、RK806的BUCK2電路PCB要求

① 輸入電容必須離芯片盡可能近,如果輸入電容放在芯片的背面,需保證電容的GND端朝向芯片,這樣讓輸入電容與VCC和GND的連接環路盡可能小。

② 應當保證SW的走線出焊盤后盡可能短粗以提高載流能力及電源效率,對于需要打孔的地方,VCC2供電至少需要3個0.5*0.3mm過孔,輸出電容的GND端至少要12個以上的0.5*0.3mm過孔,如果空間不足可以打小過孔或盲孔補充。

③ 輸出如果有換層至少保證12個及以上的0.5*0.3mm過孔,如圖6-5所示。

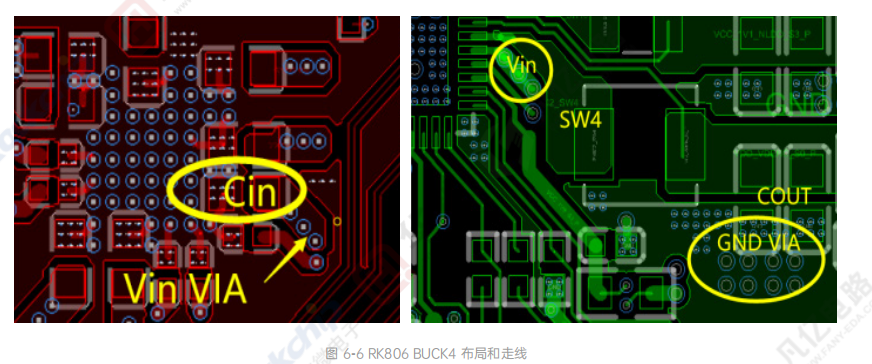

4、RK806的BUCK4電路PCB布局布線要求

① 輸入電容必須離芯片盡可能近,如果輸入電容放在芯片的背面,需保證電容的GND端朝向芯片,這樣讓輸入電容與VCC和GN的連接環路盡可能小。

② 應當保證SW的走線出焊盤后盡可能短粗以提高載流能力及電源效率,對于需要打孔的地方,VCC4供電至少需要3個0.5*0.3mm的過孔,輸出電容的GND端至少要12個以上的 0.5*0.3mm過孔,如果空間不足可以打小過孔或盲孔補充,如圖6-6所示。

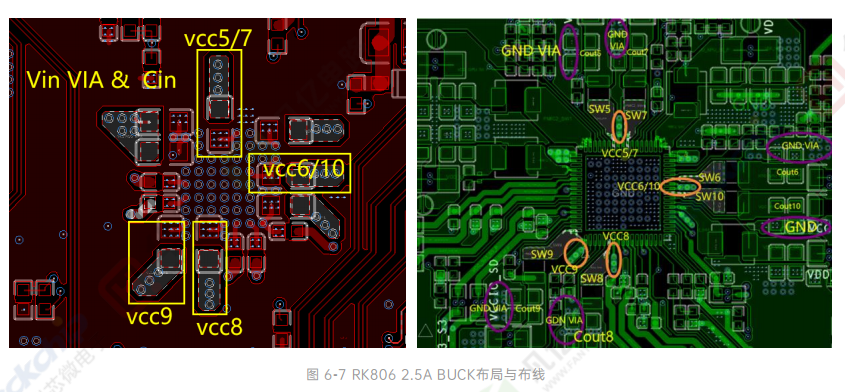

5、RK806的2.5A BUCK電路PCB要求

① 輸入電容必須離芯片盡可能近,如果輸入電容放在芯片的背面,需保證電容的GND端朝向芯片,這樣讓輸入電容與VCC和GND的連接環路盡可能小,如圖6-7所示。

② 應當保證SW的走線出焊盤后盡可能短粗以提高載流能力及電源效率。

③ 對于需要打過孔的地方,VCC5/6/7/10供電至少需要3個0.5*0.3mm的過孔,VCC8/9至少需要2個0.5*0.3mm的過孔,輸出電容的GND端至少要5個及以上的0.5*0.3mm過孔,如果空間不足可以打盲孔補充,如圖6-8所示。

④ 輸出如果要換層至少保證5個及以上的0.5*0.3mm過孔換層。

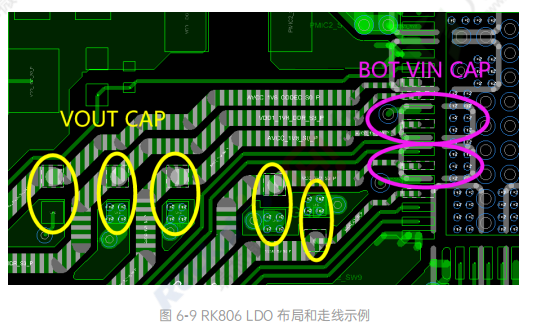

6、RK806 的 LDO電路PCB布局布線要求

① 輸入電容必須離芯片盡可能近,輸入電容與VCC11/12/13/14和GND的連接環路盡可能小。

② 輸出電容必須離芯片盡可能近,輸出電容與PLDO1/2/3/4/5/6及NLDO1/2/3/4/5和GND的連接環路盡可能小。

③ RK806的VCCA電容必須靠近管腳放置,遠離其它干擾源,電容的地焊盤必須良好接地,即VCCA電容地焊盤和RK806 EPAD之間路徑必須保證最短,不得被其他信號分割。

④ RK806的Pin 67(RESETB)的100nF電容必須靠近RK806管腳,提高芯片抗干擾能力。

⑤ RK806 LDO部分管腳不建議覆銅,所有管腳通過走線方式和外面連接,焊盤內走線寬度不得超過焊盤寬度,防止制板后,焊盤變大貼片容易連錫。

⑥ 走線粗線一般按1mm寬度走1A來設計,大電流輸出的LDO根據后端實際供電需求,走線在從芯片引出后應盡快變粗到需求大小,要特別關注低壓大電流NLDO的走線長度及損耗,以滿足目標芯片的供電電壓及紋波需求。如圖6-9所示。

1.2 分立電源的DC-DCPCB設計

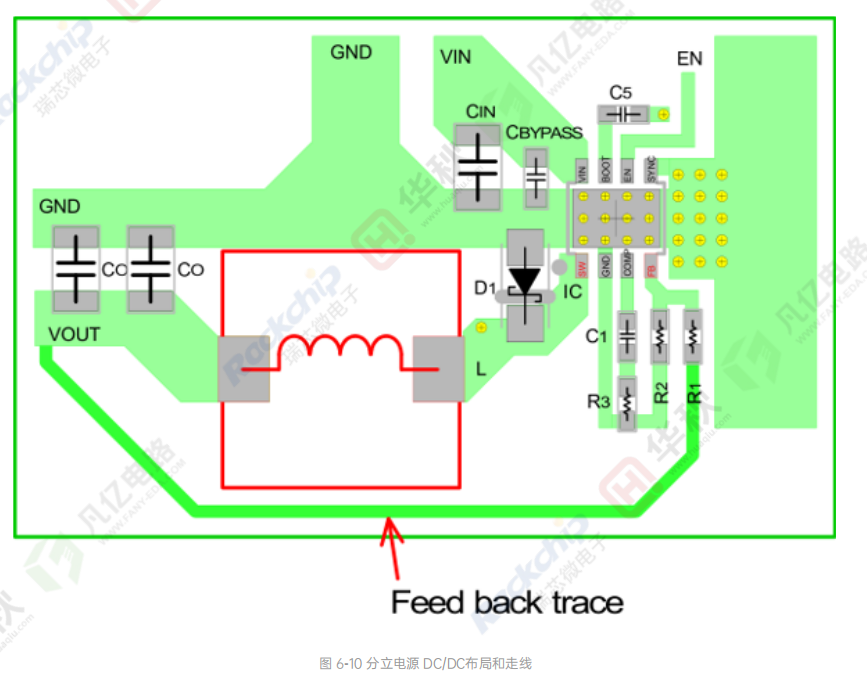

輸入電容Cin、輸出電容Cout放置于Vin管腳、Vout管腳與DC/DC的GND之間,盡量減小Vin、Vout與DC/DC的GND之間的環路面積,這樣可以減小電源紋波幅度,大大提高芯片的可靠性,如圖6-10所示。

輸入電容Cin、輸出電容Cout以及DC/DC的GND,要盡量多打一些過孔,建議4個及以上的0.5*0.3mm過孔,如果 Vin,Vout電源有換層,建議過孔也要多打一些過孔,建議4個以上的0.5*0.3mm過孔(和電流有關系,參考上面RK3588峰值電流表)。電感要盡量靠近DC/DC,走線要盡量粗而短,FB端的電阻地盡量遠離干擾源,不要從電感下面走線。

1.3 RK860電源PCB設計

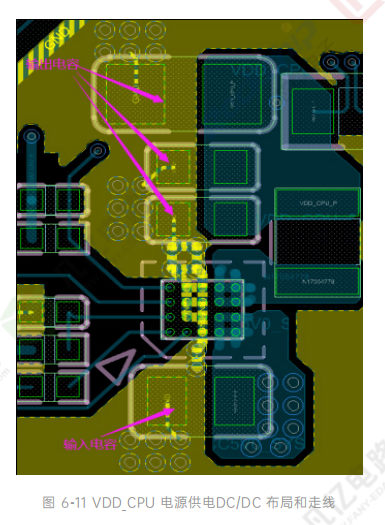

RK860-X做為單顆RK806-1的輔助補充供電,一般給CPU、GPU或NPU等大電流供電。整體布局時應盡量靠近RK3588(10mm以內為佳)。RK860 PCB布局推薦參考如圖6-11所示,需要注意的是輸入或者輸出的回路。

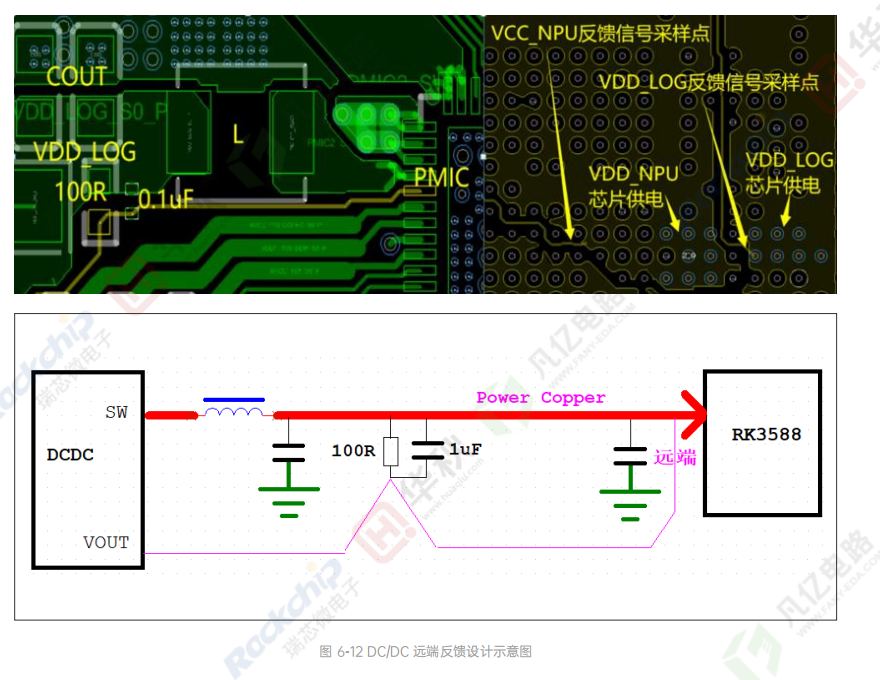

DC-DC轉換中會涉及到反饋電壓,遠端反饋是反饋點選擇在負載端;在PCB進行布線的時候,需要慎重考慮布線的方式,要充分考慮到布線產生的線路阻抗100歐姆反饋電阻需要靠近輸出電容盡量靠近PMIC放置,電阻一端連接到DC-DC輸出電容,另一端連接到PMIC的VOUT反饋腳上,并同時連接到RK3588電源管腳同一電源網絡的最遠端負載處。

反饋線寬度使用4mil,必須與電源覆銅伴隨走線,以避免干擾;反饋線與其他信號間隔6mil以上,如圖6-12所示, VDD_GPU電源覆銅及反饋線走線示意圖,其它路電源類似處理。

1、輸入輸出電容分別擺在芯片的兩端并盡量靠近芯片,電容、電感和芯片布局在同一層,電容的GND焊盤和芯片的GND在焊盤朝向是同一個方向,形成一個最小的閉環。

2、電感放在輸出電容和芯片兩端保證SW走線盡可能短,防止對其他模塊造成干擾。

3、芯片VOUT反饋信號要保證取自輸出電容(避免從電感焊盤上取),并避免離SW太近。

4、對于需要打過孔的地方,可以5個0.5*0.3mm的過孔,Buck輸出至少需要12個0.5*0.3mm的過孔。特別是GND過孔盡量靠近芯 GND和電容焊盤,如果是盲埋孔的板子就在芯片和電容的GND焊盤補一些盲孔。

1.4 VDD_LOGIC,VDD_GPU,VDD_NPU,VDD_CPU電源的DC-DC遠端反饋設計

DC-DC轉換中會涉及到反饋電壓,遠端反饋是反饋點選擇在負載端;在PCB進行布線的時候,需要慎重考慮布線的方式,要充分考慮到布線產生的線路阻抗100歐姆反饋電阻需要靠近輸出電容盡量靠近PMIC放置,電阻一端連接到DC-DC輸出電容,另一端連接到PMIC的VOUT反饋腳上,并同時連接到RK3588電源管腳同一電源網絡的最遠端負載處。

反饋線寬度使用4mil,必須與電源覆銅伴隨走線,以避免干擾;反饋線與其他信號間隔6mil以上,如圖6-12所示, VDD_GPU電源覆銅及反饋線走線示意圖,其它路電源類似處理。

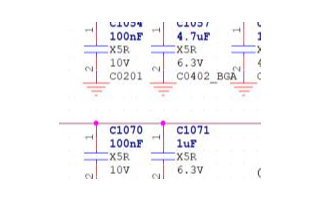

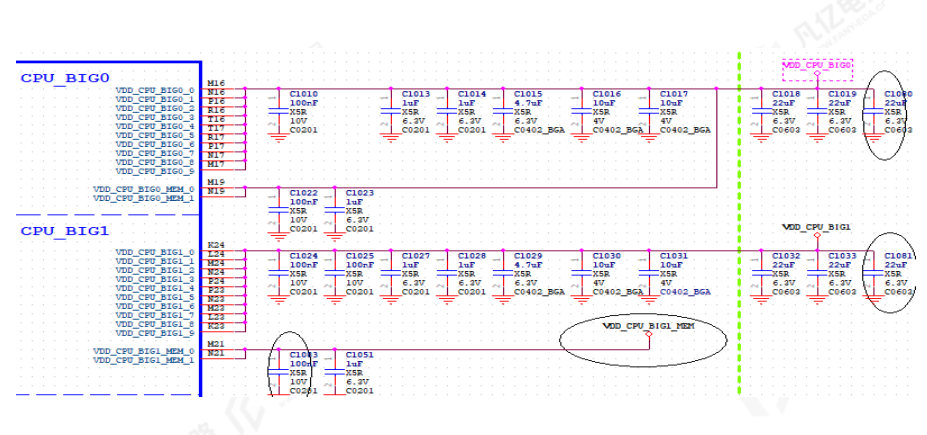

1.5 RK3588VDD_CPU_BIG0/1 電源PCB設計

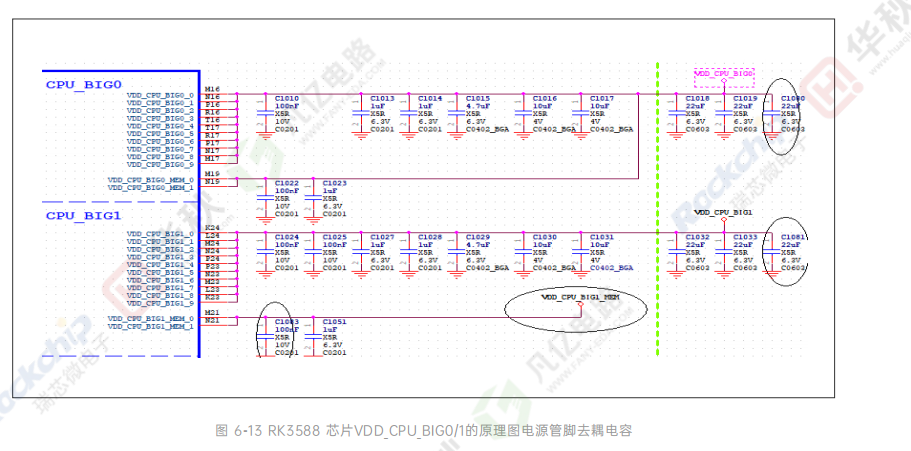

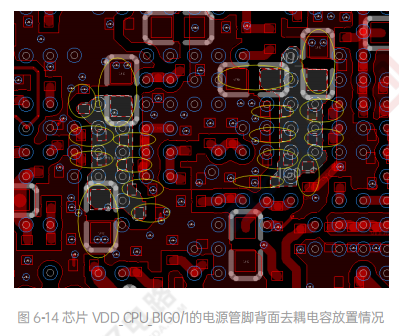

1、如圖6-13所示的濾波電容,原理圖上靠近 RK3588的VDD_CPU_BIG電源管腳綠線以內的去耦電容務必放在對應的電源管腳背面,電容GND PAD盡量靠近芯片中心的GND管腳放置,如圖6-14所示。其余的去耦電容盡量擺放在3588芯片附近,而卻需要擺放在電源分割來源的路徑上。

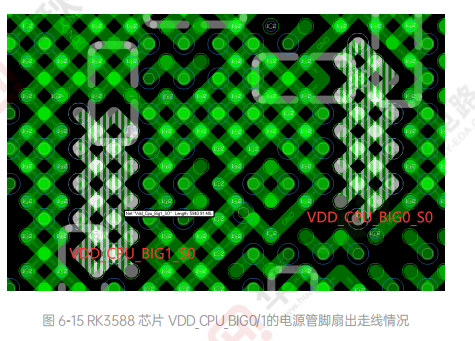

2、RK3588芯片VDD_CPU_BIG0/1的電源管腳,保證每個管腳邊上都有一個對應的過孔,并且頂層走“井”字形,交叉連接,如圖6-15所示,建議走線線寬10mil。

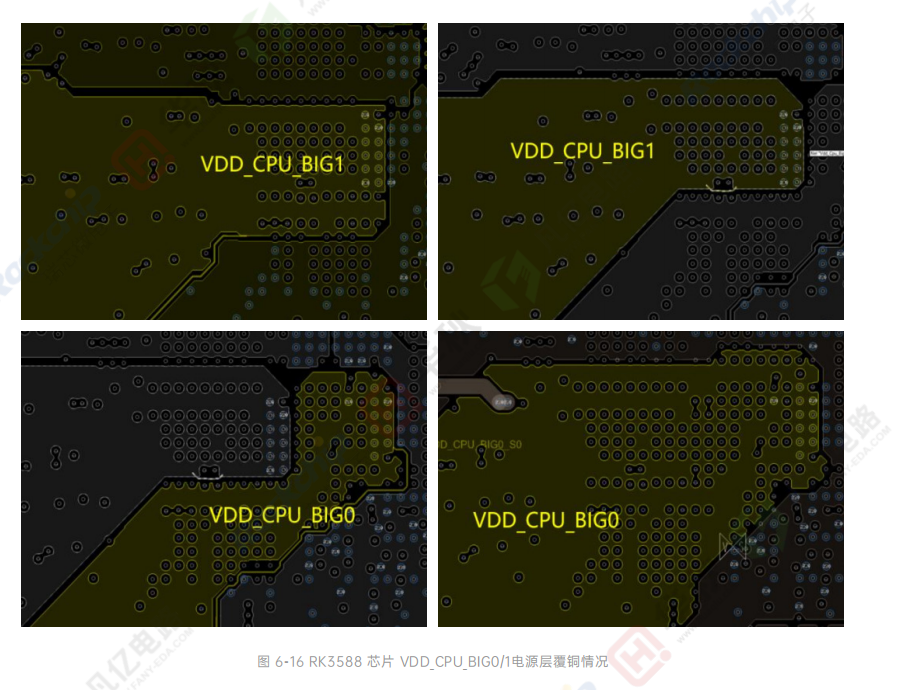

3、VDD_CPU_BIG0/1覆銅寬度需滿足芯片的電流需求,連接到芯片電源管腳覆銅足夠寬,路徑不能被過孔分割太嚴重,必須計算有效線寬,確認連接到CPU每個電源PIN腳路徑都足夠。

4、VDD_CPU_BIG的電源在外圍換層時,要盡可能的多打電源過孔12個及以上0.5*0.3mm的過孔,降低換層過孔帶來的壓降;去耦電容的GND過孔要跟它的電源過孔數量保持一致,否則會大大降低電容作用。

5、VDD_CPU_BIG電流比較大需要雙層覆銅,VDD_CPU_BIG 電源在 CPU 區域線寬合計不得小于 300mil,外圍區域寬度不小于600mil,盡量采用覆銅方式,降低走線帶來壓降其它信號換層過孔請不要隨意放置,必須規則放置,盡量騰出空間走電源,也有利于地層的覆銅,如圖6-16所示。

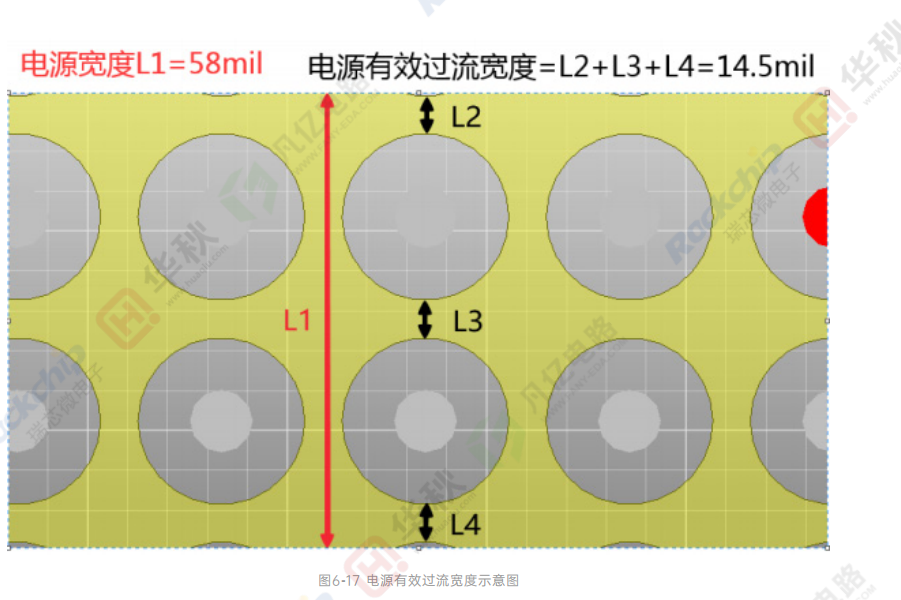

6、電源平面會被過孔反焊盤破壞,PCB設計時注意調整其他信號過孔的位置,使得電源的有效寬度滿足要求。下圖L1為電源銅皮寬度58mil,由于過孔的反焊盤會破壞銅皮,導致實際有效過流寬度僅為L2+L3+L4=14.5mil,如圖6-17所示。

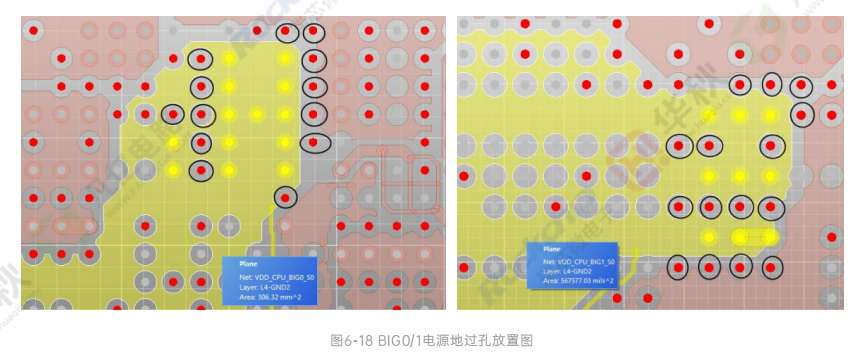

7、BIG0/1電源過孔40mil范圍(過孔中心到過孔中心間距)內的GND過孔數量,建議≧12個,如圖6-18所示。

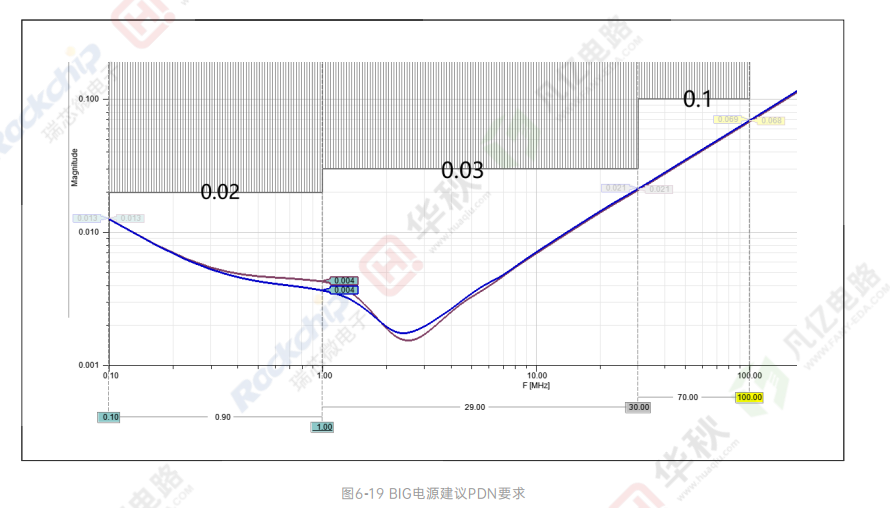

8、BIG電源PDN目標阻抗建議值如下表6-2所示和圖6-19所示:

1.6 RK3588 VDD_LOGIC電源PCB設計

1、VDD_LOGIC的覆銅寬度需滿足芯片的電流需求,連接到芯片電源管腳的覆銅足夠寬,路徑不能被過孔分割太嚴重,必須計算有效線寬,確認連接到CPU每個電源PIN腳路徑都足夠。

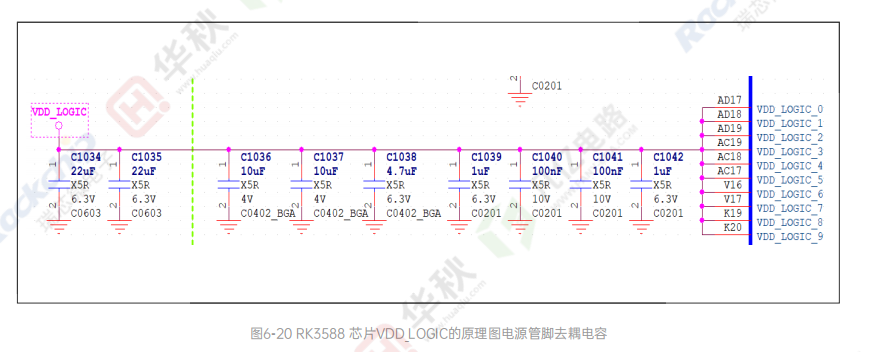

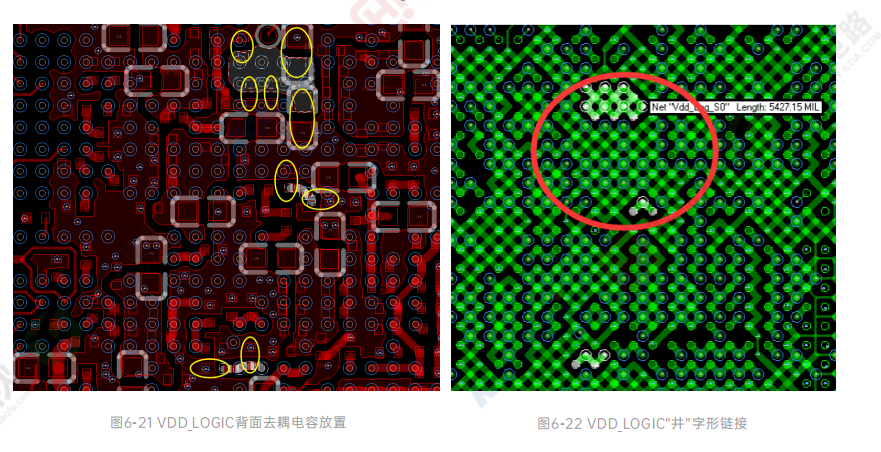

2、如圖6-20所示,原理圖上靠近RK3588的VDD_LOGIC電源管腳綠線以內的去耦電容務必放在對應的電源管腳背面,電容的GND管腳盡量靠近芯片中心的GND管腳放置,如圖6-21所示。其余的去耦電容盡量擺放在RK3588芯片附近,并擺放在電源分割來源的路徑上。

3、RK3588芯片VDD_LOGIC的電源管腳,每個管腳需要對應一個過孔,并且頂層走“井”字形,交叉連接,如圖6-22所示,建議走線線寬10mil。

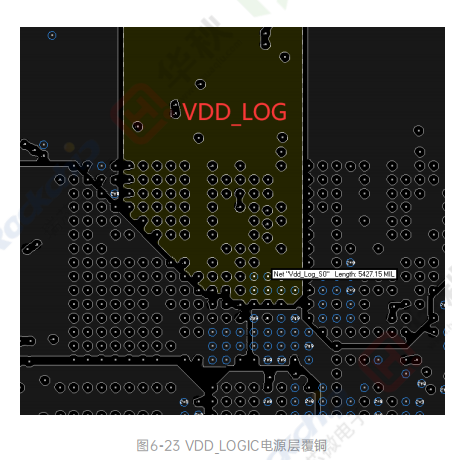

4、VDD_LOGIC電源在CPU區域線寬不得小于120mil,外圍區域寬度不小于200mil,盡量采用覆銅方式,降低走線帶來壓降(其它信號換層過孔請不要隨意放置,必須規則放置,盡量騰出空間走電源,也有利于地層的覆銅),如圖6-23所示。

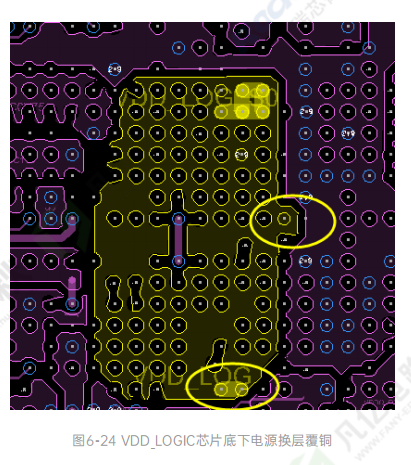

5、VDD_LOGIC的電源在外圍換層時,要盡可能的多打電源過孔(8個以上10-20mil的過孔),降低換層過孔帶來的壓降;去耦電容的GND過孔要跟它的電源過孔數量保持一致,否則會大大降低電容作用,如圖6-24所示。

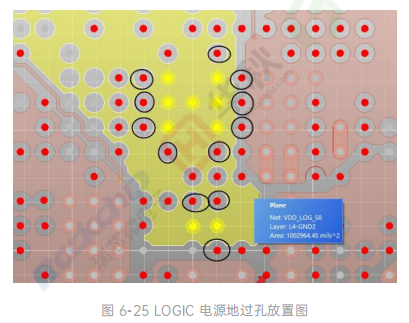

6、電源過孔40mil范圍(過孔中心到過孔中心間距)內的GND過孔數量,建議≧11個,如圖6-25所示。

1.7 RK3588 VDD_GPU電源PCB 設計

1、VDD_GPU的覆銅寬度需滿足芯片的電流需求,連接到芯片電源管腳的覆銅足夠寬,路徑不能被過孔分割太嚴重,必須計算有效線寬,確認連接到CPU每個電源PIN腳的路徑都足夠。

2、VDD_GPU 的電源在外圍換層時,要盡可能的多打電源過孔(10個以上0.5*0.3mm的過孔),降低換層過孔帶來的壓降;去耦電容的GND過孔要跟它的電源過孔數量保持一致,否則會大大降低電容作用。

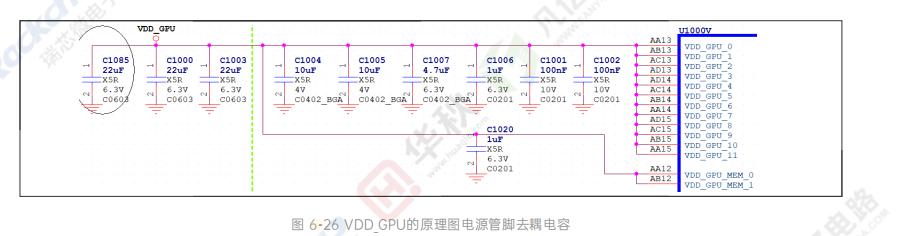

3、如圖6-26所示,原理圖上靠近RK3588的VDD_GPU電源管腳綠線以內的去耦電容務必放在對應的電源管腳背面,電容的GND PAD盡量靠近芯片中心的GND管腳放置,如圖6-27所示。其余的去耦電容盡量擺放在RK3588芯片附近,并需要擺放在電源分割來源的路徑上。

4、RK3588芯片VDD_GPU的電源管腳,每個管腳需要對應一個過孔,并且頂層走“井”字形,交叉連接,如圖6-28所示,建議走線線寬10mil。

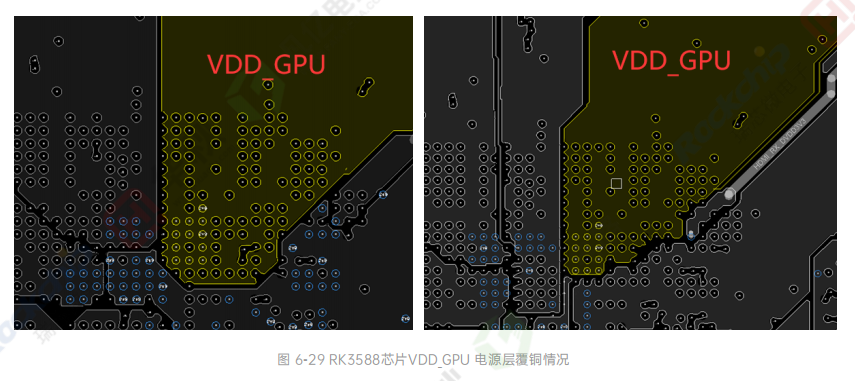

5、VDD_GPU電源在GPU區域線寬不得小于300mil,外圍區域寬度不小于500mil,采用兩層覆銅方式,降低走線帶來壓降,如圖6-29所示。

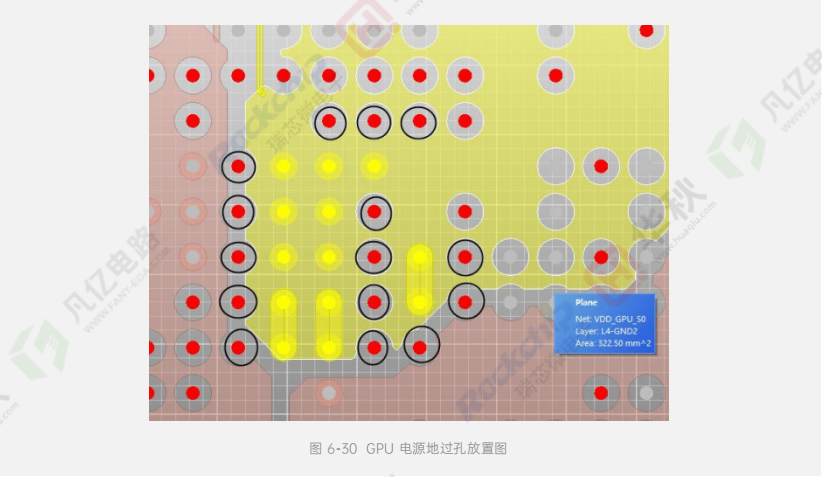

6、電源過孔40mil范圍(過孔中心到過孔中心間距)內的GND過孔數量,建議≧14個,如圖6-30所示。

1.8 RK3588 VDD_NPU電源PCB設計

1、VDD_NPU的覆銅寬度需滿足芯片的電流需求,連接到芯片電源管腳的覆銅足夠寬,路徑不能被過孔分割太嚴重,必須計算有效線寬,確認連接到CPU每個電源PIN腳的路徑都足夠。

2、VDD_NPU的電源在外圍換層時,要盡可能的多打電源過孔(7個以上0.5*0.3mm的過孔),降低換層過孔帶來的壓降;去耦電容的GND過孔要跟它的電源過孔數量保持一致,否則會大大降低電容作用。

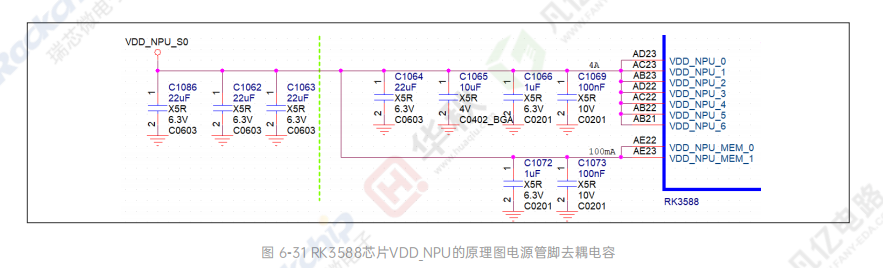

3、如圖6-31所示,原理圖上靠RK3588的VDD_NPU電源管腳綠線以內的去耦電容務必放在對應的電源管腳背面,電容的GND PAD盡量靠近芯片中心的GND管腳放置,如圖6-32所示。其余的去耦電容盡量擺放在RK3588芯片附近,并需要擺放在電源分割來源的路徑上。

4、RK3588芯片VDD_NPU的電源管腳,每個管腳就近有一個對應過孔,并且頂層走“井”字形,交叉連接,如圖6-33所示 ,建議走線線寬10mil。

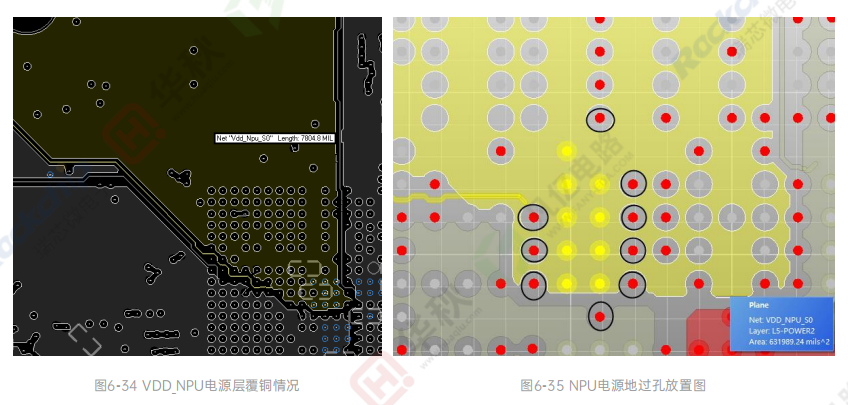

5、VDD_NPU電源在NPU區域線寬不得小于300mil,外圍區域寬度不小于500mil,盡量采用覆銅方式,降低走線帶來的壓降(其它信號換層過孔請不要隨意放置,必須規則放置,盡量騰出空間走電源,也有利于地層的覆銅,如圖6-34)。

6、電源過孔40mil范圍(過孔中心到過孔中心間距)內的GND過孔數量,建議≧9個。如圖6-35所示。

1.9 RK3588 VDD_CPU_LIT電源PCB設計

1、VDD_CPU_LIT覆銅寬度需滿足芯片電流需求,連接到芯片電源管腳的覆銅足夠寬,路徑不能被過孔分割太嚴重,必須計算有效線寬,確認連接到CPU每個電源PIN腳的路徑都足夠。

2、VDD_CPU_LIT的電源在外圍換層時,要盡可能的多打電源過孔(9個以上0.5*0.3mm的過孔),降低換層過孔帶來的壓降;去耦電容的GND過孔要跟它的電源過孔數量保持一致,否則會大大降低電容作用。

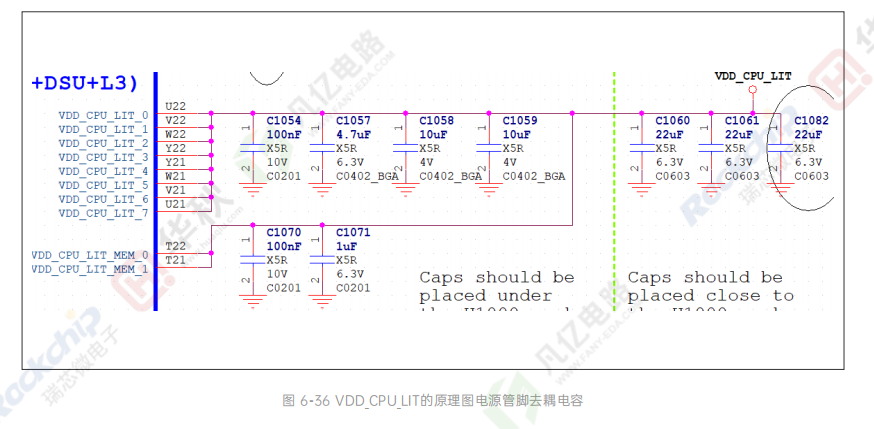

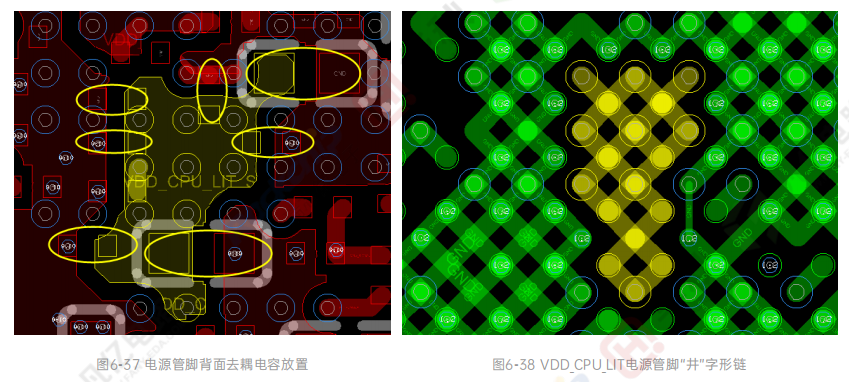

3、如圖6-36所示,原理圖上靠近RK3588的VDD_CPU_LIT電源管腳綠線以內的去耦電容務必放在對應的電源管腳背面,電容的GND PAD盡量靠近芯片中心的GND管腳放置,如圖6-37所示。其余的去耦電容盡量擺放在RK3588芯片附近,并需要擺放在電源分割來源的路徑上。

4、RK3588芯片VDD_CPU_LIT的電源管腳,每個管腳就近有一個對應過孔,并且頂層走“井”字形,交叉連接,如圖6-38所示,建議走線線寬10mil。

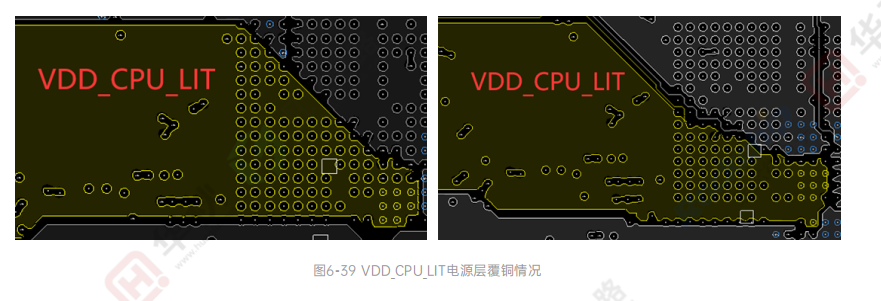

5、VDD_CPU_LIT電源在CPU 區域線寬不得小于120mil,外圍區域寬度不小于300mil,采用雙層電源覆銅方式,降低走線帶來壓降(其它信號換層過孔請不要隨意放置,必須規則放置,盡量騰出空間走電源,也有利于地層的覆銅,如圖6-39所示)。

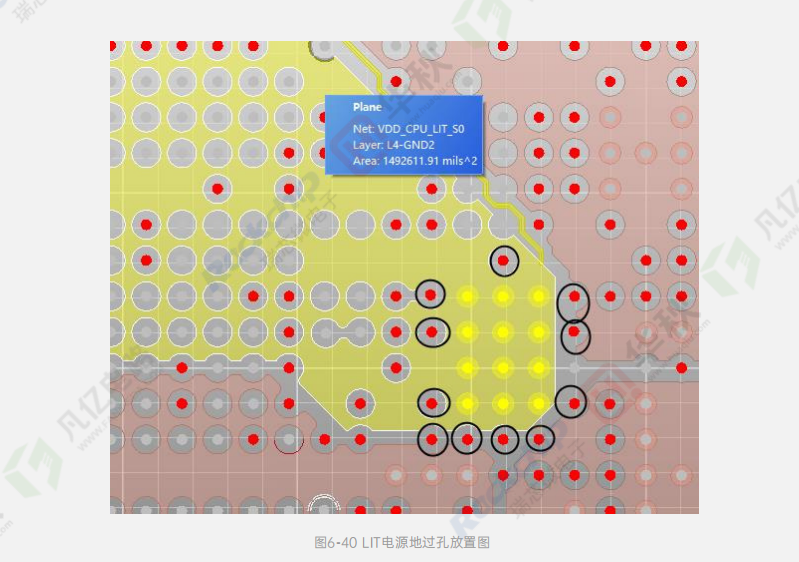

6、電源過孔40mil范圍(過孔中心到過孔中心間距)內的GND過孔數量,建議≧9個。如圖6-40所示。

1.10 RK3588 VDD_VDENC電源PCB設計

1、VDD_VDENC覆銅寬度需滿足芯片的電流需求,連接到芯片電源管腳的覆銅足夠寬,路徑不能被過孔分割太嚴重,必須計算有效線寬,確認連接到CPU每個電源PIN腳的路徑都足夠。

2、VDD_VDENC電源在外圍換層時,要盡可能的多打電源過孔(9個以上0.5*0.3mm的過孔),降低換層過孔帶來的壓降;去耦電容的GND過孔要跟它的電源過孔數量保持一致,否則會大大降低電容作用。

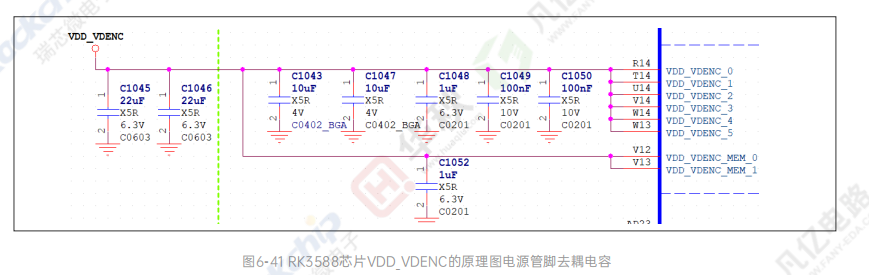

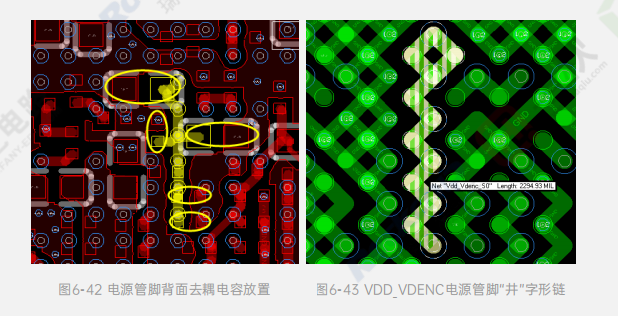

3、如圖6-41所示,原理圖上靠近RK3588的VDD_VDENC電源管腳綠線以內的去耦電容務必放在對應的電源管腳背面,電容的GND PAD盡量靠近芯片中心的GND管腳放置,如圖6-42所示。其余的去耦電容盡量擺放在RK3588芯片附近,并需要擺放在電源分割來源的路徑上。

4、RK3588芯片VDD_VDENC的電源管腳,每個管腳就近有一個對應過孔,并且頂層走“井”字形,交叉連接,如圖6-43所示,建議走線線寬 10mil。

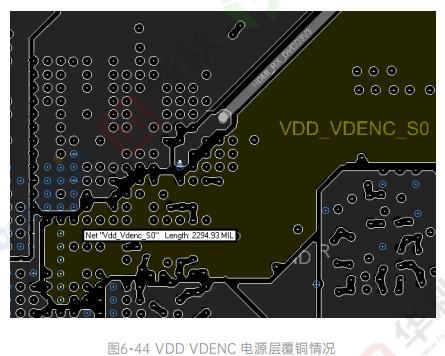

5、VDD_VDENC電源在CPU區域線寬不得小于100mil,外圍區域寬度不小于300mil,采用雙層電源覆銅方式,降低走線帶來壓降,如圖6-44所示。

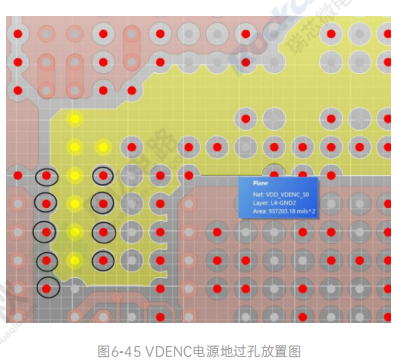

6、電源過孔30mil范圍(過孔中心到過孔中心間距)內的 GND 過孔數量,建議≧8個。如圖6-45所示。

1.11 RK3588 VCC_DDR電源PCB設計

1、VCC_DDR覆銅寬度需滿足芯片的電流需求,連接到芯片電源管腳的覆銅足夠寬,路徑不能被過孔分割太嚴重,必須計算有效線寬,確認連接到CPU每個電源PIN腳的路徑都足夠。

2、VCC_DDR的電源在外圍換層時,要盡可能的多打電源過孔(9個以上0.5*0.3mm的過孔),降低換層過孔帶來的壓降;去耦電容的GND過孔要跟它的電源過孔數量保持一致,否則會大大降低電容作用。

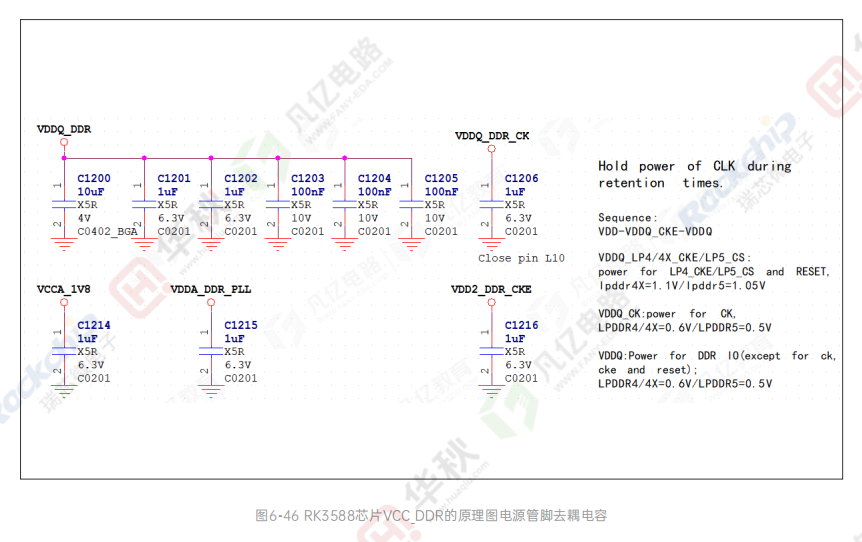

3、如圖6-46所示,原理圖上靠近RK3588的VCC_DDR電源管腳的去耦電容務必放在對應的電源管腳背面,電容的GND PAD盡量靠近芯片中心的GND管腳放置,其余的去耦電容盡量靠近RK3588,如圖6-47所示。

4、RK3588 芯片 VCC_DDR 的電源管腳,每個管腳需要對應一個過孔,并且頂層走“井”字形,交叉連接,如圖6-48所示,建議走線線寬 10mil。

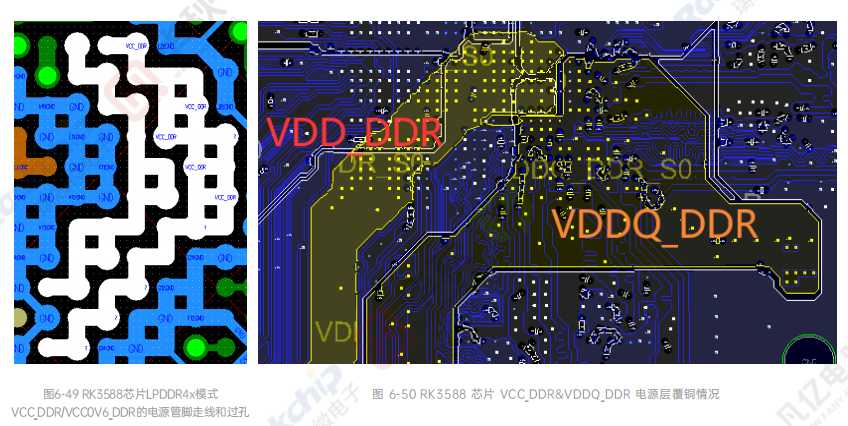

當LPDDR4x 時,鏈接方式如圖6-49所示:

5、VCC_DDR電源在CPU區域線寬不得小于120mil,外圍區域寬度不小于200mil,盡量采用覆銅方式,降低走線帶來壓降(其它信號換層過孔請不要隨意放置,必須規則放置,盡量騰出空間走電源,也有利于地層的覆銅,如圖6-50所示)。

1.12 RK3588 GND管腳PCB設計

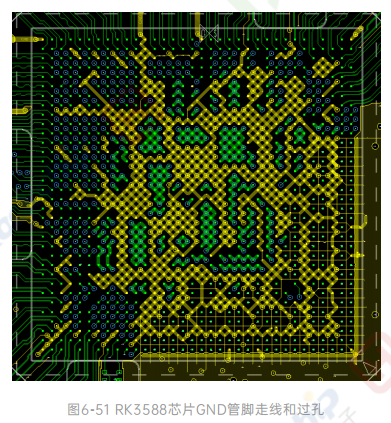

1、RK3588芯片的GND管腳,至少保證每2個管腳需要對應一個過孔,盡量每個管腳對應一個過孔,提供更優的SI(信號完整性),PI(電源完整性)條件,以及對散熱也有幫助。

2、RK3588芯片的相鄰層必須是一個完整的 GND 平面,保證主參考地靠近CPU的管腳,用于保證電源完整性以及加強PCB 的散熱。

3、RK3588芯片下方相同網絡的GND管腳在頂層走“井”字形,交叉連接,建議走線線寬10mil。如圖6-51所示。

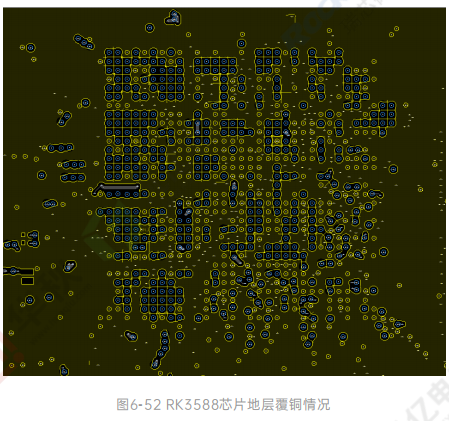

4、在Layout 時,RK3588的各信號放置換層過孔時,要求打在管腳間隔的正中間,有規律的放置,如圖6-52,GND層的覆銅情況,RK3588芯片中間的地有大面積的銅皮和外面地銅皮連接,一方面有利于電源信號完整性,另外一方面有利于芯片散熱。

1.13 RK3588 其它電源的PCB設計

1、RK3588其它電源去耦電容,必須放在芯片管腳背面,走線時盡量形成先經過電容焊盤再到芯片管腳。

2、無論是輸入或是輸出、功率環路或信號環路,應盡可能的小。功率環路發射電磁場,將導致較差的EMI特性或較大的輸出噪聲;同時,若被控制環接收,很可能引起異常。

3、另一方面,若功率環路面積較大,其等效寄生電感也會增大,可能增加漏極噪聲尖峰。

審核編輯:湯梓紅

-

電源電路

+關注

關注

48文章

998瀏覽量

65227 -

PCB設計

+關注

關注

394文章

4691瀏覽量

85855 -

PMIC

+關注

關注

15文章

337瀏覽量

109522 -

RK3588

+關注

關注

6文章

335瀏覽量

4388

原文標題:RK3588 PMIC/Power電路PCB設計(附白皮書下載)

文章出處:【微信號:發燒友研習社,微信公眾號:發燒友研習社】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RK3588 VDD_CPU_LIT電源PCB設計

瑞芯微RK3588開發板RK3588 EVB和RK3588S EVB解讀

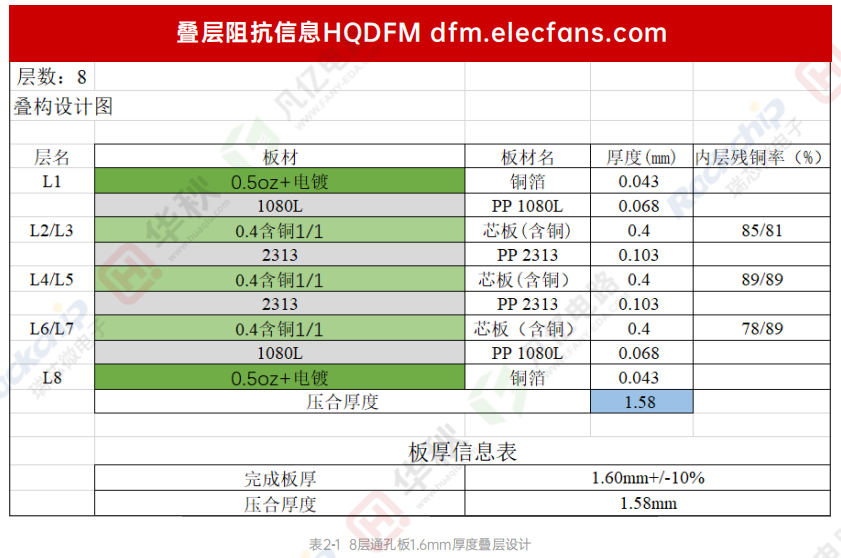

RK3588 PCB推薦疊層及阻抗設計

RK3588 VDD_LOGIC電源PCB設計注意事項

用這份PCB設計實戰手冊輕松搞定RK3588

用這份PCB設計實戰手冊,輕松搞定RK3588

【全是干貨】《RK3588 PCB設計指導白皮書》線上發布&實戰解讀

PCB設計沒頭緒?RK3588 PCB設計指導,搞硬件必入手!

rk3588和rk3588s的區別

RK3588與3588s的區別

RK3588 VDD_CPU_BIG0/1 電源PCB設計注意事項

RK3588電源電路PCB設計方案

RK3588電源電路PCB設計方案

評論