導讀:

異步FIFO包含"讀"和"寫“兩個部分,寫操作和讀操作在不同的時鐘域中執行,這意味著Write_Clk和Read_Clk的頻率和相位可以完全獨立。異步FIFO的原理很簡單,寫操作是在寫使能有效時,寫地址指針(Write_Pointer)逐漸遞增,將數據寫入存儲器的相應位置。讀操作是在讀使能信號有效時,讀地址指(Read_Pointer)逐漸遞增,從存儲器的相應位置讀取數據。

但異步FIFO有一個難點就是—滿和空的產生。寫操作,我們得判斷FIFO是不是滿了,滿了就不能繼續往里面寫,不然就會覆蓋還沒取走的數據。對于讀操作,我們得判斷FIFO是不是空了,空了就不能接著取,不然舊的數據會被取多次。

觸發異步FIFO的滿和空,是拿讀和寫的Pointer做比較得到的。問題在于:寫操作下的Write_Pointer和讀操作下的Read_Pointer屬于兩個不同的時鐘域信號。兩個不同的時鐘域信號是不能直接做運算的,需要同步到同一個時鐘域之后才行,因為有這個CDC同步器的開銷,導致FIFO出現 真 滿空和 假 滿空。

接下來我們一起來看看標準異步FIFO的”真“滿空和“假“滿空如何產生,以及采用格雷碼異步FIFO跟標準FIFO有什么區別。(這里所謂標準異步FIFO是指不使用特殊編碼方式(如格雷碼)的異步FIFO,即使用常規的二進制地址指針。)

標準異步FIFO

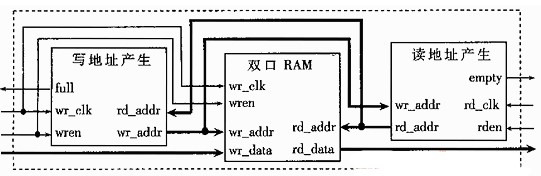

標準異步FIFO結構如上圖,假設FIFO的深度為8,addr(地址范圍)為0 ~ 7。那么設計讀寫地址指針都是4bit,即w_ptr[3:0],r_ptr[3:0],其中最高bit是擴展位。ptr取值范圍是0 ~15,要比FIFO地址(addr)多一倍。為什么這么設計呢?因為滿和空本質上是讀和寫指向了FIFO的同一個存儲單元,但是“空”是讀指針追上了寫指針,“滿”是寫指針超過了讀指針整整一圈。其中最高位就是用來確定是 “誰追上了誰”

如果兩個ptr低位全等,最高位不等,就是“滿”;

如果兩個Ptr低位全等,最高位相等,就是“空”。

如圖所示,將w_ptr通過CDC同步之后,送到讀時鐘域,得到w_ptr_syn,然后再將它和r_ptr作比較,就可以得到“空”信號,代碼如下:

assign empty = (w_ptr_syn[3:0]== r_ptr[3:0]);

同理,將r_ptr通過CDC同步之后,送到寫時鐘域,得到r_ptr_syn,然后將它和w_ptr作比較,就可以得到滿信號,代碼如下:

assign full = (w_ptr[3] != r_ptr_syn[3]) && (w_ptr[2:0] == r_ptr_syn[2:0]);

大家覺得上面的代碼得到的滿和空是“ 真”滿空嗎?

答案是否定的。因為CDC同步器本身也需要開銷,一般簡單的兩級同步器需要目標時鐘域兩個時鐘周期。當我們判斷滿信號的時候,我們是在 寫時鐘域 ,用w_ptr和同步過來的r_ptr_syn做比較。r_ptr_syn要比真正的r_ptr要滯后,導致判滿的邏輯并不完全準確。當FIFO接近滿的時候,full信號就會為1,從而阻止對FIFO繼續寫入(腦補:“滿”意味著寫比讀塊,寫指針馬上趕上讀指針一圈,此刻還與滯后同步過來的讀指針比較,是不是快滿還沒滿時就滿足full條件了?)。同理,當FIFO接近空,但是實際可能還沒空的時候,empty信號就會為1。

這種假滿空并不會導致FIFO的行為出錯,只會導致FIFO的利用率并非百分百,相當于FIFO的深度少了那么一兩層。

那么FIFO能得到真滿空嗎?

答案肯定是可以的。如果我們在寫時鐘域判斷“空”信號,在讀時鐘域判斷“滿”信號呢?(在寫時鐘域,通過滯后的r_ptr_syn都得到了“空”信號,那說明實際的r_ptr必然真的趕上了w_ptr,此刻FIFO絕對空了。在讀時鐘域,通過滯后的w_ptr_syn都得到了“滿”信號,那說明實際的w_ptr必然真的超過了r_ptr一圈,此刻FIFO絕對滿了)。

assign empty_real = (w_ptr[3:0] == r_ptr_syn[3:0]);

assign full_real = (r_ptr[3] != w_ptr_syn[3]) && (r_ptr[2:0] == w_ptr_syn[2:0]);

這個“真”滿空信號,用到的時候并不多。但是理解“真”滿空和“假”滿空,是理解異步FIFO的基礎。

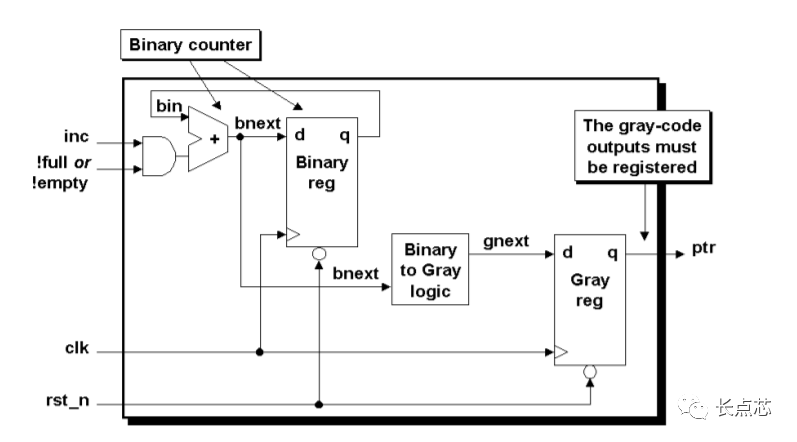

采用格雷碼的異步FIFO

采用格雷碼的異步FIFO判斷“滿”和“空”的原理沒變,跟標準FIFO是一樣的,即在寫時鐘域判斷滿條件,在讀時鐘域判斷空條件:

如果兩個ptr低位全等,最高位不等,就是“滿”;

如果兩個Ptr低位全等,最高位相等,就是“空”。

只不過,地址指針采用的是格雷碼,如寫地址指針:

assign nxt_wptr = (!full && wr_en) ? (wptr +1'b1):wptr;

assign nxt_wptr_gray = (nxt_wptr >>1)^nxt_wptr;

判斷空條件:則在讀時鐘域,讀地址指針格雷碼 與 兩級同步過來后的寫地址指針格雷碼(nxt_wptr_gray)進行比較:

always@(posedge rclk or negedge rst_n)

begin

if(!rst_n) begin

wptr_sp1<=6'b0;

wptr_sp2<=6'b0;

end

else begin

wptr_sp1<=nxt_wptr_gray;

wptr_sp2<=wptr_sp1;

end

end

assign empty=(rptr_gray==wptr_sp2);

同理,判斷滿條件:

assign full=(wptr_gray=={~rptr_sp2[3],rptr_sp2[2:0]});

理解到這兒,本質上兩種FIFO似乎沒什么區別,那為什么要用格雷碼編碼呢? 異步FIFO采用格雷碼的主要原因是為了減少在異步時鐘域中地址指針變化時可能出現的不穩定性,從而增強異步FIFO的可靠性和穩定性 。即使在亞穩態進行讀寫指針抽樣也能進行正確的空滿狀態判斷”。

下面兩張圖是采用格雷碼的異步FIFO觸發滿和空條件的截圖,從圖示可看出,4根標紅的格雷碼地址指針 每一周期前后只有1位發生跳變,如wptr_gray:0010>0110>0111>0101>0100>1100>1101>1111>1110,這就是格雷碼的特性,保證了相鄰的兩個值只有一個位元發生變化,因此在變化時不會出現多個位同時變化,減少了不穩定狀態的可能性。

滿條件

空條件

為什么2 進制指針做空滿判斷存在不穩定的可能呢?事實上 2 進制讀指針在增減時,經常發生多位突變,比如 6 位地址 111111 會在下一時刻變成 000000 ,在實際電路中,這個變化過程要持續很長一段時間,會由 111111 經歷 6 個狀態轉移到達 000000 。比如 111111-> 101111 -> 100111 ->100110 -> 100100 -> 000100-> 000000 。由于寫時鐘與讀時鐘不同步,異步的寫時鐘很可能會在狀態不穩定的中間某個狀態抽樣,這樣就會得到錯誤的讀指針,進而做出錯誤的狀態判斷,導致系統異常。

當采用格雷碼只有一個比特發生改變時,即使在中間狀態抽樣,其結果也不外乎兩種:遞增前原指針和遞增后新指針。如果抽樣到遞增后的指針,預期結果跟設計一致。如果抽樣到遞增前的原指針,最壞的情況就是把“不滿”判斷成了“滿”,但是這并不會對邏輯產生影響,只是帶來了寫操作的延遲。

總結(兩種fifo的主要區別)

因此,標準范式的FIFO和采用格雷碼的FIFO都存在一定的可能出現假滿空。兩者有一些區別,主要涉及到地址指針的表示和更新方式。以下是這兩種FIFO的主要區別:

- 地址指針的表示:

- 標準范式的FIFO:常常使用二進制表示的地址指針。這意味著每個存儲單元都有一個唯一的二進制地址,用于指示數據在FIFO中的位置。

- 采用格雷碼的FIFO:地址指針通常使用格雷碼來表示。格雷碼是一種二進制碼,相鄰的兩個值只有一個位元發生變化。使用格雷碼可以減少地址指針在變化時的不穩定性,從而減少在時鐘邊沿時的不穩定狀態。

- 地址指針的更新方式:

- 標準范式的FIFO:地址指針在每個時鐘周期朝一個方向遞增或遞減,用于確定要讀取或寫入的位置。在寫入數據時,寫指針增加;在讀取數據時,讀指針增加。

- 采用格雷碼的FIFO:格雷碼地址指針的更新方式相對復雜一些。格雷碼的特性使得在更新時只有一個位發生變化,這樣可以減少指針變化的不穩定性。在讀寫操作時,格雷碼地址指針的更新可能需要一些額外的邏輯。

- 時序穩定性:

- 標準范式的FIFO:由于二進制地址指針的性質,通用FIFO在時序上需要額外的同步邏輯,以確保地址指針的穩定傳遞。這尤其在不同時鐘域的情況下需要考慮。

- 采用格雷碼的FIFO:格雷碼的特性減少了地址變化的不穩定性,因此在一些時序方面可能更容易處理。但格雷碼的使用可能需要更多的邏輯來實現。

選擇使用哪種FIFO設計取決于具體的應用需求和時序約束。格雷碼的FIFO在一些特定情況下可能提供一些優勢,但也需要權衡設計的復雜性。

-

fifo

+關注

關注

3文章

387瀏覽量

43650 -

信號

+關注

關注

11文章

2789瀏覽量

76730 -

時鐘域

+關注

關注

0文章

52瀏覽量

9535 -

異步FIFO

+關注

關注

0文章

20瀏覽量

8354

發布評論請先 登錄

相關推薦

基于FPGA的異步FIFO的實現

詳細討論異步FIFO的具體實現???

請問SPI使用FIFO和不使用有什么區別?使用FIFO效率更高嗎?

Camera Link接口的異步FIFO設計與實現

異步FIFO的設計分析及詳細代碼

利用VHDL語言和格雷碼對地址進行編碼的異步FIFO的設計

異步FIFO用格雷碼的原因有哪些

異步fifo詳解

同步FIFO和異步FIFO區別介紹

采用格雷碼異步FIFO跟標準FIFO有什么區別

采用格雷碼異步FIFO跟標準FIFO有什么區別

評論