在古代,我們的祖先就掌握了測試技術,例如農民發明吹風機測試稻谷,把飽滿的谷粒和谷殼分離開來,這就是早期的測試機器。

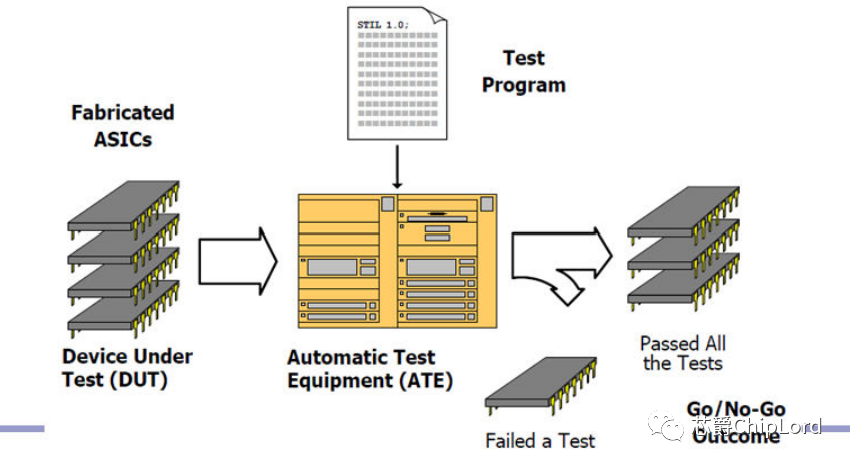

生產測試的目的是把好的物品和有瑕疵的物品分離出來,集成電路行業,測試的目標是把功能正確的芯片和有瑕疵的芯片分離出來,保證客戶使用的是功能完整的芯片。

按照摩爾定律,集成電路的規模每兩年翻一番,設計的規模越來越大,工藝尺寸越來越小。隨著電路的集成度越來越高,生產測試的成本也越來越高。為了降低測試成本和難度,提高芯片的質量和良品率,需要為芯片進行可測性設計(design for test),簡稱DFT。

可測性設計是在芯片設計過程中保證功能的前提下,加入特殊的測試結構,芯片制造完成后進行DFT測試,如果在制造或者封裝的過程中有瑕疵,芯片不能正常工作,通過DFT測試可以篩選出這種芯片。可測性設計與設計驗證不同,設計驗證是通過對設計的分析,排除設計中的錯誤,確保該設計符合其技術規范,保證設計與要求一致。

芯片制造和封裝過程中的測試可以大致分為如下三類:

其中WAT測試和DFT沒有關系,主要是用來檢測FAB的制造工藝是否有問題,它并沒有測試芯片,而是測試die和die之間的scribe line上面的特殊結構。

CP是測試晶圓上的每顆die,實際上,只有通過CP測試的die才會進行封裝,而未通過測試的die會被淘汰。

FT測試是die封裝以后的測試,如果沒有異常,才會到客戶那里。

可測性設計具體是什么呢?

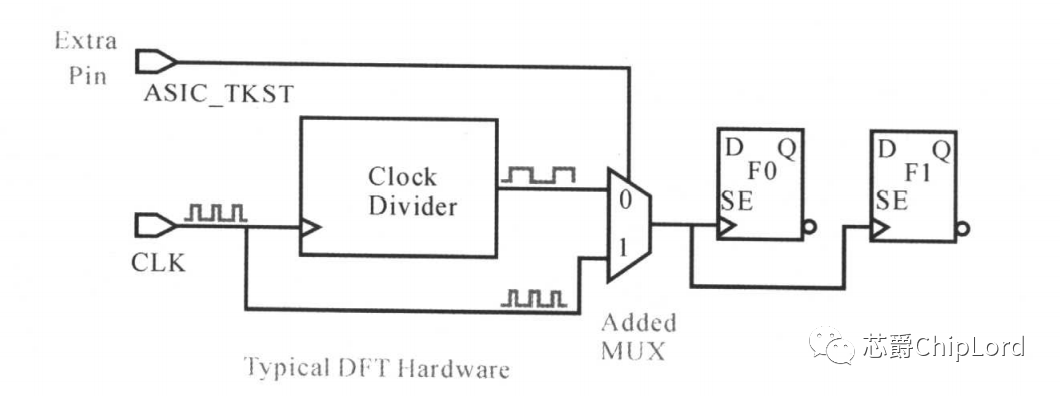

為了使芯片方便測試,在設計中額外的增加或者修改某些邏輯,增加輸入,輸出端口,但是這種設計不會改變芯片的功能。

如下圖所示:DFT就是增加額外的輸入端口(ASIC_TKST),在設計中加入MUX,使寄存器F0,F1的時鐘引腳在測試過程中可以直接由輸入時鐘端口CLK控制。

可測性設計內容豐富,主要分為四大類:后面會詳細介紹。

- Scan Chain

- Boundar Scan

- MBIST

- ATPG

當我們對已制造出來的芯片進行生產測試時,先把芯片插入自動測試設備中(ATE),然后輸入測試程序,測試程序中包含ATPG生成的測試向量,測試向量簡單理解包含輸入值和期望值,如果ATE收集的實際值和期望值不一致,則可以判斷芯片有故障。

接下來介紹物理瑕疵(defects)和故障模型(fault models),這里主要涉及抽象與建模。

芯片的物理瑕疵是指在生產制造過程中產生的瑕疵,這種瑕疵使得芯片不能正常工作,值得注意的是,這里的測試并不是測試邏輯設計的錯誤,而是測試在芯片生產過程中引入的瑕疵,主要由如下因素引起:

- 開路和短路(open and short)

- 金屬線之間的橋接(bridging bewteen metal lines)

- 通過絕緣氧化物的導電性擊穿(conductive pinholes through insulating oxides)

下圖是一個簡單CMOS反相器的物理版圖,它由一個n型下拉晶體管(n-type pull-down transistor)和一個p型上拉晶體管(p-type pull-up transistor)組成。如果一粒塵埃落在金屬連線上就可以使該線開路,過度的金屬刻蝕可能引起金屬橋接現象,即直接短路到電源或者地線上。一個有瑕疵的下來晶體管永遠處于開路的狀態,從而就像直接短路到地線上一樣。

瑕疵的行為就像永久的短路到電源或者地線上一樣,我們可以抽象為輸入或輸出引腳stuck at在邏輯"0"或"1"上,大部分的CMOS門單元的版圖類似,因此可以抽象建模,把stuck at 1 or 0代表具體的物理瑕疵。

綜上所述,故障模型(fault model)就是用抽象邏輯模型來表示物理瑕疵(defect)的結果。

stuck-at fault model(SAF)模型仍然是最常見的故障模型。

測試SAF的規則是不可以使用內部探針,我們只能通過輸入/輸出端口對芯片進行測試,經封裝后,輸入/輸出端口對應于芯片的封裝管腳,ATE設備可以對每個輸入端口進行驅動,控制測試芯片的每個輸入端,同時對每個輸出端進行采樣,把采樣結果與預期值進行比較,來判斷芯片的好壞。

-

寄存器

+關注

關注

31文章

5427瀏覽量

123738 -

晶體管

+關注

關注

77文章

9995瀏覽量

140979 -

DFT設計

+關注

關注

0文章

10瀏覽量

8979 -

時鐘控制

+關注

關注

0文章

17瀏覽量

6992 -

CMOS反相器

+關注

關注

0文章

19瀏覽量

6968

發布評論請先 登錄

評論