1.什么是Design for Tesability,我們為什么需要它?

a. 芯片在制造過程中的問題

如今,半導體是整個電子行業不斷發展的核心。新技術的發展,尤其是先進技術節點,如7nm及以下工藝,使集成電路行業能夠跟上消費者不斷增長的性能需求,也即摩爾定律得到延續,毫不夸張的說,集成電路技術是人類科技的支點。

但是,新的技術同時帶來了新的挑戰,芯片尺寸的變小會增加某些錯誤的可能性。芯片制造過程中的錯誤是我們不愿看到的,下面列出芯片制造中可能出現的一些問題。

- 密度問題 :隨著納米技術的出現,芯片制造過程越來越復雜。設計的晶體管越來越小,溝道長度越來越小,后端連線也越來越密集。現在的芯片,普遍有數十億個晶體管,所以,兩根導線之間短路或斷路的概率很大,這些是錯誤或者故障的來源。關鍵是,在設計和制造過程中可能會出現大量此類錯誤。綜上所述,晶體管密度的增加,芯片失效的可能性大大增加。

- 軟件問題 :此外,除了制造過程的defect,用于設計芯片的EDA軟件的bug或者工程師的失誤,也會造成芯片失效。

- 應用問題 :在一些關鍵應用中,我們無法承受芯片的故障。例如,在醫療行業,設備控制器中的單個故障甚至會造成個人生命危險。對于使用低溫燃料運行的火箭或航天飛機,其控制芯片需要在較寬的溫度范圍內工作。因此,這些芯片的測試條件應針對特定的環境且在極端條件上進行,以防止使用過程中發生任何故障。

- 維護問題 :萬一未來發生故障,為了進行維修或者保養,我們需要精準定位問題。由于PCB尺寸不斷縮小,因此用萬用表測試已經無法定位問題,而且模塊化設計正朝著SoC設計的方向發展,從而失去了相關性,最后使維護過程變得更加昂貴。

- 商業問題 :如果發現設計的芯片存在故障,最終會轉化為公司的重大損失。稍后我們將討論如何及時發現故障來降低成本。

即使在封裝過程中,也有可能出現故障。考慮到所有這些問題,最關鍵的是在芯片出廠前進行測試,并且在每個關鍵過程都需要測試。

b. 解決問題的辦法:DFT

測試從來就不是免費的午餐。現在的CPU都包含超過1000多個pins,內部包含許多功能,如果芯片內任一晶體管出現故障,整個芯片就會失效。作為消費者,我們不希望用到有故障的芯片。但是,要從數十億個晶體管中找到單個缺陷晶體管,猶如大海撈針。我們需要窮盡各種組合來測試芯片所有功能,如果以這種方式進行測試,那么芯片上市時間非常久遠,甚至以至于芯片可能永遠無法到達消費者手中。那么如何解決這種問題?我們使用一種方法為芯片添加測試功能,叫可測性設計design for testability,DFT并不影響芯片的正常工作。

簡而言之,可測性設計是一種通過向芯片添加更多電路來使芯片測試變得可行且具有成本效益的設計。此外,可測性設計技術可以改善內部節點的可控性和可觀察性,從而可以測試芯片內部功能。

c. DFT的作用

i.測試時序電路

DFT提供了測試時序電路的解決方案,時序電路由于和時鐘相關,正常的測試非常困難。與組合邏輯電路不同,我們無法僅通過查看輸入來確定時序電路的輸出。時序電路的輸出取決于輸入和時鐘狀態,很難從外部控制和觀測內部觸發器。

因此,除非將時序邏輯電路初始化為已知值,否則無法對其進行測試。為了初始化它們,我們還需要一組特定的功能。DFT使我們能夠將此功能添加到時序電路中,從而使我們能夠對其進行測試。

ii. 優化芯片制造過程

DFT在芯片制造過程中實現了兩個重要目標:

- 拒絕有故障的芯片(品控)

測試會檢查制造過程中的錯誤,這些錯誤會在設計的芯片中產生故障。較早的檢查到故障,則可以將有故障的芯片丟棄,可以節省時間和金錢

- 監控和提高制造能力

芯片在制造過程中會經過很多次測試,如果測試失敗,EDA軟件可以定位到某個具體位置,然后進行切片分析其微觀結構,最終定位到制造過程中。

d. DFT可以永久的消除故障嗎?

測試是否可以保證芯片再也不會出現故障?

不會,芯片到客戶手中,也有可能出現故障。如果芯片暴漏在高溫或潮濕的環境或由于老化而隨時可能出現故障。

舉個例子,如果你有未鎖定的CPU,你可以嘗試超頻,但是請不要這么做!

超頻是一種將系統頻率和電壓提高到額定值以上的方法,配置不正確的超頻可能會干擾時序指標并導致不穩定性。長時間超頻會導致系統過熱并承受壓力,從而縮短計算機的使用壽命。這可能會導致芯片間歇性故障,并在將來造成隨機崩潰。除此之外,它也可能使保修無效。以上例子只是對現實生活中可能發生故障的一種解釋。

關鍵是,您甚至可以自行產生故障,芯片永遠無法抵抗故障。它們總會發生,那么我們需要做些什么?測試設備可以增強我們的信心,通過測試芯片,供應商試圖最大程度地減少將來發生錯誤和故障的可能性。

為了確保高質量的芯片,芯片在設計過程中還涉及一個輔助過程,即為驗證。

2. 驗證和測試的關系

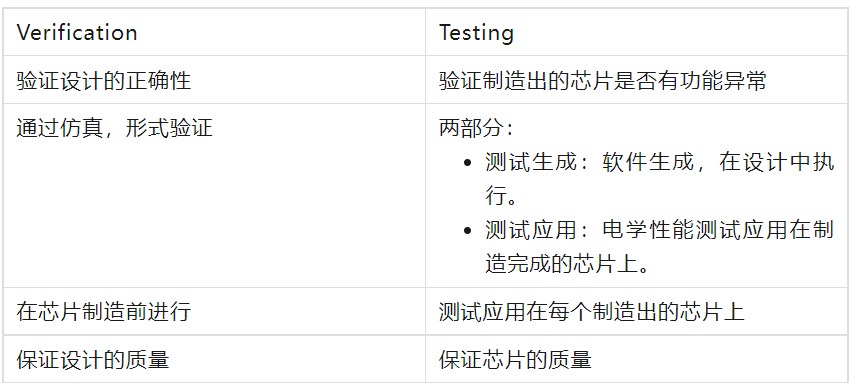

a. 驗證和測試的不同點

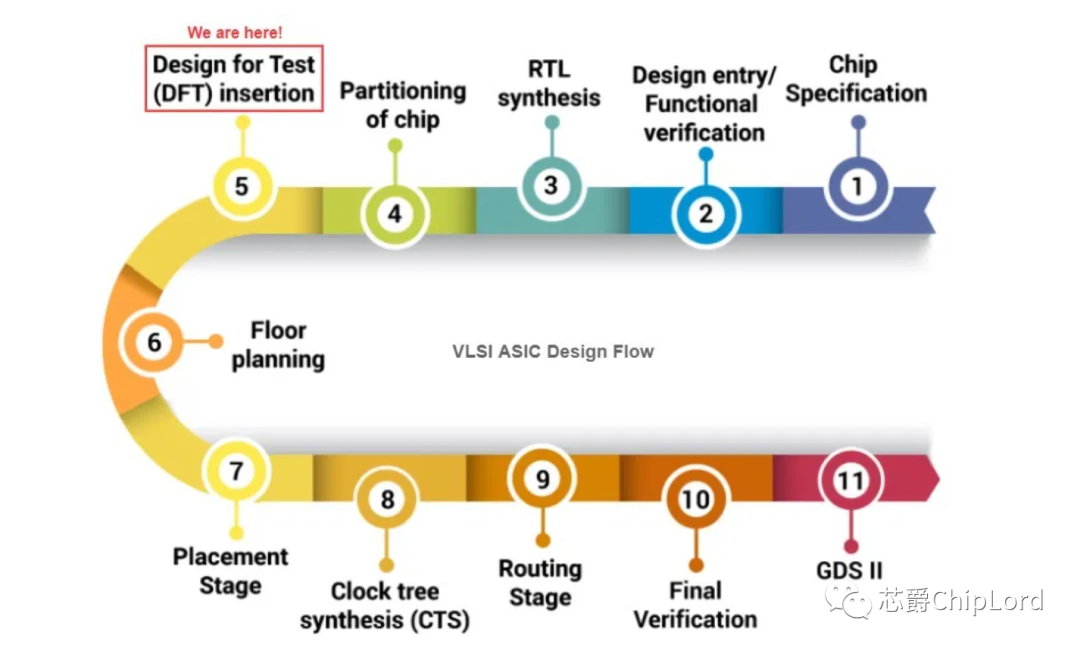

驗證證明設計的正確性和邏輯功能,在使用硬件描述語言(VHDL/Verilog)對RTL設計進行編碼后,即可完成該過程。它是用高級語言編寫testbech來完成的。這僅在芯片實際制造之前執行一次,在設計中,通過system verilog進行驗證,例如UVM。驗證本身是一個單獨的話題,這里不深入討論。

相反,測試試圖在芯片設計過程的每個抽象級別上保證所制造的芯片的正確性。由于在芯片制造和封裝過程中均有可能發生故障,因此需要對每個芯片進行測試。通過測試,我們可以改善市場上出售的芯片的質量。

b. 職業選擇?驗證 vs DFT

讓我們先討論下這兩個職位的工作內容。

驗證和DFT在芯片設計行業中都很重要,從產品開發的角度,這兩者的范圍都很廣,你可以根據自己的興趣愛好,自行選擇。

芯片設計大約2/3的時間用于驗證,從而使其成為VISL設計流程中最耗時的過程,因此與DFT工程師相比,驗證工程師的數量也是很大的,如果你是DFT工程師,那么與驗證團隊相比,團隊規模會小很多。

DFT:

對于DFT,你需要精通CMOS VLSI,數字電路,數字電路測試,Verilog和一些腳本語言,這些技能將在你日常工作中發揮重要作用。你工作中會用到perl,shell和TCL等腳本語言。同時,DFT相關的EDA工具如:DFT compiler,TetraMAX,Tessent等。你將會和后端物理設計工程師和前端設計工程師緊密合作,職業道路,可能更適合后端物理設計,并且必須面對新技術的發展。

驗證:

對于驗證領域,你將從事設計開發和某些高級的testbench的編寫,這需要分析和軟件編程能力,以及硬件技能。需要具有verilog,system verilog,C++的專用知識等。

驗證分為兩個階段:功能驗證和物理驗證。大多數驗證工程師不會直接參與電路設計,晶體管或后端設計部分,主要著眼于前端領域。要成為驗證專家,你需要實際項目經驗。

4. 測試的分類

從等級角度,測試類別可分為:

- Chip-level

- Board-level

- System-level

有一條經驗法則,叫十倍原則,從低級到高級(chip-->board-->system),測試成本要高10倍,如果在不同階段發現芯片失效,損失的代價也是10倍左右。所以我們要盡早發現失效芯片,以減少損失。

5. 芯片失效的來源

下面是一些可能的故障來源:

- 芯片制造,例如contact的短路或開路。

- 材料缺陷,例如基底材料的裂紋或缺陷,表面雜質等。

- 老化損耗,介電擊穿,電子遷移等。

- 封裝過程,接觸點短路或斷路等。

6. 故障的分類

故障可以分成如下類別:

7. DFT技術

DFT技術廣泛的分為如下兩種類型:

Ad-hoc techniques

這些是從設計經驗中學到的芯片設計過程的技術或規則集合,以使設計可測性更容易實現。基本上,這些是在遇到各種錯誤之后隨著時間的推移而收集到的規則。

- Advantage

測試向量易于生成,沒有設計規則約束,并且不會增大面積

- Drawbacks

測試結構不能重復利用,因為每種設計都有其特定的要求和可測性問題。無論使用哪種電路,都無法保證較高的可測性,系統性不足,無法采用統一的方法來進行可測性電路設計。

- Example

以下是一些專用DFT技術必須遵循的規則:大規模電路應劃分為較小的子電路,以降低測試成本。必須插入測試點,以增強電路的可控性和可觀察性,可以通過增加節點數或為要觀察的內部節點多路復用現有的主要輸出來完成。

Structured techniques

在這種技術中,額外的邏輯和信號被添加在電路中,以允許根據一些預定義的過程進行測試。

- Advantage

和專用DFT技術相比,結構化DFT技術意味著無論電路功能如何,始終可以使用相同的設計方法并確保良好的可測性。該技術是解決當今世界DFT問題的唯一解決方案。

- Disadvantage

但是,需要付出一定的代價,通常包括接受一定的設計規則,并且需要承受額外的面接和延遲。

- Example

以下是結構化DFT技術的一些示例,我們后續會詳細介紹。

- scan path

- partial scan

- level sensitive scan

- BIST

- Boundary Scan

8. 總結

本文對VLSI中可測性設計做了簡短介紹,關鍵點在于,IC制造過程很容易出現問題,這些故障可能在經濟上造成更多損失。

-

電路

+關注

關注

172文章

5901瀏覽量

172134 -

控制器

+關注

關注

112文章

16332瀏覽量

177808 -

EDA工具

+關注

關注

4文章

267瀏覽量

31787 -

芯片設計

+關注

關注

15文章

1015瀏覽量

54877 -

eda

+關注

關注

71文章

2755瀏覽量

173201 -

晶體管

+關注

關注

77文章

9682瀏覽量

138080 -

時序電路

+關注

關注

1文章

114瀏覽量

21696 -

DFT

+關注

關注

2文章

231瀏覽量

22712 -

DFT設計

+關注

關注

0文章

10瀏覽量

8881

發布評論請先 登錄

相關推薦

什么是DFT?我們為什么需要它?DFT可以永久的消除故障嗎?

什么是DFT?我們為什么需要它?DFT可以永久的消除故障嗎?

評論