1、什么是Pause幀

Pause幀是一種報文類型。在IEEE802.3協議中規定中,pause幀是一種控制幀,用于控制數據流停止發送,在MAC 發送側產生,在MAC接收側解析并執行。當此端設備輸入數據量過大,無法及時處理時會在此端發送側MAC產生pause幀,發給對端,要求對端在一定時間內停止發送數據。

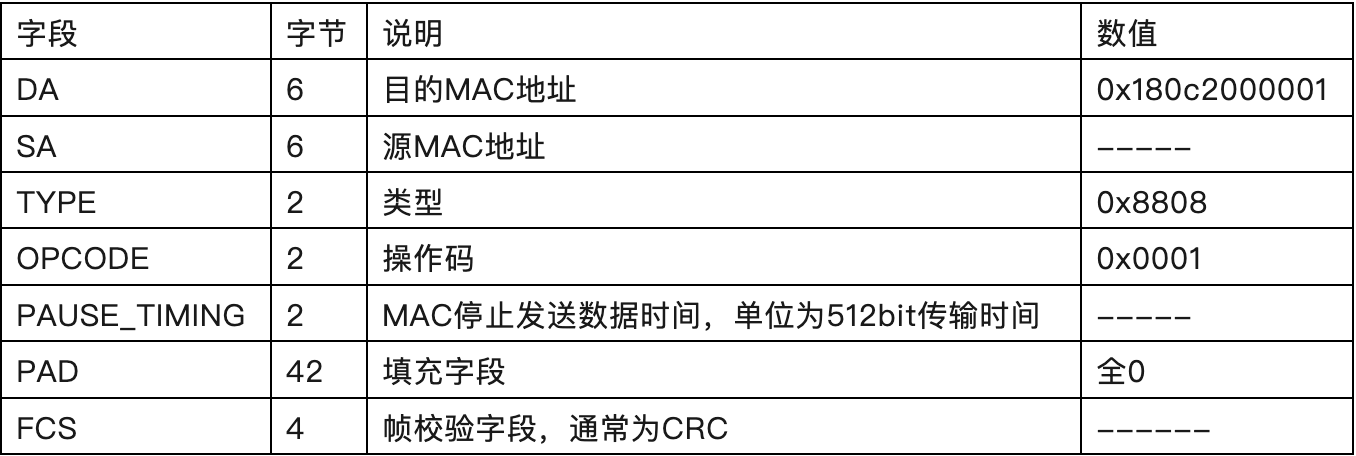

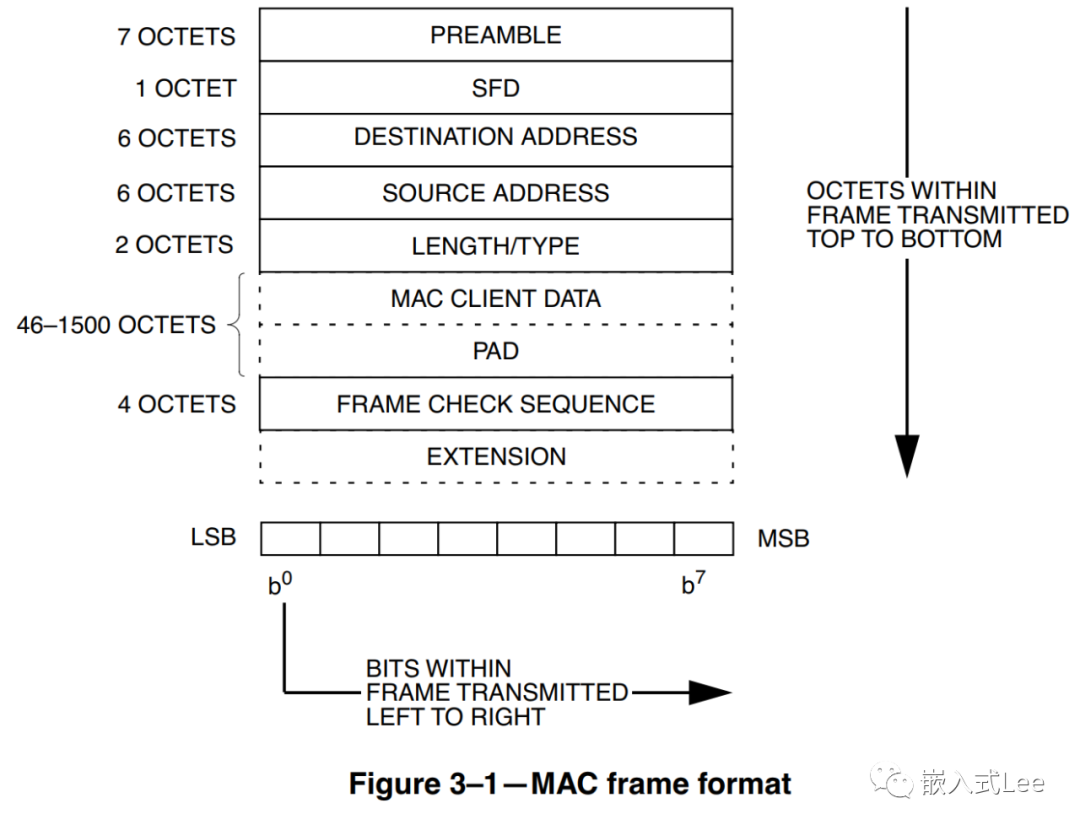

Pause報文由IEEE802.3協議規定,與標準以太幀格式相似:

DA表示目的地址,地址數據固定為0x180c2000001

SA表示源地址 地址由發送方確定

TYPE為報文類型字段,固定為0X8808

OPCODE為操作碼,固定為0X0001

PAUSE_TIMING字段為上游MAC停止發送數據的時間,每單位為512bit傳輸時間,數值為16’d1024表示暫停時間為MAC傳輸1024*512bit數據所需要的時間

PAD:為填充字段,所有值為0

FCS: 為校驗字段,通常為CRC校驗值

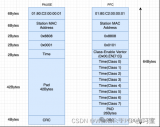

2、Pause幀的流程過程

如圖所示,左側為本端芯片,右側為對端芯片。MAC0和MAC1都包含發送側tx和接收側rx。左側芯片內部mac上游模塊A與mac0發送側有流控信號fc_rdy。信號高表示模塊A無法及時處理輸入數據,需要進行流控。為了方便突出重點,圖中省略了PCS以及serdes等模塊。

流程處理如下:

1~2步:對端mac1發送數據給mac0接收側,進行發送到模塊A

3步:模塊A無法及時處理輸入的數據,需要減少數據輸入,從而將fc_rdy拉高。

4步:mac0發送側tx發現流控信號fc_rdy為高,產生pause幀,發送給mac1接收側。只要fc_rdy為高,mac0發送側tx每隔一段時間發送一個pause幀,間隔時間由配置寄存器控制。間隔時長計算由計數器counting計算。Pause幀內停止發送數據的時間由另外一個配置寄存器控制。只要fc_rdy為高期間,mac0發送側不發送普通數據。

5步:mac1接收側rx接收到pause報文后,提取pause幀內包含的暫停時間,產生流控信號fc通知MAC發送側上游模塊module B停止發送數據

678:mac1 TX側在暫停時間內,停止發送數據。MAC0 TX側可能會發起多個Pause幀。一旦模塊A處理完之前的數據后將fc_rdy拉低,則進入第9步

9:步:第9步分2種情況。

情況1:fc_rdy拉低,并且counting在計數沒有到一個間隔周期,此時發送pause幀,但是幀內暫停時間為0. Mac1接收到pause幀后,控制tx控制立即開始發送數據。

情況2:fc_rdy拉低的同時,counting正好計數到一個間隔周期,此時不發送pause幀。等到上一個pause幀的暫停時間到達后,mac1發送側tx繼續發送數據。

3、pause幀處理協議強制要求

1)pause的產生發送過程不能中斷一個完整的數據報文。即在第4步中,fc_rdy拉高后,首先mac0 tx側需要判斷當前是否正常數據報文在傳輸。如果有,則需要在當前數據報文傳輸完成后才能發送pause幀。也就是說在發送過程中,只能在完整數據報文的間隙插入pause幀。

2)新的pause報文暫停時間會覆蓋上一個暫停時間。對mac1來說,當mac1接收到新的pause幀后,暫停時間以最新時間為準。

-

處理器

+關注

關注

68文章

19547瀏覽量

231868 -

寄存器

+關注

關注

31文章

5392瀏覽量

121924 -

CRC校驗

+關注

關注

0文章

84瀏覽量

15339 -

PCS

+關注

關注

1文章

146瀏覽量

14858 -

MAC控制器

+關注

關注

0文章

6瀏覽量

2649

發布評論請先 登錄

相關推薦

基于Xilinx FPGA的千兆以太網控制器的開發

基于DWC_ether_qos的以太網驅動開發-MAC幀格式介紹

以太網MAC怪異

以太網控制器(MAC)的基本框架怎么搭建

基于FPGA的以太網MAC控制器的設計與實現

工業以太網協議的歷史及其優勢

設置AMD以太網IP核的Pause幀處理

深入探究以太網PAUSE幀處理流程及長距離鏈路控制閾值

什么是Pause幀?以太網MAC的pause流控介紹

什么是Pause幀?以太網MAC的pause流控介紹

評論