隨著現代集成電路工藝的發展,芯片制成越來越來精密,出現缺陷的可能性也越來越高,有時候一個微不足道的影響就可能導致芯片報廢,為了能有效的檢測出生產中出現的廢片,就需要用到掃描鏈測試(scan chain),DFT可測試性設計中的掃描鏈測試發展至今,已經有了成熟的設計和制造流程。本文就對掃描鏈測試過程做簡單介紹。

掃描鏈測試原理

scan chain的基本原理是將設計中所有觸發器連成一條鏈,用統一的scan clk驅動,這樣可以將預先設計好的scan pattern送入芯片中,然后開啟capture使能,這樣每個觸發器Q端輸出傳入它們所驅動的組合電路,scan chain中的下一級觸發器D端就會捕獲這個組合電路的輸出,然后capture失效,這組向量與工具預先計算好的預期相比較,以此為依據來判斷芯片中是否有制造錯誤

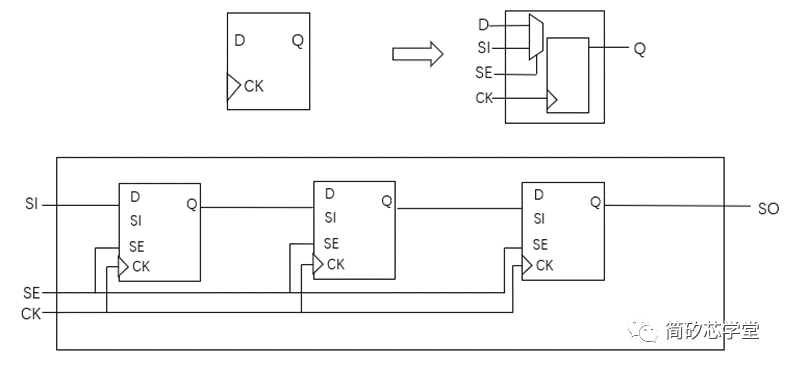

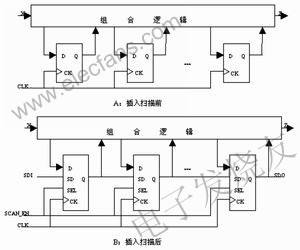

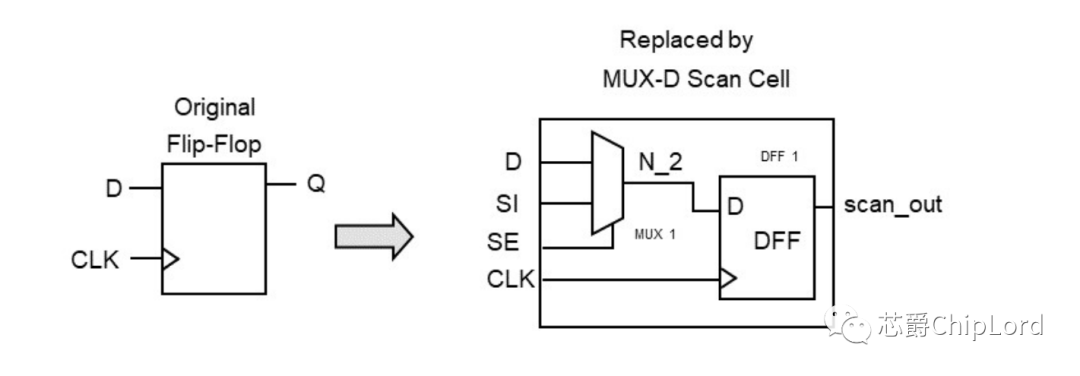

下圖即為scan前和scan后的DFF,這是一個簡單的示意圖,含有三個掃描寄存器。其實就是替換成帶有scan邏輯的DFF,當scan_en有效時,scan邏輯就會從scan-in穿過DFF到達scan-out,多個scan DFF鏈接在一起就成了scan chain,鏈上有多少個scan DFF表示這條鏈的長度。

作為結構性測試(structural test)的主要手段,DFT工程師需要注意的是電路的可測性,也就是可觀測點和可控制點。在運用scan 測試方法的時候,整個芯片被看做是大量的寄存器和寄存器直接連接的組合邏輯。這也就是scan test開發的基本原理。

為了偵測生產過程中的制造缺陷,常用的方法并不是對芯片功能進行測試,而是從元器件最基本的電路反應入手,測試其中的異常,從而偵測到制造缺陷。當然上述是scan chain的基本思想,scan的具體過程在電路中的應用也是相對復雜的,因其橫跨了芯片設計的整個周期,各個角落,在設計scan test的時候需要綜合考慮到芯片設計的方方面面,包括時鐘設計,電源設計,芯片結構,PAD資源,邏輯綜合規劃等。

DFT中的Scan Chain Flow

Scan的工作流程大概分為以下過程:

1、首先是scan insertion(掃描鏈的插入),在芯片功能設計完成后,即為將整個網表由一堆普通寄存器替換為掃描寄存器的過程,這樣新加入的寄存器和原有寄存器一同構成scan chain并參與對芯片的測試;

2、接下來是Test Pattern Generation(測試向量生成過程),測試向量的產生是基于ATPG算法與故障模型以及電路結構生成的,依靠掃描鏈的插入結構生成測試向量,得到測試向量后;

3、即對電路進行門級仿真,類似于驗證芯片功能,當然最后測試向量需要在ATE機臺上針對有限的芯片輸入輸出端口進行測試,盡管上述流程描述相對簡單,但如前文所言在實際應用中要考慮對芯片主線的影響,功耗,面積開銷等問題,這使得該過程變得相對復雜,所以在DFT的工作中,需要對各個因素全面考慮,做到覆蓋率高,功耗低。

Scan Reorder

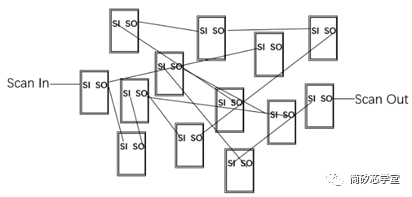

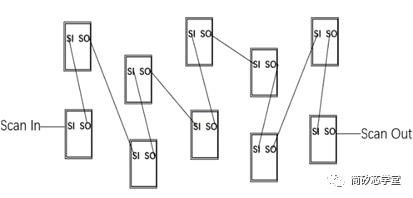

在做完Coarse Placement后,Scan Cell大部分是按照連接的順序隨機的亂放的。這樣其實會極大地占用繞線資源,因此,在后續步驟開始之前,我們需要對掃描鏈的布局布線進行處理,在不影響邏輯功能的前提下,重新進行連接,從而減少走線長度。那這個重組的過程,我們就稱之為掃描鏈重組(Scan Reorder),這個過程可以用下面兩張圖來形象地說明:

在scan插入后會生成后綴為.def文件,后端工程師通過獲取.def文件對scan chain進行Reorder

Scan Reorder之前可以看到每個scan cell的連接是繁瑣雜亂的,被稱為detour,這就需要scan Reorder,在不影響功能邏輯的前提下整理布局布線,得到清晰合理的scan cell連接。

總結

大多數測試生成方案都會將一個被測電路視為一個黑盒子,而對測試機而言,唯一可利用控制端的就是主要輸入端,唯一可用的觀測點就是主要輸出端,因此這就限制了電路的可控性和可觀測性,掃描鏈的機制很好解決這一問題,隨著該技術的發展,測試生成算法,以及其他測試方案也會隨著改進和發展。

-

電源設計

+關注

關注

31文章

1563瀏覽量

67702 -

寄存器

+關注

關注

31文章

5430瀏覽量

123982 -

觸發器

+關注

關注

14文章

2034瀏覽量

62018 -

DFT算法

+關注

關注

0文章

27瀏覽量

7705 -

ATPG

+關注

關注

1文章

6瀏覽量

7687

發布評論請先 登錄

DFT和BIST在SoC設計中的應用

讓你徹底理解DFT

幫你理解DFT中的scan technology

DS26522 JTAG Scan Chain Mappin

DFT掃描設計在控制芯片的測試中的應用

一文讀懂DC/AC SCAN測試技術

DFT分步法原理分析

用全掃描結構(FULL SCAN METHOD)來實現數字電路

怎么配置DFT中常見的MBIST以及SCAN CHAIN

是否需要補插scan chain的isolation cell?怎么插呢?

芯片設計測試中scan和bist的區別

評論