作者:Ki-ill Moon,SK 海力士 PKG 技術開發主管

英特爾聯合創始人戈登摩爾曾預言,芯片上的晶體管數量每隔一到兩年就會增加一倍。由于圖案微型化技術的發展,這一預測被稱為摩爾定律,直到最近才得以實現。然而,摩爾定律可能不再有效,因為技術進步已達到極限,并且由于使用極紫外 (EUV) 光刻系統等昂貴設備而導致成本上升。與此同時,市場對不斷完善的半導體技術的需求仍然很大。為了彌補技術進步方面的差距并滿足半導體市場的需求,出現了一種解決方案:先進的半導體封裝技術。

盡管先進封裝非常復雜并且涉及多種技術,但互連技術仍然是其核心。本文將介紹封裝技術的發展歷程以及 SK 海力士最近在幫助推動該領域發展方面所做的努力和取得的成就。

互連在先進封裝中的重要性

首先,需要注意的是,互連技術是封裝中關鍵且必要的部分。芯片通過封裝互連以接收電力、交換信號并最終進行操作。由于半導體產品的速度、密度和功能根據互連方式而變化,因此互連方法也在不斷變化和發展。

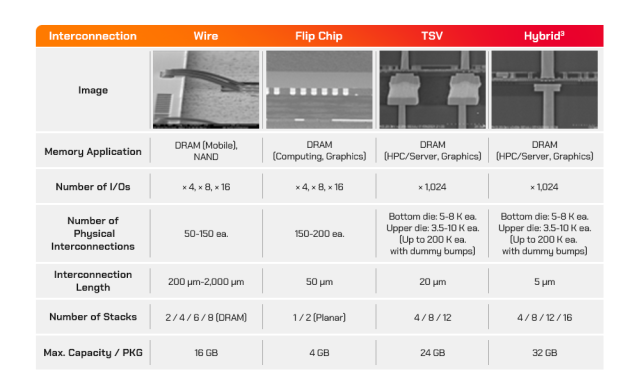

除了開發各種工藝以在晶圓廠實現精細圖案外,還全面努力推進封裝工藝中的互連技術。因此,開發了以下四種類型的互連技術:引線鍵合、倒裝芯片鍵合、硅通孔(TSV) 鍵合以及小芯片混合鍵合。

1硅通孔 (TSV):一種垂直互連通路(通孔),完全穿過硅芯片或晶圓,以實現硅芯片的堆疊。

2 Chiplet:按用途(例如控制器或高速存儲器)劃分芯片并將其制造為單獨的晶圓,然后在封裝過程中重新連接的技術。

3下述產品未采用混合鍵合。規格為估計值。

圖 1. 互連方法規格表。(這些規格是應用每種互連技術的主要產品的示例。)

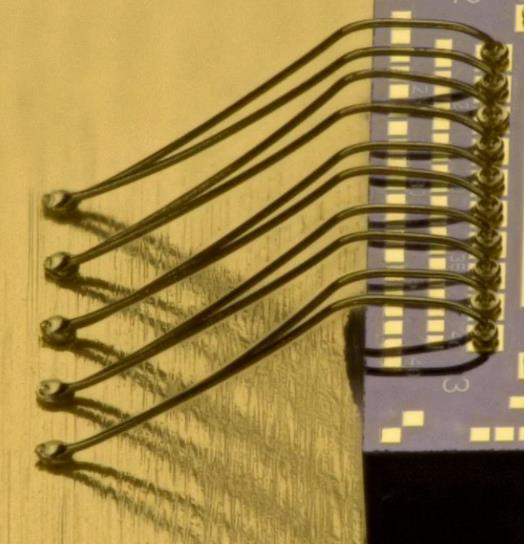

引線鍵合

引線鍵合是第一種開發的互連方法。通常,具有良好電性能的材料(例如金、銀和銅)被用作連接芯片和基板的導線。這是最具成本效益且可靠的互連方法,但由于其電氣路徑較長,因此不適合需要高速操作的較新設備。因此,這種方法被用于不需要快速操作的移動設備中使用的移動 DRAM 和 NAND 芯片。

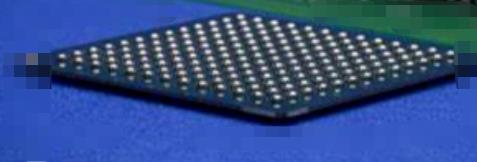

倒裝芯片接合

倒裝芯片接合克服了引線鍵合的缺點。其電氣路徑的長度是引線鍵合的十分之幾,使其適合高速操作。與在芯片級執行的引線鍵合相比,在晶圓級進行處理的倒裝芯片鍵合還提供了卓越的生產率。因此,它被廣泛應用于CPU、GPU和高速DRAM芯片的封裝。此外,由于可以在芯片的整個側面形成凸塊,因此可以比引線鍵合擁有更多的輸入和輸出 (I/O),從而有可能提供更高的數據處理速度。然而,倒裝芯片接合也有其自身的缺點。首先,難以進行多芯片堆疊,這對于需要高密度的存儲產品來說是不利的。此外,盡管倒裝芯片鍵合可以比引線鍵合連接更多的 I/O,和有機 PCB 間距阻止連接更多數量的 I/O。為了克服這些限制,開發了 TSV 鍵合技術。

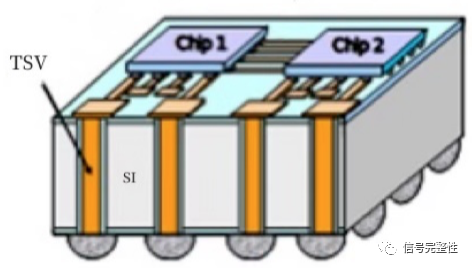

硅通孔 (TSV) 鍵合

TSV不采用傳統的布線方法來連接芯片與芯片,而是通過在芯片上鉆孔并填充金屬等導電材料以容納電極來垂直連接芯片。制作帶有TSV的晶圓后,通過封裝在其頂部和底部形成微凸塊,然后連接這些凸塊。由于 TSV 允許凸塊垂直連接,因此可以實現多芯片堆疊。最初,使用 TSV 接合的堆棧有四層,后來增加到八層。最近,一項技術使得堆疊 12 層成為可能,并于 2023 年 4 月SK hynix 開發了其 12 層 HBM3。雖然 TSV 倒裝芯片接合方法通常使用基于熱壓的非導電薄膜 (TC-NCF),但 SK hynix 使用 MR-MUF 工藝,可以減少堆疊壓力并實現自對準。這些特性使 SK hynix 能夠開發出世界上第一個 12 層 HBM3。

4大規模回流模塑底部填充(MR-MUF):將半導體芯片堆疊起來,并將液體保護材料注入芯片之間的空間,然后硬化以保護芯片和周圍電路的工藝。與在每個芯片堆疊后應用薄膜型材料相比,MR-MUF 是一種更高效的工藝,并提供有效的散熱。

5自對準:在 MR-MUF 工藝期間通過大規模回流將芯片重新定位到正確的位置。在此過程中,熱量被施加到芯片上,導致相關凸塊在正確的位置熔化并硬化。

如上所述,引線、倒裝芯片和 TSV 鍵合在封裝工藝的各個領域中發揮著各自的作用。盡管如此,最近出現了一種新的互連技術,稱為銅對銅直接鍵合,它是混合鍵合的一種。

與小芯片的混合鍵合

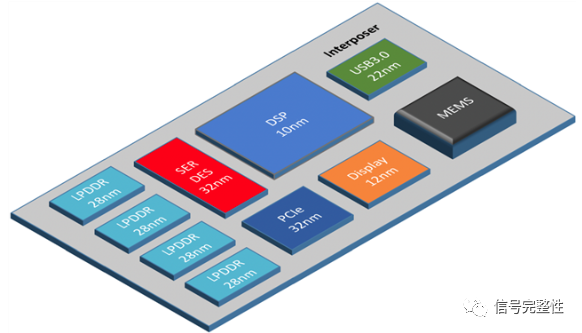

術語“混合”用于表示同時形成兩種類型的界面結合6。界面結合的兩種類型是:氧化物界面之間的結合和銅之間的結合。這項技術并不是新開發的技術,但多年來已經用于 CMOS 圖像傳感器的大規模生產。然而,由于小芯片的使用增加,它最近引起了更多關注。Chiplet技術將各個芯片按功能分離,然后通過封裝將它們重新連接起來,在單個芯片上實現多種功能。

6界面鍵合:相互接觸的兩個物體的表面通過分子間力結合在一起的鍵合。

盡管小芯片的功能是該技術的一個明顯優勢,但采用它們的主要原因是成本效益。當所有功能都在單個芯片上實現時,芯片尺寸會增加,并且不可避免地導致晶圓生產過程中良率的損失。此外,雖然芯片的某些區域可能需要昂貴且復雜的技術,但其他區域可以使用更便宜的傳統技術來完成。因此,由于芯片無法分離,制造工藝變得昂貴,因此即使只有很小的面積需要精細技術,也要將精細技術應用于整個芯片。然而,小芯片技術能夠分離芯片功能,從而可以使用先進或傳統的制造技術,從而節省成本。

雖然chiplet技術的概念已經存在十多年了,但由于缺乏能夠互連芯片的封裝技術的發展,它并沒有被廣泛采用。然而,芯片到晶圓 (C2W) 混合鍵合的最新進展顯著加速了小芯片技術的采用。C2W 混合鍵合具有多種優勢。首先,它允許無焊料鍵合,從而減少鍵合層的厚度、縮短電氣路徑并降低電阻。因此,小芯片可以高速運行而無需任何妥協——就像單個芯片一樣。其次,通過直接將銅與銅接合,可以顯著減小凸塊上的間距。目前,使用焊料時很難實現 10 微米 (μm) 或更小的凸塊間距。然而,銅對銅直接鍵合可以將間距減小到小于一微米,從而提高芯片設計的靈活性。第三,它提供了先進的散熱功能,這一封裝功能在未來只會繼續變得越來越重要。最后,上述的薄粘合層和細間距影響了封裝的形狀因數,因此可以大大減小封裝的尺寸。

然而,與其他鍵合技術一樣,混合鍵合仍然需要克服挑戰。為了確保穩定的質量,必須在納米尺度上改進顆粒控制,而控制粘合層的平整度仍然是一個主要障礙。同時,SK海力士計劃使用最高功率的封裝解決方案來開發混合鍵合,以便將其應用于未來的HBM產品。

利用 SK 海力士的混合鍵合推進封裝技術

雖然SK海力士目前正在開發混合鍵合,以應用于其即將推出的高密度、高堆疊HBM產品,但該公司此前已在2022年成功為HBM2E采用混合鍵合堆疊八層,同時完成電氣測試并確保基本可靠性。這是一項重大壯舉,因為迄今為止大多數混合鍵合都是通過單層鍵合或兩個芯片面對面堆疊來完成的。對于 HBM2E,SK 海力士成功堆疊了 1 個基礎芯片和 8 個 DRAM 芯片。

混合鍵合是封裝行業中最受關注和關注的鍵合技術。集成器件制造商、代工廠以及任何能夠生產先進封裝的公司都專注于混合鍵合。如上所述,盡管該技術具有眾多優勢,但仍有很長的路要走。通過其領先的 HBM技術,SK海力士將開發除混合鍵合之外的各種封裝技術,以幫助封裝技術和平臺解決方案達到前所未有的水平。

-

芯片

+關注

關注

455文章

50714瀏覽量

423137 -

摩爾定律

+關注

關注

4文章

634瀏覽量

78998 -

封裝

+關注

關注

126文章

7873瀏覽量

142893 -

晶體管

+關注

關注

77文章

9682瀏覽量

138080 -

SK海力士

+關注

關注

0文章

958瀏覽量

38475 -

chiplet

+關注

關注

6文章

431瀏覽量

12584

原文標題:SK海力士 :芯片內部的互連技術

文章出處:【微信號:fcsde-sh,微信公眾號:fcsde-sh】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SK海力士 :芯片內部的互連技術

SK海力士 :芯片內部的互連技術

評論