1.1 計(jì)算機(jī)結(jié)構(gòu)

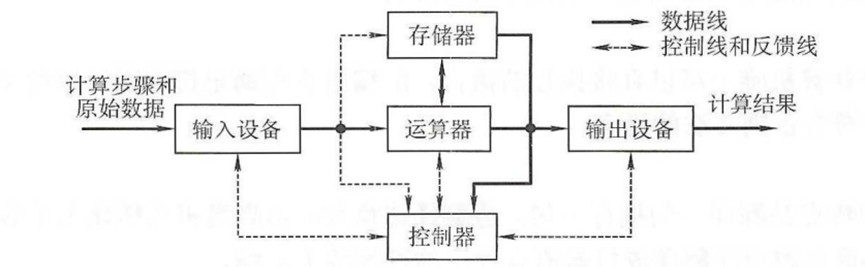

圖1 早期馮·諾依曼計(jì)算機(jī)結(jié)構(gòu)

圖2 以存儲(chǔ)器為中心的計(jì)算結(jié)構(gòu)

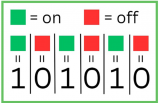

馮·諾依曼為改善早期計(jì)算器手動(dòng)接線來控制計(jì)算的方式,提出了“存儲(chǔ)程序”的概念,將指令以二進(jìn)制代碼的形式事先輸入計(jì)算機(jī)的主存儲(chǔ)器,然后按其在存儲(chǔ)器中的首地址執(zhí)行程序的第一條指令,以后就按該程序的規(guī)定順序執(zhí)行其他指令,直至程序執(zhí)行結(jié)束。早期馮·諾依曼計(jì)算機(jī)結(jié)構(gòu)的特點(diǎn)是以運(yùn)算器作為核心,數(shù)據(jù)的輸入輸出都是由運(yùn)算器進(jìn)行中轉(zhuǎn),為了提高計(jì)算機(jī)的效率,現(xiàn)代計(jì)算機(jī)以存儲(chǔ)器作為核心。

1.2 計(jì)算機(jī)硬件的基本組成

現(xiàn)代計(jì)算機(jī)將運(yùn)算器和控制器集成到一個(gè)芯片上,合成為 中央處理器 ,簡稱 CPU 。

? 運(yùn)算器 ,是計(jì)算機(jī)的運(yùn)算單元,用于算術(shù)運(yùn)算和邏輯運(yùn)算,運(yùn)算器的核心單元是算術(shù)邏輯單元(ALU)

? 控制器 ,控制器是計(jì)算機(jī)的指揮中心,有其指揮各部件自動(dòng)協(xié)調(diào)的進(jìn)行工作

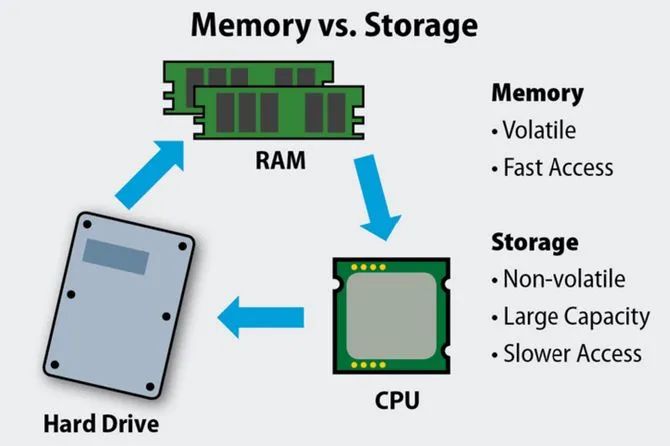

?存儲(chǔ)器分為主存儲(chǔ)器和輔助存儲(chǔ)器

?主存儲(chǔ)器也被成為內(nèi)存儲(chǔ)器,CPU能直接訪問

?輔助存儲(chǔ)器即外存儲(chǔ)器,協(xié)助主存儲(chǔ)器記憶更多的信息,輔助存儲(chǔ)器的信息需要導(dǎo)入到主存儲(chǔ)器中,才可以被CPU訪問

? 輸入設(shè)備 ,是指將外部信息以計(jì)算機(jī)能讀懂的方式輸入進(jìn)來,如鍵盤,鼠標(biāo)等

? 輸出設(shè)備 ,就是將計(jì)算機(jī)處理的信息以人所能接受的方式輸出出來,比如顯示屏,打印機(jī)

CPU包含運(yùn)算器與控制器,控制器通過控制線來告訴運(yùn)算器接下來要進(jìn)行什么樣的運(yùn)算,另外控制器也會(huì)控制主存儲(chǔ)器的讀寫以及輸入輸出設(shè)備的開啟與停止,主存儲(chǔ)器與CPU之間會(huì)進(jìn)行數(shù)據(jù)的交換,數(shù)據(jù)包括需要進(jìn)行基礎(chǔ)運(yùn)算的的數(shù)據(jù)以及指令,這些指令會(huì)放到控制器中來解析這些指令的含義,并且發(fā)出相應(yīng)的控制信號(hào),I/O設(shè)備也會(huì)直接的與主存儲(chǔ)器進(jìn)行數(shù)據(jù)的交換,這大致就是現(xiàn)代計(jì)算機(jī)運(yùn)行的主要步驟。

2.1 中央處理器-CPU

?CPU,即中央處理器,是一臺(tái)計(jì)算機(jī)的運(yùn)算核心和控制核心。其功能主要是解釋計(jì)算機(jī)指令以及處理計(jì)算機(jī)軟件中的數(shù)據(jù)。CPU由運(yùn)算器、控制器、寄存器、高速緩存及實(shí)現(xiàn)它們之間聯(lián)系的數(shù)據(jù)、控制及狀態(tài)的總線構(gòu)成

CPU的主要功能

?指令控制。完成取指令、分析指令和執(zhí)行指令的操作,即程序的順序控制

?操作控制。一條指令的功能往往是由若干操作信號(hào)的組合來實(shí)現(xiàn)的。CPU管理并產(chǎn)生由內(nèi)存取出的每條指令的操作信號(hào),把各種操作信號(hào)送往相應(yīng)的部件從而控制這些部件按指令的要求進(jìn)行動(dòng)作。

?時(shí)間控制。對(duì)各種操作加以時(shí)間控制。時(shí)間控制要為每條指令按時(shí)間順序提供應(yīng)有的控制信號(hào)。

?數(shù)據(jù)加工。對(duì)數(shù)據(jù)進(jìn)行算術(shù)和邏輯運(yùn)算。

?中斷處理。對(duì)計(jì)算機(jī)運(yùn)行過程中出現(xiàn)的異常情況和特殊請(qǐng)求進(jìn)行處理

2.2 運(yùn)算器組成部分

?ALU算術(shù)邏輯單元(Arithmetic&logical Unit) :是中央處理器(CPU)的執(zhí)行單元,是所有中央處理器的核心組成部分,由"And Gate"(與門)和"Or Gate"(或門)構(gòu)成的算術(shù)邏輯單元,主要功能是進(jìn)行二位元的算術(shù)運(yùn)算,如加減乘(不包括整數(shù)除法)。基本上,在所有現(xiàn)代CPU體系結(jié)構(gòu)中,二進(jìn)制都以補(bǔ)碼的形式來表示。

?通用寄存器組:用于存放操作數(shù),包括源操作數(shù)、目的操作數(shù)及中間結(jié)果和各種地址信息等。

?暫存寄存器:用于暫存從主存讀來的數(shù)據(jù),這個(gè)數(shù)據(jù)不能存放在通用寄存器中,否則會(huì)破壞其原有內(nèi)容。

?累加寄存器:它是一個(gè)通用寄存器,用于暫時(shí)存放ALU運(yùn)算的結(jié)果信息,用于實(shí)現(xiàn)加法運(yùn)算。

?程序狀態(tài)字寄存器(PSW):保留由算術(shù)邏輯運(yùn)算指令或測試指令的結(jié)果而建立的各種狀態(tài)信息,如溢出標(biāo)志(OP)、符號(hào)標(biāo)志(SF)、零標(biāo)志(ZF)、進(jìn)位標(biāo)志(CF)等。PSW中的這些位參與并決定微操作的形成。

?移位器:對(duì)運(yùn)算結(jié)果進(jìn)行移位運(yùn)算。

?計(jì)數(shù)器:控制乘除運(yùn)算的操作步數(shù)。

2.3 控制器組成部分

?程序計(jì)數(shù)器( PC ):用于指出下一條指令在主存中的存放地址。CPU就是根據(jù)PC的內(nèi)容去主存中取指令的。因程序中指令通常是順序執(zhí)行的,所以PC有自增功能。

?指令寄存器(IR):存放當(dāng)前需要執(zhí)行的指令,與CPU內(nèi)部總線相連,指令包括操作碼OP和地址碼Ad。

指令譯碼器(ID):通過譯碼器可知當(dāng)前執(zhí)行的是什么指令,輸入信號(hào)為操作碼,輸出信號(hào)為微操作信號(hào),將指令轉(zhuǎn)化為對(duì)應(yīng)微操作。

?微操作信號(hào)發(fā)生器:產(chǎn)生控制整個(gè)計(jì)算機(jī)系統(tǒng)所需的信號(hào),輸入信號(hào)是指令譯碼器的輸出結(jié)果,根據(jù)翻譯后的微操作執(zhí)行具體的微操作。微操作信號(hào)發(fā)生器會(huì)根據(jù)指令譯碼器、時(shí)序系統(tǒng)和標(biāo)志位、PSW寄存器的內(nèi)容執(zhí)行微操作。

?時(shí)序系統(tǒng):用于產(chǎn)生各種時(shí)序信號(hào)。

?存儲(chǔ)器地址寄存器(MAR):用于存儲(chǔ)所要訪問的主存單元的地址,一端連接CPU內(nèi)部總線,一端連接地址總線。

?存儲(chǔ)器數(shù)據(jù)寄存器(MDR):用于存儲(chǔ)向主存寫入的信息或從主存讀出的信息,一端連接CPU內(nèi)部總線,一端連接數(shù)據(jù)總線。

一般將運(yùn)算器和控制器集成到同一個(gè)芯片上,稱為中央處理器(CPU)。CPU和主存儲(chǔ)器共同構(gòu)成主機(jī)。CPU和內(nèi)存之間通過一組總線相連,總線中有地址、控制和數(shù)據(jù)3組信號(hào)線。MAR中的地址信息會(huì)直接送到地址線上,用于指向讀/寫操作的主存存儲(chǔ)單元;控制線中有讀/寫信號(hào)線,指出數(shù)據(jù)是從CPU寫入主存還是從主存讀出到CPU,根據(jù)是讀操作還是寫操作來控制將MDR中的數(shù)據(jù)是直接送到數(shù)據(jù)線上還是將數(shù)據(jù)線上的數(shù)據(jù)接收到MDR中。

3.1 存儲(chǔ)系統(tǒng)-層****次結(jié)構(gòu)

計(jì)算機(jī)的存儲(chǔ)系統(tǒng)根據(jù)層次劃分可分為主存,Cache以及輔存

高速緩沖存儲(chǔ)器(Cache):存放正在執(zhí)行的程序段和數(shù)據(jù);容量小,價(jià)格高,速度快;集成于CPU

主存:存放運(yùn)行期間使用的程序和數(shù)據(jù);容量較小,造價(jià)較高,速度較快;需要由RAM和ROM制作

輔存:存放暫時(shí)不用的數(shù)據(jù)、程序或永久性保存的信息;不能與CPU交換信息,輔存中的內(nèi)容只有調(diào)入主存才可被CPU訪問

主要思想:上一層是下一層的高速緩存,解決速度、容量、成本之間的矛盾

Cache-主存(解決CPU和主存速度不匹配問題):全部由硬件自動(dòng)完成

主存-輔存(解決存儲(chǔ)系統(tǒng)容量問題):將主存與輔存的一部分通過軟/硬結(jié)合的技術(shù)組成虛擬存儲(chǔ)器,他的更新是由硬件和操作系統(tǒng)進(jìn)行控制的

3.2 存儲(chǔ)系統(tǒng)-存儲(chǔ)器分類

?按存儲(chǔ)介質(zhì)分類:

半導(dǎo)體存儲(chǔ)器(如:主存、Cache)、磁表面存儲(chǔ)器(如:磁盤、磁帶以及機(jī)械硬盤等)、光存儲(chǔ)器(如:光盤)

?按存取方式分類:

隨機(jī)存儲(chǔ)器(RAM)(其任何一個(gè)存取單元的內(nèi)容都可隨機(jī)存取,存取時(shí)間與物理位置無關(guān)),順序存取存儲(chǔ)器(SAM)(如:磁帶),直接存取存儲(chǔ)器(DAM)(如:磁盤)(其直接選取信息所在區(qū)域(隨機(jī)存取,在區(qū)域內(nèi)順序查找)),相聯(lián)存儲(chǔ)器(CAM)(如:快表)(他是按照內(nèi)容來檢索物理信息)

?按信息的可讀寫性進(jìn)行分類:

讀/寫存儲(chǔ)器(如:內(nèi)存,硬盤等)(可讀寫),只讀存儲(chǔ)器(ROM)(如:電影使用的光碟)(只可隨機(jī)讀入信息,不可寫入,存取方式為隨機(jī)存取)

?按信息的可保存性進(jìn)行分類:

易失性存儲(chǔ)器(內(nèi)存,Cache),非易失性存儲(chǔ)器(磁盤、光盤)

?按信息讀出后,原信息是否被破壞進(jìn)行分類:

破壞性讀出(如:DRAM芯片),非破壞性讀出(如:SRAM芯片、磁盤、光盤)

3.3 主存儲(chǔ)器-基本組成

主存儲(chǔ)器是由存儲(chǔ)體、MAR和MDR組成的。現(xiàn)代計(jì)算機(jī)的主存由半導(dǎo)體集成電路組成。驅(qū)動(dòng)器、譯碼器和讀寫電路均制作在存儲(chǔ)芯片內(nèi),而MAR和MDR制作在CPU芯片內(nèi)。存儲(chǔ)芯片和CPU芯片可以通過總線連接。

當(dāng)要從主存中讀出某一信息字時(shí),首先由CPU將該字地址送到MAR,經(jīng)地址總線送到主存,然后發(fā)出讀命令。主存接到讀命令之后,得知需要將該地址單元的內(nèi)容讀出,便完成讀操作,將該單元的內(nèi)容讀至數(shù)據(jù)總線上,至于該信息由MDR送到什么地方,由CPU決定。若要向主存存入一個(gè)信息字時(shí),首先CPU將該字所在主存單元的地址經(jīng)MAR送到地址總線,并將該信息字送入MDR,然后向主存發(fā)出寫命令,主存接到寫命令后,便將數(shù)據(jù)線上的信息寫入到對(duì)應(yīng)地址線指出的主存單元中。

4.1 輸入輸出系統(tǒng)(I/O系統(tǒng))

“I/O”就是“輸入/輸出” (Input/Output) I/O 設(shè)備就是可以將數(shù)據(jù)輸入到計(jì)算機(jī),或者可以接收計(jì)算機(jī)輸出數(shù)據(jù)的外部設(shè)備。

輸入設(shè)備:鍵盤,鼠標(biāo)

輸出設(shè)備:顯示器,打印機(jī)

硬盤、光盤:既可輸入、又可輸出的設(shè)備

I/O接口: 又稱I/O控制器( I/O Controller)、設(shè)備控制器,負(fù)責(zé)協(xié)調(diào)主機(jī)與外部設(shè)備之間的數(shù)據(jù)傳輸。

I/O接口多種多樣,也會(huì)制定相應(yīng)的標(biāo)準(zhǔn),如:用于控制USB設(shè)備的I/O接口、用于控制SATA 3.0硬盤的I/O接口等(I/O控制器就是一塊芯片,常被集成在主板上)。

I/O接口與總線之間主要通過設(shè)備選擇線、數(shù)據(jù)線、命令線和狀態(tài)線進(jìn)行連接。

設(shè)備選擇線:用來傳送設(shè)備碼的

數(shù)據(jù)線:是I/O設(shè)備與主機(jī)之間數(shù)據(jù)代碼的傳送線

命令線:主要是用來傳輸CPU向設(shè)備發(fā)出的各種信號(hào)

狀態(tài)線:是將I/O設(shè)備的狀態(tài)向主機(jī)報(bào)告的信號(hào)線

4.2 I/O系統(tǒng)-基本組成

?I/O****硬件

包括外部設(shè)備、I/O接口、I/O總線等。

?I/O****軟件

I/O軟件的主要任務(wù)是,將用戶編制的程序(或數(shù)據(jù))輸入主機(jī)內(nèi);將運(yùn)算結(jié)果輸送給用戶;實(shí)現(xiàn)輸入輸出系統(tǒng)與主機(jī)的協(xié)調(diào)等。通常采用 I/O 指令和通道指令實(shí)現(xiàn) CPU 與I/O設(shè)備的信息交換。

(1)I/O指令 CPU指令的一部分

操作碼+命令碼+設(shè)備碼

(2)通道指令通道能識(shí)別的指令

通道程序提前編制好放在主存中;在含有通道的計(jì)算機(jī)中,CPU執(zhí)行I/O指令對(duì)通道發(fā)出命令,由通道執(zhí)行一系列通道指令,代替CPU對(duì)I/O設(shè)備進(jìn)行管理。

4.3 I/O系統(tǒng)-控制方式

程序查詢方式

CPU不斷輪詢檢查I/O控制器中的“狀態(tài)寄存器”,檢測到狀態(tài)為已完成之后,再從數(shù)據(jù)寄存器取出輸入數(shù)據(jù); 在這種情況下,CPU一旦啟動(dòng)I/O,必須停止現(xiàn)行程序的運(yùn)行,并在現(xiàn)行程序中插入一段程序。

優(yōu)點(diǎn):接口設(shè)計(jì)簡單、設(shè)備量少。

缺點(diǎn):CPU在信息傳送過程中要花費(fèi)很多時(shí)間用于查詢和等待,而且在一段時(shí)間內(nèi)只能和一臺(tái)外設(shè)交換信息,效率大大降低。

程序中斷方式

程序中斷方式引入了中斷機(jī)制,程序中斷是指在計(jì)算機(jī)執(zhí)行現(xiàn)行程序的過程中,出現(xiàn)某些急需處理的異常情況或特殊請(qǐng)求,CPU暫時(shí)中止現(xiàn)行程序,而轉(zhuǎn)去對(duì)這些異常情況或特殊請(qǐng)求進(jìn)行處理。處理完畢后CPU自動(dòng)返回到現(xiàn)行程序的斷點(diǎn)處,繼續(xù)執(zhí)行原程序。

程序中斷方式就是等待鍵盤 I/O時(shí)CPU可以先去執(zhí)行其他程序,鍵盤I/O完成后I/O控制器向CPU發(fā)出中斷請(qǐng)求,CPU響應(yīng)中斷請(qǐng)求,并取走輸入數(shù)據(jù)。

這種方式如果對(duì)于快速 I/O設(shè)備,如“磁盤”,每準(zhǔn)備好一個(gè)字就給CPU發(fā)送一次中斷請(qǐng)求,會(huì)導(dǎo)致CPU需要花大量的時(shí)間來處理中斷服務(wù)程序,CPU利用率嚴(yán)重下降。

DMA****控制方式

主存與高速I/O設(shè)備之間有一條直接數(shù)據(jù)通路(DMA總線)。由于DMA方式傳送數(shù)據(jù)不需要經(jīng)過CPU,因此不必中斷現(xiàn)行程序,I/O與主機(jī)并行工作,程序和傳送并行工作。這種情況下DMA傳送速度快,CPU和外設(shè)并行工作,提高了系統(tǒng)效率。

通道控制方式

有的商用中型機(jī)、大型機(jī)可能會(huì)接上很多的I/0設(shè)備,如果都讓CPU來管理,那么CPU效率過低,這時(shí)就引入了通道控制方式。通道可以理解為是“低級(jí)版的CPU”,可以識(shí)別并執(zhí)行一系列通道指令,通道指令種類、功能通常比較單一,通過IO指令啟動(dòng)通道,通道執(zhí)行通道指令序列,通道程序放在主存中。

-

控制器

+關(guān)注

關(guān)注

113文章

16573瀏覽量

180416 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7553瀏覽量

164909 -

二進(jìn)制

+關(guān)注

關(guān)注

2文章

802瀏覽量

41869 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7575瀏覽量

89100 -

PSW

+關(guān)注

關(guān)注

0文章

9瀏覽量

8287

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

求教計(jì)算機(jī)工作過程

計(jì)算機(jī)的基本組成及工作原理

計(jì)算機(jī)的基本組成和工作原理是什么

計(jì)算機(jī)的工作原理你知道哪些

微型計(jì)算機(jī)的存儲(chǔ)設(shè)備

了解計(jì)算機(jī)硬件體系結(jié)構(gòu)

計(jì)算機(jī)組成原理

計(jì)算機(jī)cpu性能指標(biāo)與作用

簡述計(jì)算機(jī)硬件系統(tǒng)的工作原理及特點(diǎn)

通俗地講解計(jì)算機(jī)工作原理

計(jì)算機(jī)的內(nèi)存和外存別再分不清了

計(jì)算機(jī)存儲(chǔ)系統(tǒng)的工作原理和功能

量子計(jì)算機(jī)與普通計(jì)算機(jī)工作原理的區(qū)別

計(jì)算機(jī)工作原理(CPU、存儲(chǔ)、內(nèi)存、讀寫)

計(jì)算機(jī)工作原理(CPU、存儲(chǔ)、內(nèi)存、讀寫)

評(píng)論