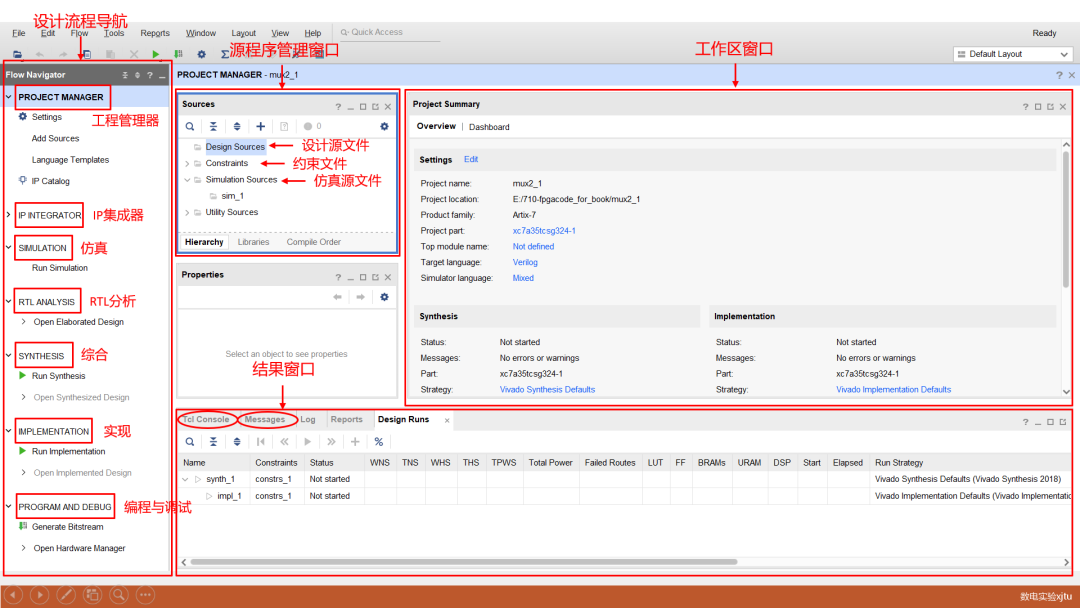

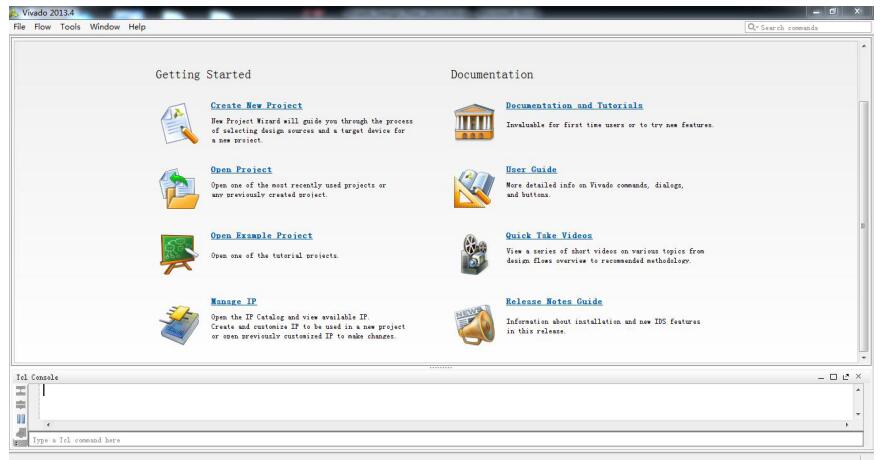

Vivado設(shè)計主界面,它的左邊是設(shè)計流程導(dǎo)航窗口,是按照FPGA的設(shè)計流程設(shè)置的,只要按照導(dǎo)航窗口一項(xiàng)一項(xiàng)往下進(jìn)行,就會完成從設(shè)計輸入到最后下載到開發(fā)板上的整個設(shè)計流程。

源程序管理窗口包含了一個設(shè)計中最基本的三種文件,設(shè)計源文件,約束文件,仿真源文件,如果添加了IP核,這里還會有IP源文件。

工作區(qū)窗口會顯示工程相關(guān)的基本信息,以及我們對系統(tǒng)進(jìn)行的詳細(xì)設(shè)計都在這個窗口完成,例如設(shè)計代碼的輸入,查看綜合實(shí)現(xiàn)結(jié)果、創(chuàng)建Block Design等。

運(yùn)行每一個步驟之后,會在結(jié)果窗口中的Message窗口顯示設(shè)計相關(guān)的所有信息,包括錯誤(error)和警告(warning)提示都會顯示在Message下面。

基于Vivado開發(fā)環(huán)境的設(shè)計流程

1.設(shè)計輸入

在Vivado中可以使用硬件描述語言描述電路,也可以通過IP集成器創(chuàng)建圖形化工程。

在設(shè)計流程導(dǎo)航窗口(Flew Navigator)中,“Settings”可以進(jìn)行vivado工具使用相關(guān)的常用設(shè)置,"Add Sources"可以添加或創(chuàng)建設(shè)計文件。"Language Templates"是語言模板,提供了一些硬件描述語言的常用設(shè)計的寫法。“IP Catalog”可以打開IP目錄,里面包含了Xilinx提供的IP核以及用戶自己設(shè)計的IP核等。

IP集成器(IP INTEGRATOR)可以創(chuàng)建一個Block Design,可以將IP核,或HDL module以圖形化的方式添加到圖形化界面中,再通過端口的互聯(lián),像搭積木一樣完成一些復(fù)雜的設(shè)計。

2.仿真(Simulation)

設(shè)計輸入完成之后,需要進(jìn)行仿真,這里可以進(jìn)行功能仿真,也可以進(jìn)行時序仿真,時序仿真就是考慮了走線時延及器件延遲的仿真。

3.RTL分析

RTL(寄存器傳輸級)分析會生成RTL原理圖,可以對設(shè)計進(jìn)行邏輯和功能檢查。因?yàn)槭褂肏DL描述設(shè)計時可能出現(xiàn)語法或邏輯上的錯誤,一般語法錯誤Vivado會自動檢測和提示,而邏輯錯誤軟件沒有明顯提示,可以使用RTL分析進(jìn)行檢查。

4.綜合(Synthesis)

綜合是將較高層次的邏輯設(shè)計代碼或原理圖等設(shè)計輸入轉(zhuǎn)化為較低層次的由FPGA芯片中底層基本單元表示的電路網(wǎng)表。

5實(shí)現(xiàn)(Implementation)

綜合之后要進(jìn)行實(shí)現(xiàn),實(shí)現(xiàn)是將綜合后的電路網(wǎng)表針對具體指定器件以及相關(guān)物理與性能約束進(jìn)行優(yōu)化、布局、布線的過程。

因此,在實(shí)現(xiàn)前還要添加約束文件,將設(shè)計的端口對應(yīng)到具體的FPGA引腳上,還要根據(jù)板卡指定引腳供電電壓等,此外,還要針對性能要求進(jìn)行相關(guān)時序約束,保證時序收斂,作為FPGA入門,我們暫不考慮時序約束。

6.編程與調(diào)試(Program and Debug)

在這一步可以生成可配置文件,也就是將實(shí)現(xiàn)產(chǎn)生的網(wǎng)表文件轉(zhuǎn)化為可下載到FPGA中的比特流文件,完成對FPGA的配置。

源程序管理窗口

源程序管理窗口包含了一個設(shè)計中最基本的三種文件,設(shè)計源文件,約束文件,仿真源文件,如果添加了IP核,這里還會有IP源文件。

工作區(qū)窗口

工作區(qū)窗口會顯示工程相關(guān)的基本信息,以及我們對系統(tǒng)進(jìn)行的詳細(xì)設(shè)計都在這個窗口完成,例如設(shè)計代碼的輸入,查看綜合實(shí)現(xiàn)結(jié)果、創(chuàng)建Block Design等。

結(jié)果窗口

Tcl console可以使用Tcl命令完成Vivado所有的操作。

Message會顯示設(shè)計相關(guān)的所有信息,包括錯誤(error)和警告(warning)提示都會顯示在message下面,其它的窗口目前階段我們不常用,就不多做介紹了。

-

FPGA設(shè)計

+關(guān)注

關(guān)注

9文章

428瀏覽量

27316 -

寄存器

+關(guān)注

關(guān)注

31文章

5433瀏覽量

124267 -

TCL

+關(guān)注

關(guān)注

11文章

1782瀏覽量

89882 -

Vivado

+關(guān)注

關(guān)注

19文章

834瀏覽量

68656 -

HDL語言

+關(guān)注

關(guān)注

0文章

48瀏覽量

9154

發(fā)布評論請先 登錄

FPGA入門開發(fā)完整流程(Vivado2020+Verilog)精選資料分享

基于microblaze的vivado開發(fā)流程

用 TCL 定制 Vivado 設(shè)計實(shí)現(xiàn)流程

Vivado設(shè)計流程指導(dǎo)手冊

Vivado設(shè)計之Tcl定制化的實(shí)現(xiàn)流程

Vivado綜合引擎的增量綜合流程

一起體驗(yàn)Vivado 的ECO流程

Vivado設(shè)計流程指導(dǎo)手冊

Vivado設(shè)計流程指導(dǎo)說明

關(guān)于Vivado non-project模式

Xilinx FPGA Vivado開發(fā)流程介紹

用TCL定制Vivado設(shè)計實(shí)現(xiàn)流程

vivado創(chuàng)建工程流程

Vivado設(shè)計套件用戶指南(設(shè)計流程概述)

評論