設計任務

在EGO1開發板上實現2選1多路選擇器。

設計分析

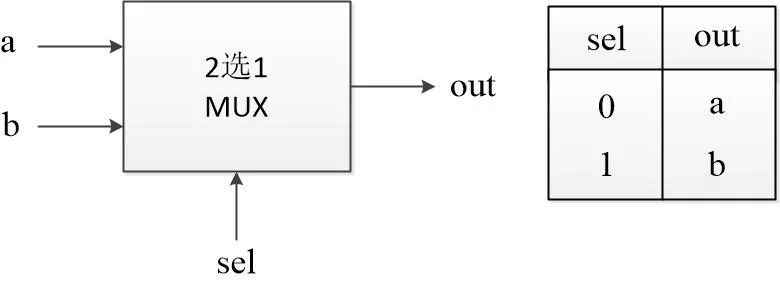

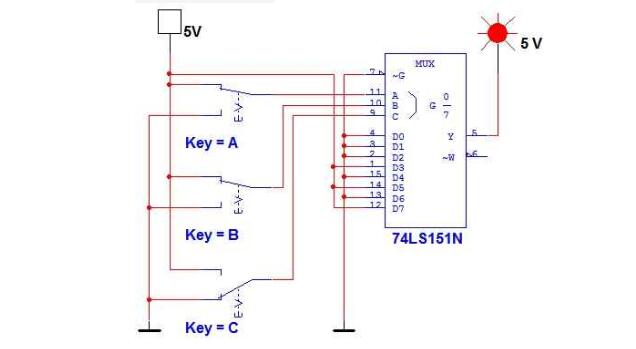

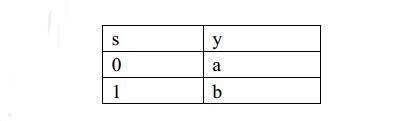

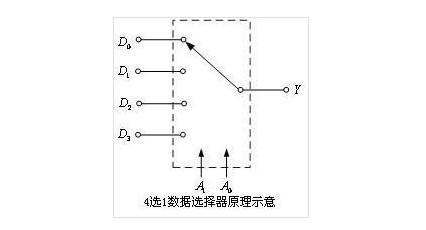

(1)設計電路邏輯關系如下圖,明確輸入、輸出信號。

▲ 2選1多路選擇器

(2)確定信號與FPGA引腳關系。(將在第6步添加設計約束中用到)

根據絲印標識可知如下對應關系。(可參考硬件原理圖或EGO1用戶手冊)

a→P4 //SW6

b→P5 //SW7

sel→R1 //SW0

out→F6 //LD2-7

設計流程

1. 創建FPGA設計工程

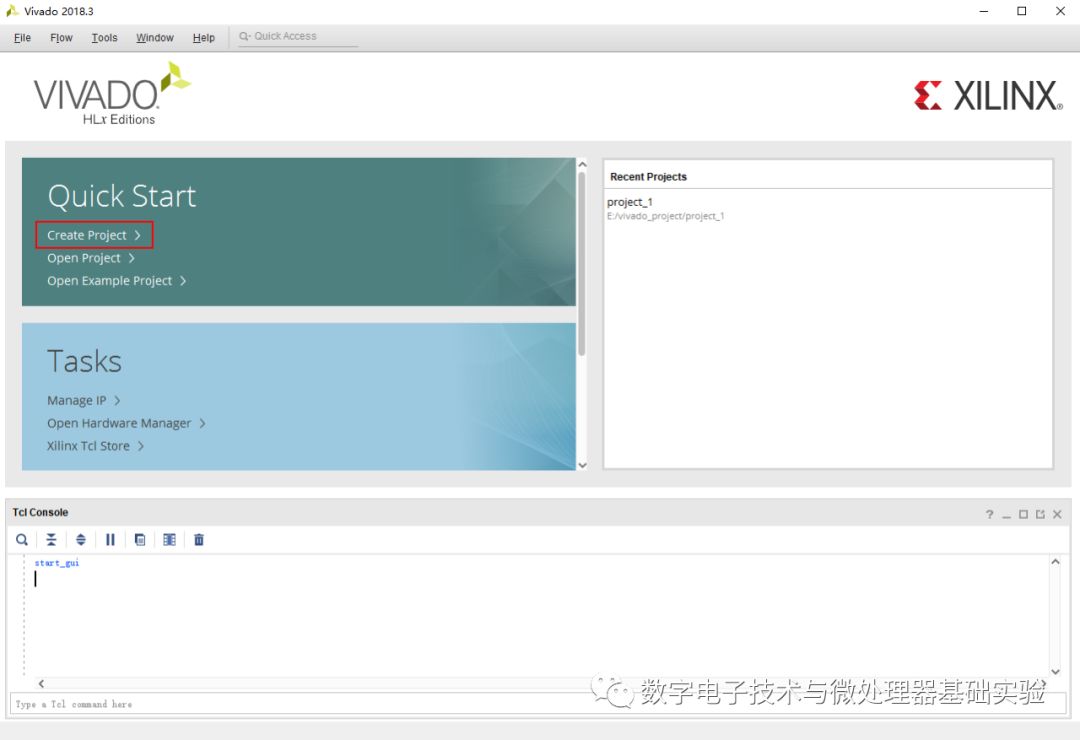

(1)雙擊桌面圖標啟動vivado。

(2)創建一個FPGA工程。

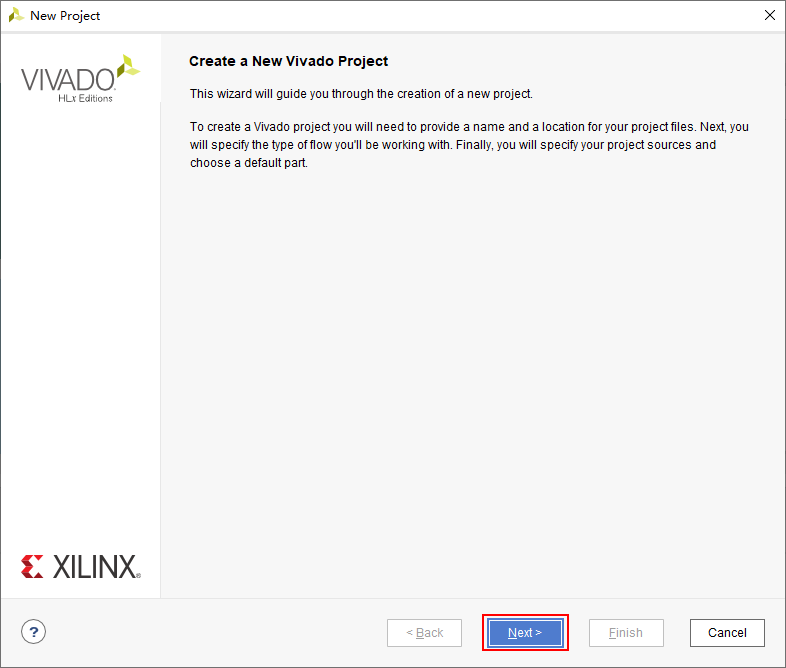

(3)進入新建工程向導。

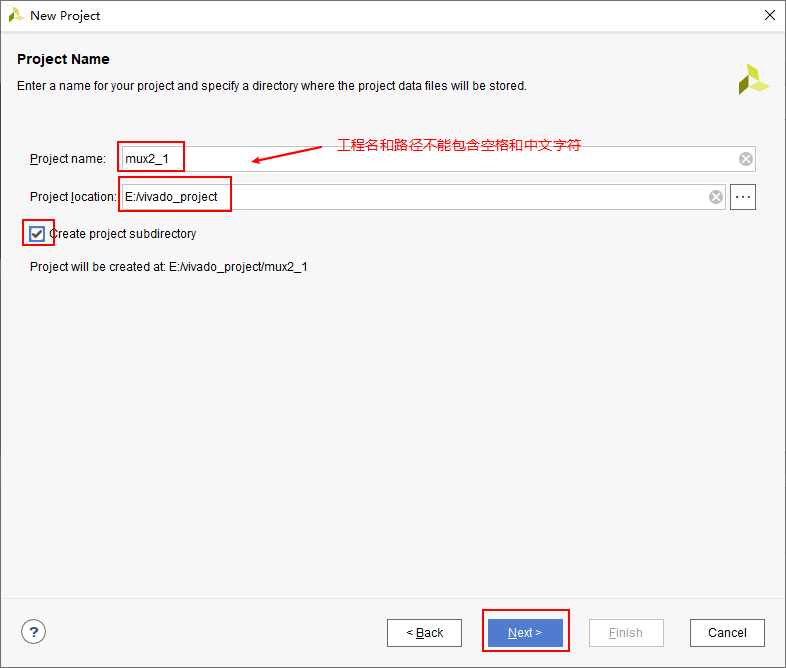

(4)填寫工程名稱和路徑,選擇“Create project subdirectory”。

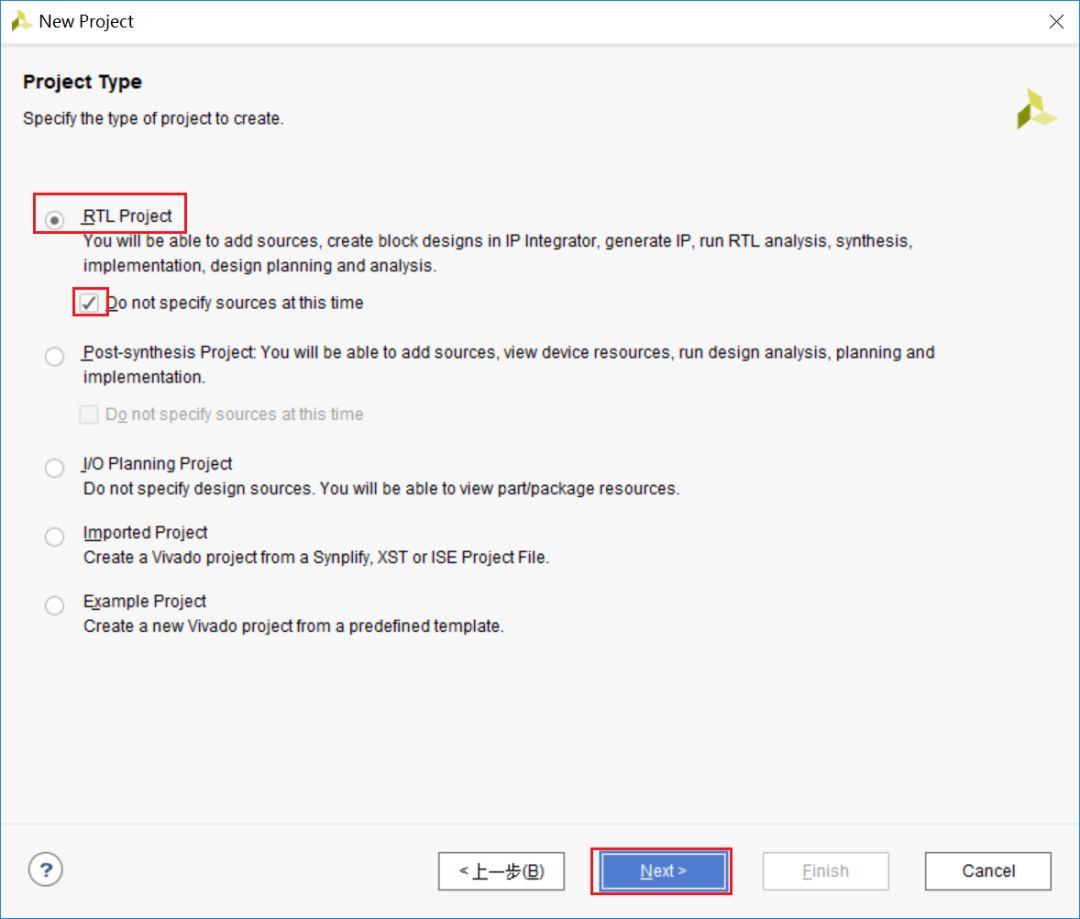

(5)選擇創建“RTL Project”。勾選復選框“Do not specify sources at this time”(不在當前階段創建源程序)。

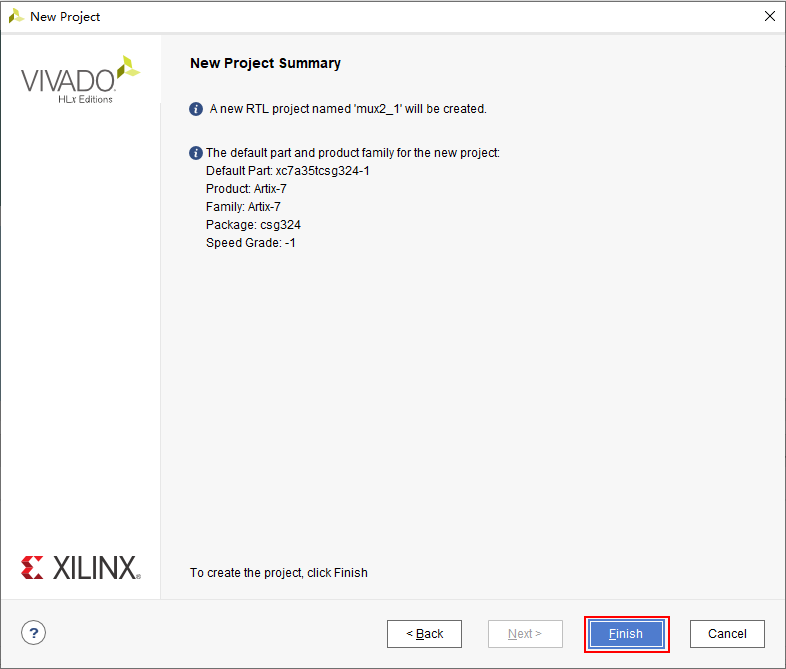

(6)選擇設計所用的具體FPGA型號,可以根據器件系列,封裝,速度等級以及溫度級別進行篩選,也可以直接填入器件型號進行搜索。EGO1開發板所用芯片為Xilinx公司的 xc7a35tcsg324-1 ,屬于Artix-7系列,封裝為csg324,速度等級為-1。

(7)工程信息概覽,單擊“Finish”,完成工程創建。

2. 添加源文件

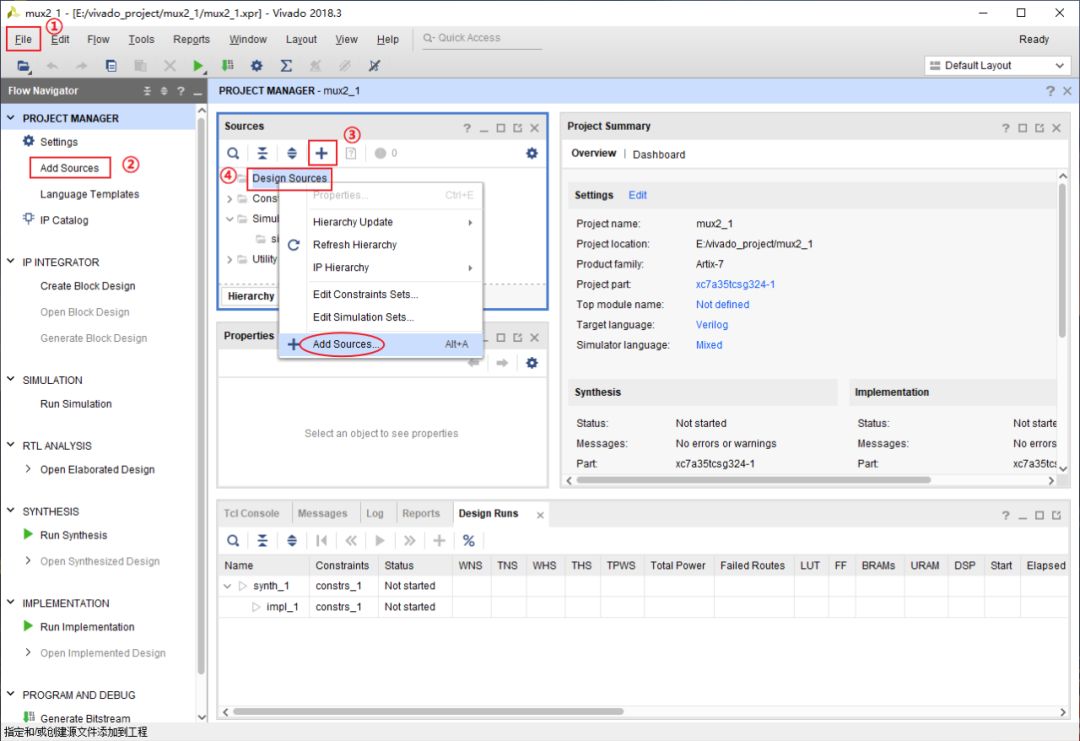

(1)有四種方式可以打開源程序添加窗口。

可以創建約束文件,設計源文件和仿真文件。這里選擇創建設計源文件Add or create design sources。

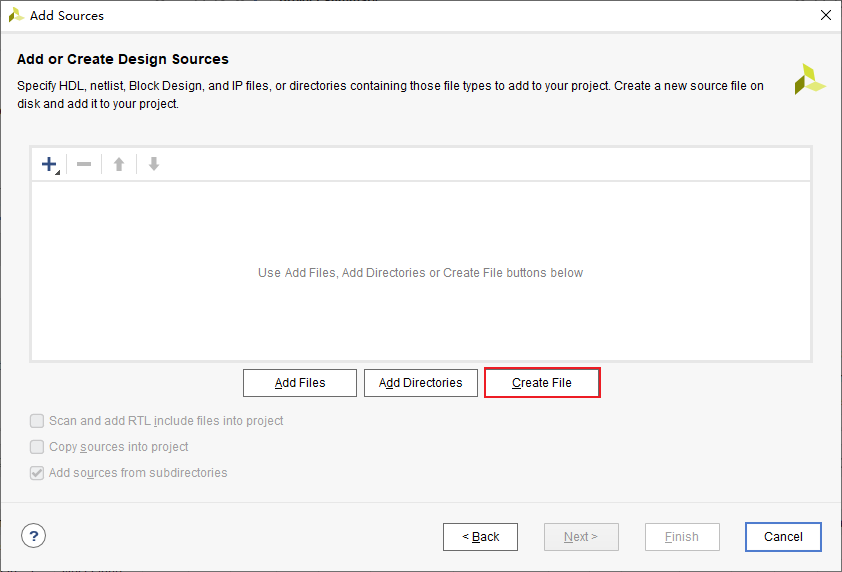

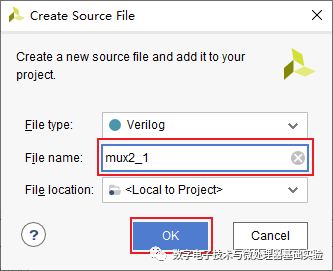

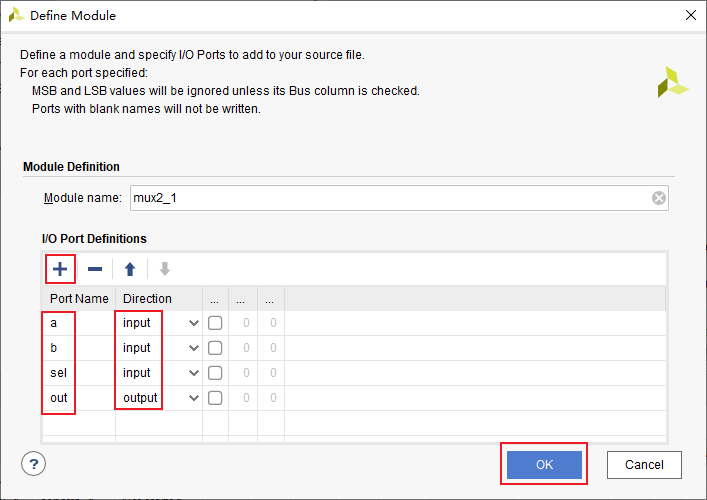

(2)選擇“Create File”,彈出對話框中輸入文件名“mux2_1”。

(3)模塊端口定義,可以添加模塊的端口信號。也可以選擇不添加,待后續直接在源程序界面輸入程序。

設計主界面中sources窗口下出現了如下圖所示的mux2_1.v源程序文件,雙擊打開文件,添加代碼。

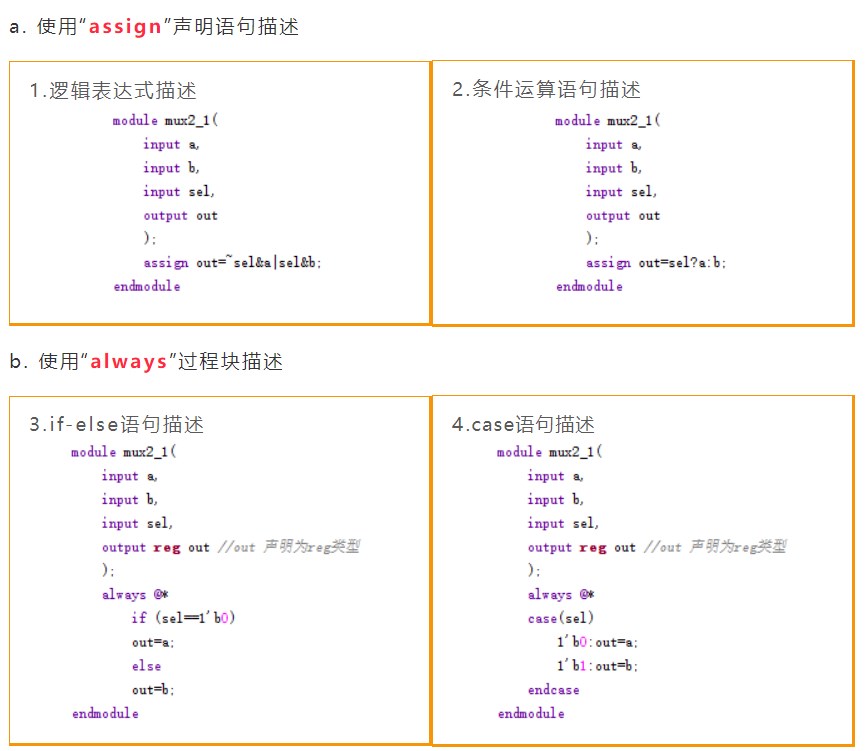

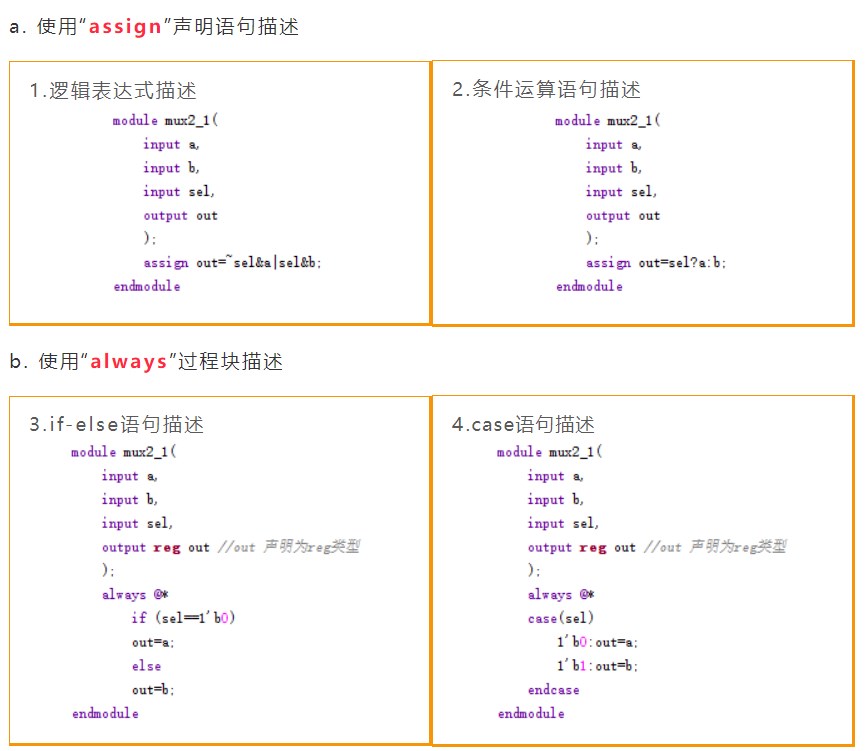

(4)添加Verilog HDL描述。對同一個電路可以有多種描述方式,以下給大家提供了2類主要功能定義的方法,4種不同的語句描述。請選擇1種添加到源程序中。

(5)編輯完成后,保存源文件。

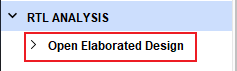

3. RTL分析

用Verilog語言描述電路的時候,可能出現語法或邏輯上的錯誤。一般語法錯誤在編寫程序的過程中,vivado會自動檢測并在程序界面中有所提示,在Messages中也會提示“Error”。對于邏輯錯誤軟件是不會提示的,最多在Messages中的“Warning”提示中找到一些蛛絲馬跡。而設計者可以利用RTL分析進行邏輯和功能檢查。

(1)點擊左側流程向導欄(Flow Navigator)中的“Open Elaborated Design”,彈出提示框,點“OK”。

(2)RTL原理圖查看。下圖即打開的RTL原理圖。該原理圖是根據HDL描述生成的,可以根據原理圖檢查設計是否符合要求。

4.行為仿真

檢驗設計是否滿足功能要求。如果直接在FPGA芯片上測試,可能因為多次綜合、實現而浪費時間。

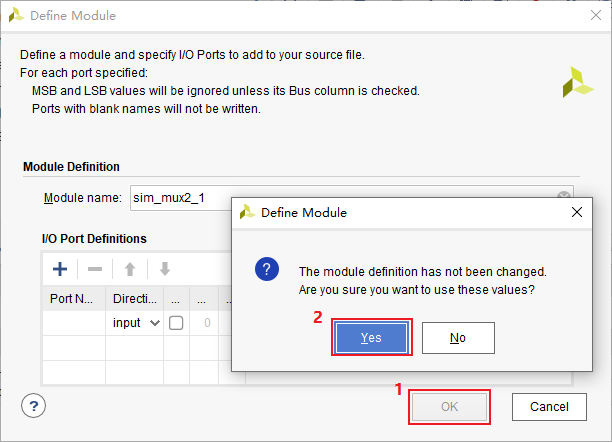

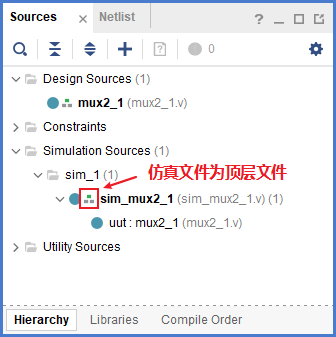

(1)創建仿真文件sim_mux2_1.v。添加方法與添加源程序方法相同,但選擇的是Add or Create Simulation Sources選項。

(2)按下圖操作,直接點擊“OK”→“Yes”,不添加端口定義。

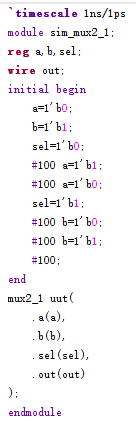

(3)sources窗口中雙擊打開仿真文件sim_mux2_1.v,輸入代碼。這里提供兩種測試代碼供大家參考比較。

參考代碼a:

參考代碼b:

(4)保存。保存文件后,sim_mux2_1.v自動變成頂層文件(品字形圖標標識),否則,右鍵選擇“Set as Top”。mux2_1.v為下層模塊,模塊名為uut。

(5)運行仿真。單擊左側Flow Navigator中Run Simulation,選擇Run Behavioral Simulation。

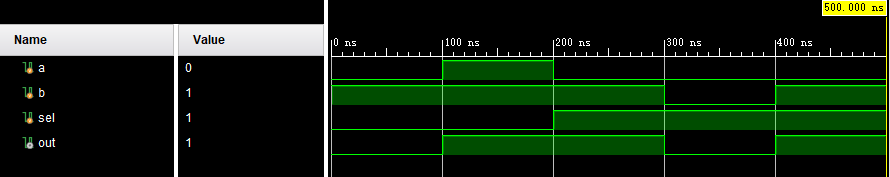

(6)觀察仿真波形。

代碼a仿真結果:

代碼b仿真結果:

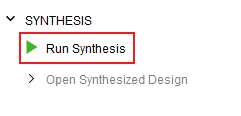

5.設計綜合

綜合: 將較高層次邏輯設計代碼或原理圖等設計輸入轉化為較低層次的由FPGA芯片中底層基本單元表示的電路網表。

(1)單擊左側Flow Navigator中的Run Synthesis。

綜合運行時,在軟件右上角會顯示當前狀態,如下圖所示。

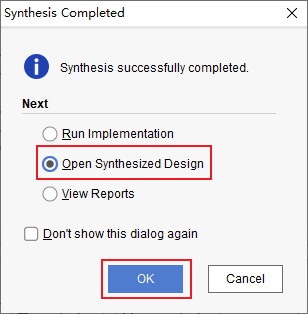

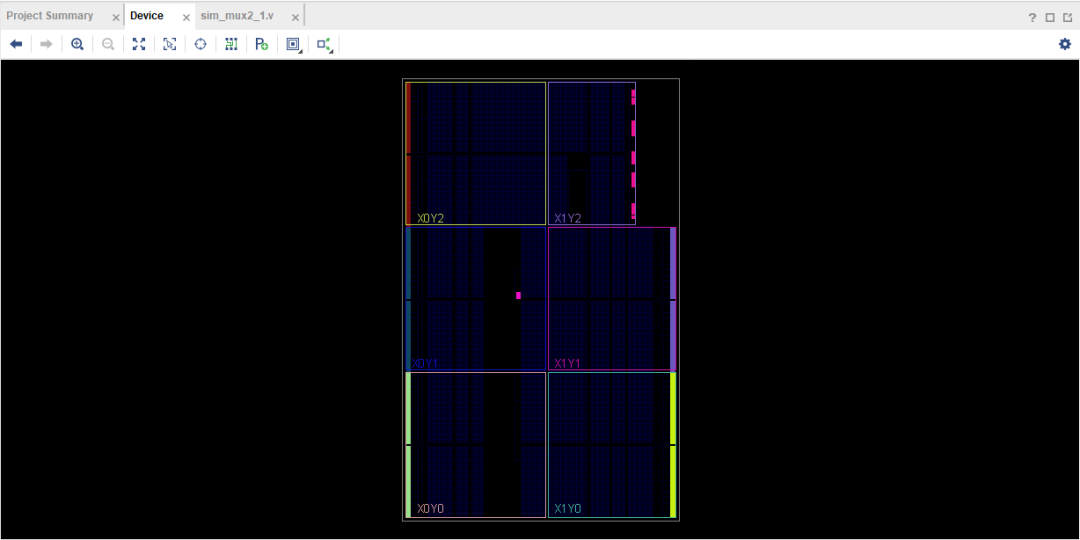

(2)運行完畢,彈出對話框,選擇Open Synthesized Design,會自動打開Device窗口,顯示的是芯片內部構架。

▲ Artix-7 FPGA器件的內部結構圖

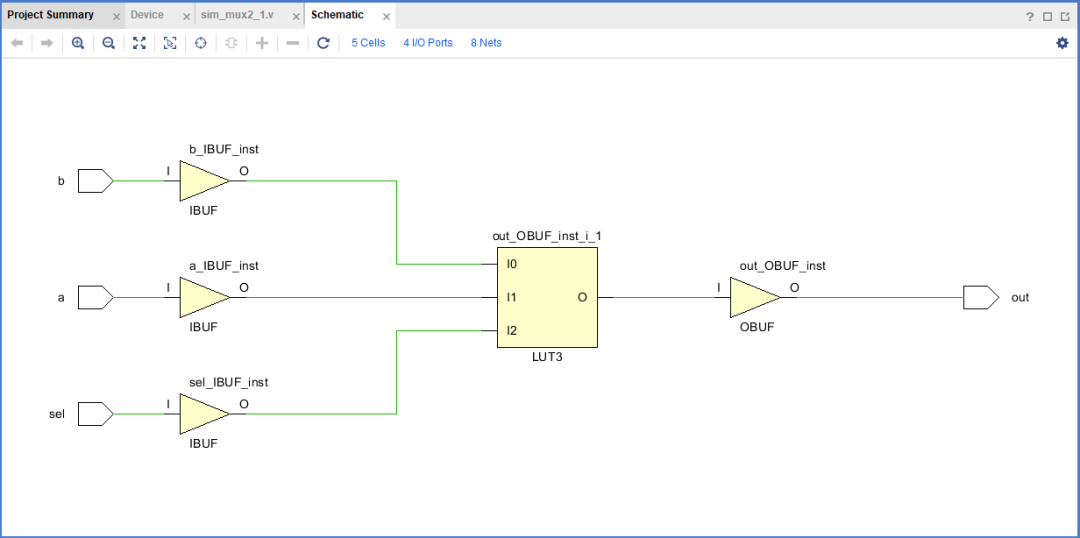

(3)打開Schematic,可以看到綜合后的原理圖,采用的是FPGA中基本單元搭建的,如本實驗使用了一個LUT3查找表。

(4)在Sources窗口下方Cell Properties窗口中,選擇Truth Table,可以看到邏輯表達式和真值表。

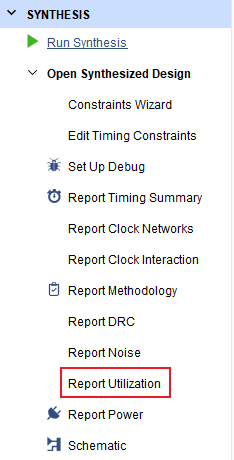

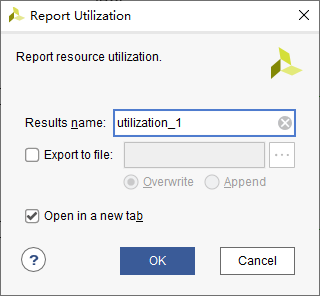

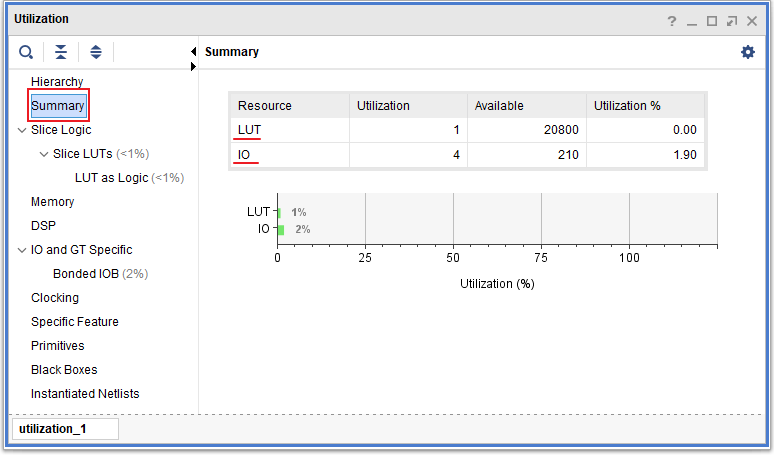

(5)單擊Report Utilization,可以查看當前設計的資源利用率的詳細報告。

可以看到本設計使用了 1個LUT ,總共20800個,利用率小于0.01%; 4個I/O ,總共120個,利用率為1.90%。

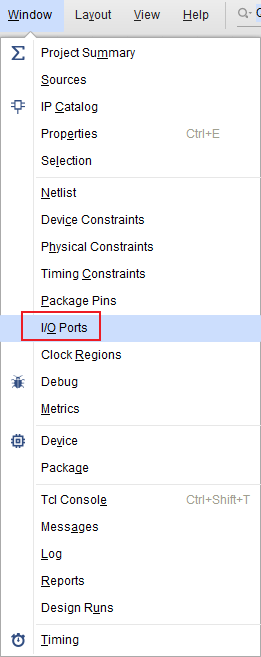

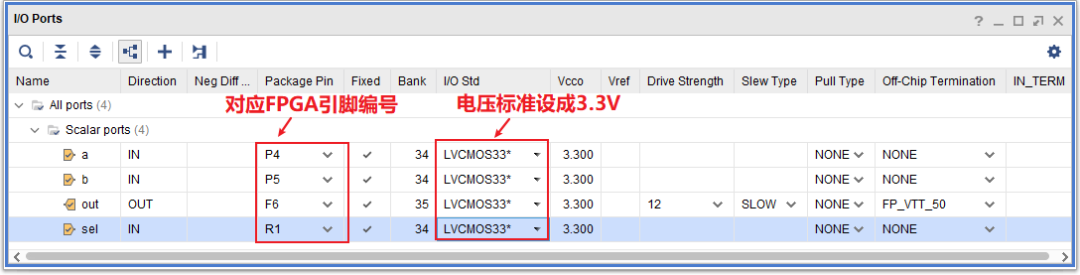

6.添加設計約束

(1)在Window下拉菜單中選擇I/O Ports。

(2)按照下圖修改電壓標準,添加端口對應的FPGA引腳編號。

(3)保存。Sources視圖中可以看到Constraints目錄下生成的mux2_1.xdc文件。打開可以看到自動生成的約束代碼,如下圖所示:

(4)在Window下拉菜單中選擇Package,可以打開I/O規劃視圖,如下圖所示。可以看到設計所占用的FPGA引腳分布(圖中用紅色圓圈標識)。

添加約束的快捷方式:新建空白約束文件,打開EGO1官方提供的約束文件“EGo1.xdc”,選擇相應的約束語句,直接拷貝,并修改端口名稱即可。

7.設計實現

實現: 將綜合后的電路網表針對具體指定器件以及相關物理與性能約束進行優化、布局、布線并生成最終可以下載到FPGA芯片內的配置文件的過程。

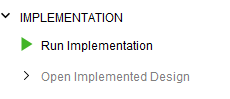

(1)單擊左側Flow Navigator中的Run Implementation。

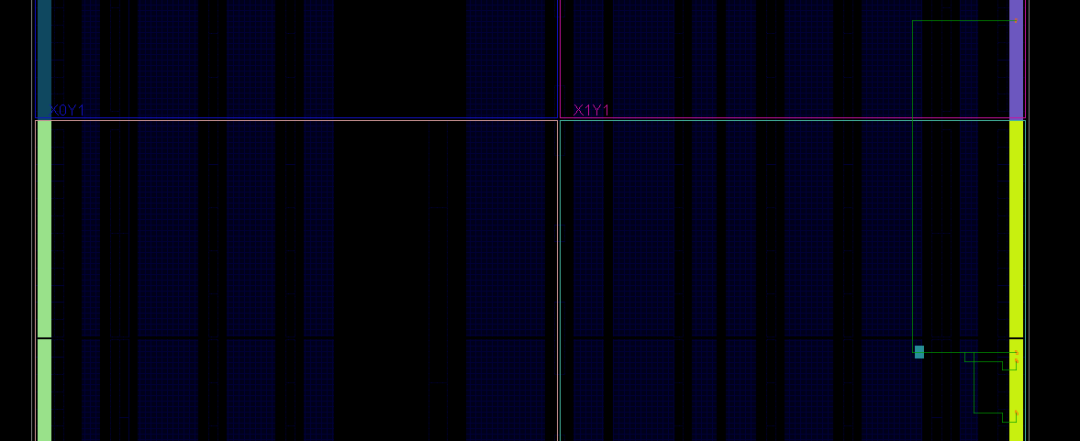

(2)實現過程結束后彈出對話框,可以選擇Open Implemented Design,也可以選擇Generate Bitstream(生成配置FPGA的比特流文件)。這里選擇Open Implemented Design。

可以看到在器件結構圖中設計所用到的器件,如圖中紅色圓圈標識部分,可以放大查看。

點擊工具欄中布線圖標,放大視圖,可以看到器件之間的連線(圖中綠色部分)。

8.時序仿真

時序仿真: 之前的行為仿真是功能仿真,并未涉及毛刺、競爭冒險等時序問題。實現執行后器件完成了布局布線,在此階段后的仿真可得到各種時序所導致的延時問題。

(1)單擊Run Simulation,在浮動菜單中單擊Run Post-Implementation Timing Simulation。

(2)仿真波形如下,調整波形,可以觀察信號延時。下圖中,輸入信號a在100ns處由0變為1,而輸出信號out在108.590ns處才發生變化,時延約8.6ns。

9.比特流文件的生成與下載

(1)實現結束后直接選擇Generate Bitstream,或單擊左側Flow Navigator中Generate Bitstream。

(2)將開發板與電腦連接,并確保電源開關打開。點擊Open target,單擊Auto Connect。

(3)點擊Program device,在出現的對話框中直接點擊Program,比特流文件就配置到器件中了。

10.實驗現象觀察

將SW0置0,撥動SW6,則最左側LED燈隨SW6的狀態變化;將SW0置1,則LED燈隨SW7的狀態變化。

-

RTL

+關注

關注

1文章

385瀏覽量

59763 -

FPGA芯片

+關注

關注

3文章

246瀏覽量

39795 -

時序仿真

+關注

關注

0文章

14瀏覽量

7411 -

HDL語言

+關注

關注

0文章

47瀏覽量

8913 -

多路選擇器

+關注

關注

1文章

22瀏覽量

6524

發布評論請先 登錄

相關推薦

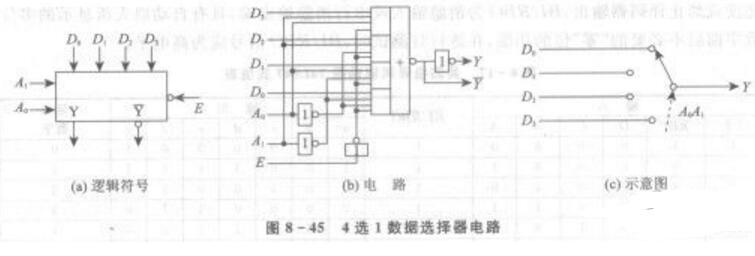

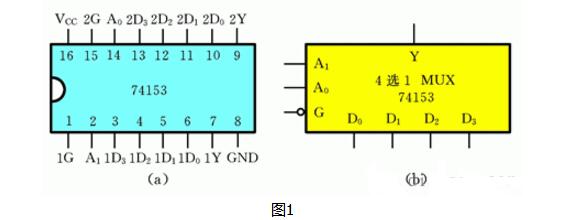

EDA四選一多路選擇器的設計

8選1多路選擇器電路圖(五款8選1多路選擇器電路)

Verilog HDL之多路選擇器設計

使用Verilog語言實現持續賦值方式定義2選1多路選擇器的程序

使用Verilog語言實現持續賦值方式定義2選1多路選擇器的程序

Verilog數字系統設計——簡單組合邏輯2(4選1多路選擇器)

教你學Vivado—以2選1多路選擇器為例

教你學Vivado—以2選1多路選擇器為例

評論