0****1

時(shí)序邏輯電路設(shè)計(jì)方法

時(shí)序邏輯電路的特點(diǎn)是輸出信號不僅與電路的輸入有關(guān),還與電路原來的狀態(tài)有關(guān)。

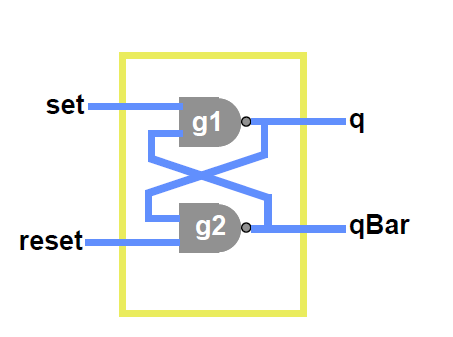

因此,電路需要具有記憶功能的存儲電路。FPGA中基本的存儲單元是D觸發(fā)器,也是實(shí)現(xiàn)時(shí)序邏輯的基本單元。

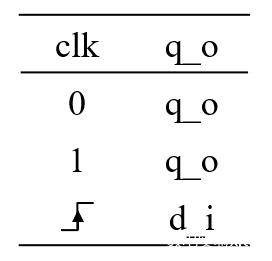

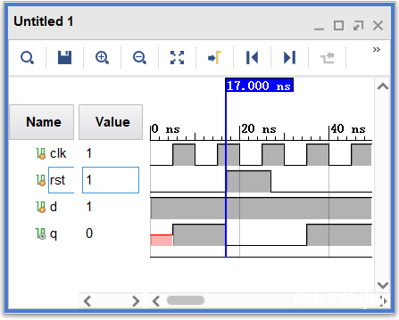

那么,什么樣的語句會被綜合成觸發(fā)器呢?在Verilog中,常使用always進(jìn)程塊描述時(shí)序邏輯。此時(shí),always進(jìn)程塊中的敏感列表一般為時(shí)鐘邊沿和異步控制信號,

** always ** @(posedge clk,posedge rst)

always進(jìn)程塊的執(zhí)行是在時(shí)鐘邊沿觸發(fā)下進(jìn)行的。

時(shí)序邏輯電路按狀態(tài)變化的特點(diǎn),可以分為同步時(shí)序邏輯電路和異步時(shí)序邏輯電路。

同步時(shí)序邏輯電路的各個(gè)觸發(fā)器狀態(tài)的轉(zhuǎn)換在同一時(shí)鐘脈沖作用下完成。目前,大多數(shù)數(shù)字電路都是同步時(shí)序電路。我們實(shí)驗(yàn)中所涉及到的也都是同步時(shí)序電路。

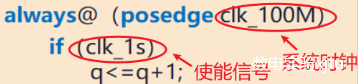

在設(shè)計(jì)時(shí)需要注意,所有always敏感列表中第一項(xiàng)敏感信號應(yīng)該為同一時(shí)鐘信號,比如,都為系統(tǒng)時(shí)鐘clk的上升沿。

不出現(xiàn)其他派生信號,比如,系統(tǒng)時(shí)鐘產(chǎn)生的分頻信號等等。

異步時(shí)序邏輯電路中,沒有統(tǒng)一時(shí)鐘,各觸發(fā)器狀態(tài)轉(zhuǎn)換是異步完成的。

在always進(jìn)程塊描述時(shí)序邏輯時(shí),賦值語句使用非阻塞賦值,即“<=”。

0****2

時(shí)序邏輯電路設(shè)計(jì)實(shí)例

下面來看幾個(gè)D觸發(fā)器的設(shè)計(jì)實(shí)例,來理解Verilog語句與電路之間的關(guān)系。

實(shí)例1:基本D觸發(fā)器

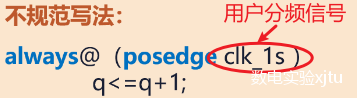

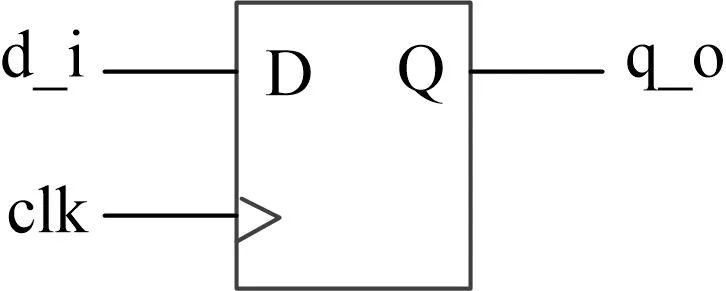

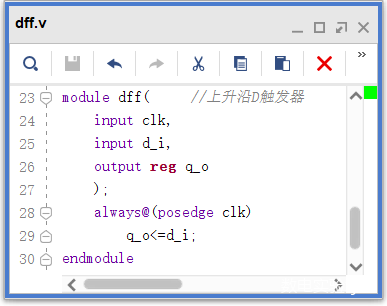

設(shè)計(jì)一個(gè)簡單的D觸發(fā)器,在時(shí)鐘上升沿觸發(fā)下,輸出等于輸入,其他時(shí)間輸出保持不變。

使用always語句進(jìn)行描述,敏感列表為時(shí)鐘上升沿。當(dāng)時(shí)鐘信號由0變?yōu)?時(shí),執(zhí)行always語句“q_o=d_i”,如下圖所示。

我們看到輸入信號d_i不出現(xiàn)在敏感信號列表中,也就表明,輸入的變化不會引發(fā)輸出立即變化,只有在時(shí)鐘上升沿時(shí)才被采樣。

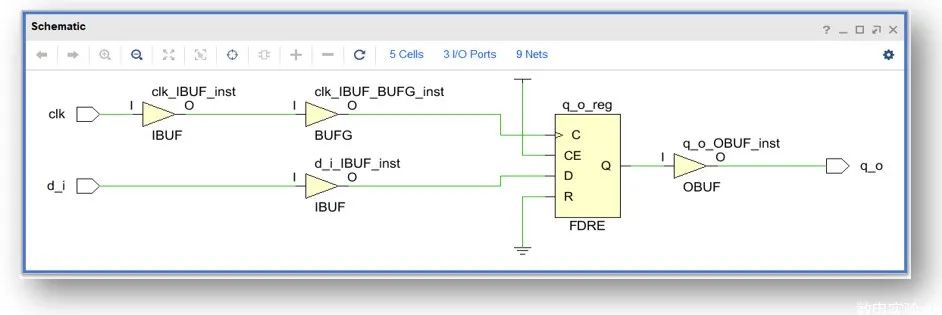

下面是綜合后的原理圖,綜合就是將Verilog設(shè)計(jì)對應(yīng)到FPGA內(nèi)部組成單元上。

我們看到,綜合出的是D觸發(fā)器(FDRE為D觸發(fā)器,參見賽靈思官方文檔ug799),其中敏感列表中的clk被綜合為觸發(fā)器的時(shí)鐘信號C,d_i連接D觸發(fā)器輸入端D。D觸發(fā)器還包含信號CE(時(shí)鐘使能端),以及R(復(fù)位端,高有效),在本示例中均未用到。因此,將CE連接高電平,使時(shí)鐘始終有效,R連接低電平,使復(fù)位無效。

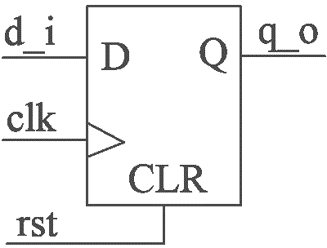

實(shí)例2:帶復(fù)位(高有效)的D觸發(fā)器

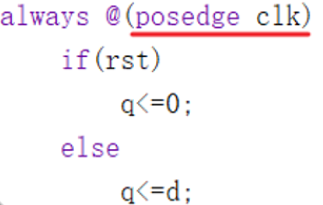

下面的例子加入了復(fù)位信號。復(fù)位分為同步復(fù)位和異步復(fù)位。

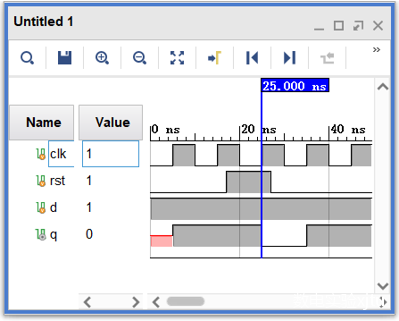

同步復(fù)位中,當(dāng)復(fù)位信號有效時(shí),必須要等到時(shí)鐘上升沿到來時(shí),才能執(zhí)行復(fù)位信號相關(guān)的行為語句,如仿真波形圖中所示。

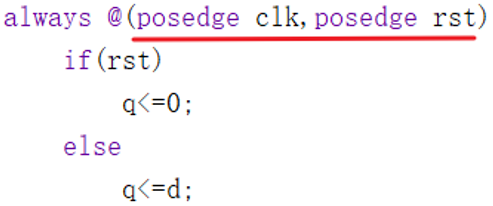

異步復(fù)位中的復(fù)位信號與時(shí)鐘沒有關(guān)系,只要復(fù)位信號有效,就立即執(zhí)行復(fù)位相關(guān)的邏輯行為。要實(shí)現(xiàn)異步復(fù)位,復(fù)位信號要放在敏感列表中。

仿真波形圖中可以看到,當(dāng)rst有效時(shí),輸出立即被復(fù)位,下一個(gè)clk上升沿到來時(shí),此時(shí),rst信號仍然有效,因此,輸出為0。再一個(gè)clk到來時(shí),復(fù)位無效,則輸出等于輸入。

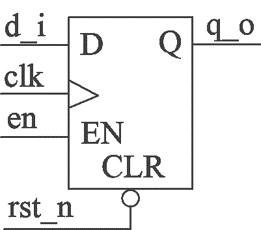

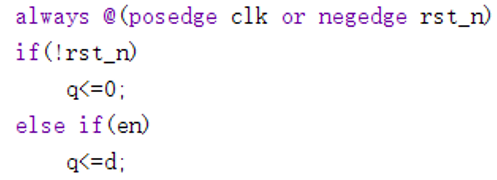

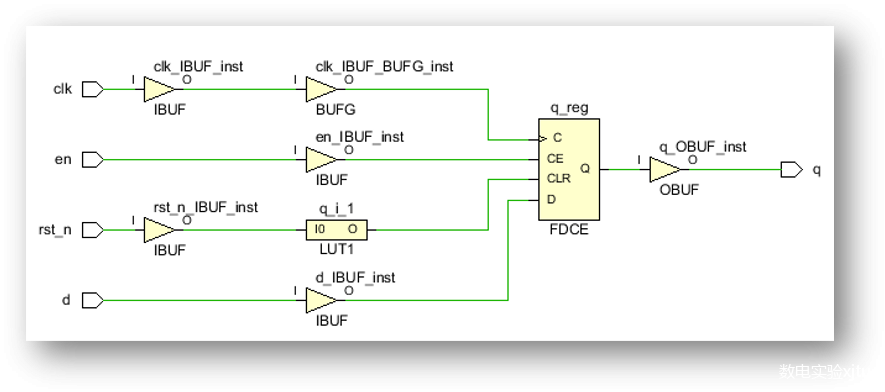

實(shí)例3:含異步復(fù)位(低有效)和同步使能的D觸發(fā)器

下面是一個(gè)帶有同步使能信號的D觸發(fā)器。

這里我們使用了低電平復(fù)位,當(dāng)復(fù)位信號無效,使能信號有效時(shí),在時(shí)鐘上升沿觸發(fā)下,輸出等于輸入。

在綜合后的原理圖中,en使能信號連接在了D觸發(fā)器的CE端。復(fù)位信號rst_n與CLK的連接經(jīng)過一個(gè)LUT(LUT是FPGA用于實(shí)現(xiàn)組合邏輯的基本單元查找表),在Vivado中可以看到該LUT的真值表,它實(shí)現(xiàn)的是反相器的功能,這也說明了賽靈思的FPGA中觸發(fā)器的復(fù)位引腳是高有效的,如果你設(shè)計(jì)中復(fù)位是低有效,這里就會多出一個(gè)反相器將其邏輯取反。

03

always進(jìn)程塊用法總結(jié)

always進(jìn)程塊是最常用的行為描述語句,他可以描述組合邏輯也可以描述時(shí)序邏輯。

描述組合邏輯時(shí),敏感列表中為輸入電平信號,而描述時(shí)序邏輯時(shí),敏感列表為時(shí)鐘邊沿及異步控制信號。Vivado綜合工具會根據(jù)always后面的敏感列表的不同形式綜合出相應(yīng)的電路。

always在仿真中還可以通過延時(shí)控制來產(chǎn)生激勵(lì)信號。例如,always #5 clk=~clk,表示當(dāng)執(zhí)行到該語句時(shí),需要延遲5個(gè)時(shí)間單位的時(shí)間(由`timescales 定義),然后再執(zhí)行“clk=~clk”。

-

FPGA設(shè)計(jì)

+關(guān)注

關(guān)注

9文章

428瀏覽量

26511 -

反相器

+關(guān)注

關(guān)注

6文章

311瀏覽量

43290 -

D觸發(fā)器

+關(guān)注

關(guān)注

3文章

164瀏覽量

47902 -

時(shí)序邏輯電路

+關(guān)注

關(guān)注

2文章

94瀏覽量

16538 -

CLK

+關(guān)注

關(guān)注

0文章

127瀏覽量

17158

發(fā)布評論請先 登錄

相關(guān)推薦

VHDL硬件描述語言與和數(shù)字邏輯電路設(shè)計(jì).侯伯亭&顧新

Verilog硬件描述語言描述.

VERILOG HDL硬件描述語言

VHDL硬件描述語言與數(shù)字邏輯電路設(shè)計(jì)

[VHDL硬件描述語言與和數(shù)字邏輯電路設(shè)計(jì)].侯伯亭&顧新.掃描版

經(jīng)典教材-VHDL硬件描述語言與數(shù)字邏輯電路設(shè)計(jì)(第三版)

VHDL硬件描述語言與數(shù)字邏輯電路設(shè)計(jì)

基于Verilog硬件描述語言的IEEE標(biāo)準(zhǔn)硬件描述語言資料合集免費(fèi)下載

Verilog硬件描述語言的學(xué)習(xí)課件免費(fèi)下載

如何使用Verilog硬件描述語言描述時(shí)序邏輯電路?

如何使用Verilog硬件描述語言描述時(shí)序邏輯電路?

評論