0****1

什么是有限狀態機

如果一個對象(系統或機器),由若干個狀態構成,在某種條件下觸發這些狀態,會發生狀態相互轉移的事件,那么此對象稱之為狀態機。描述對象的狀態往往是有限的,所以狀態機又稱為有限狀態機(Finite-state machine,FSM)。

有限狀態機是一種數學模型,是時序電路常用的設計工具,更是一種設計思想、設計方法。

有限狀態機的本質是在描述一系列具有先后順序和時序規律的事件。

有限狀態機核心是處理各種輸入事件和狀態切換,產生輸出控制信號。

0****2

有限狀態機的四要素

現態:當前的狀態;

條件:觸發狀態轉移的事件,即狀態輸入;

動作:執行某種操作,即狀態輸出;

次態:滿足條件后跳轉到下一狀態。

03

有限狀態機描述方法

第一步, 邏輯抽象,得出狀態圖或狀態表。主要包括:

· 分析給定的邏輯問題,確定系統的狀態、輸入變量和輸出變量。

· 分析確定每一個狀態的輸入、狀態轉移條件和輸出。

第二步,根據狀態轉移圖或表進行狀態化簡。

第三步,狀態編碼。

第四步,根據狀態轉移圖或表進行代碼描述。

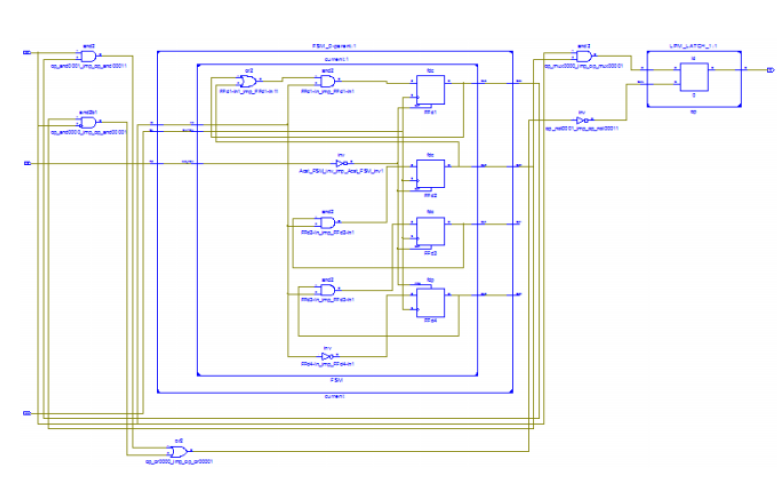

使用Verilog HDL描述狀態機,有一定的固定格式,以三段式狀態機為例:

第一段,使用時序邏輯,描述現態,使用非阻塞賦值。

第二段,使用組合邏輯,描述次態,使用阻塞賦值。

第三段,使用可以使用組合邏輯,也可以使用時序邏輯進行描述,主要描述的是輸出控制信號。

-

編碼器

+關注

關注

45文章

3639瀏覽量

134429 -

有限狀態機

+關注

關注

0文章

52瀏覽量

10323 -

狀態機

+關注

關注

2文章

492瀏覽量

27529 -

HDL語言

+關注

關注

0文章

47瀏覽量

8913

發布評論請先 登錄

相關推薦

什么是有限狀態機呢

有限狀態機的建模與優化設計

VHDL有限狀態機設計-ST

初學者對有限狀態機(FSM)的設計的認識

如何使用FPGA實現序列檢測有限狀態機

有限狀態機設計是HDL Designer Series的關鍵應用

基于事件驅動的有限狀態機介紹

基于事件驅動的有限狀態機介紹

一個基于事件驅動的有限狀態機

什么是有限狀態機?有限狀態機的四要素介紹

什么是有限狀態機?有限狀態機的四要素介紹

評論