本文將重點介紹如何在無需久等 SI 和 PI 專家反饋的情況下,助力 PCB 設(shè)計團隊在預(yù)算范圍內(nèi)按時交付合格的產(chǎn)品。

對于當(dāng)今設(shè)計高速、高密電路板的工程師來說,信號完整性 (SI) 和電源完整性 (PI) 是重中之重。而在設(shè)計早期階段發(fā)現(xiàn) SI/PI 問題,有助于加快設(shè)計簽核,以免重新設(shè)計。

在簽核高速 PCB 設(shè)計時,工程師需要解決三個關(guān)鍵問題:電源分析、SerDes 鏈路合規(guī)和 DDR 存儲器接口合規(guī)。電源傳輸網(wǎng)絡(luò)(Power Delivery Network, PDN) 必須充足、高效和穩(wěn)定,信號質(zhì)量必須符合存儲器接口和串行鏈路合規(guī)規(guī)范。

1

設(shè)計分析框架

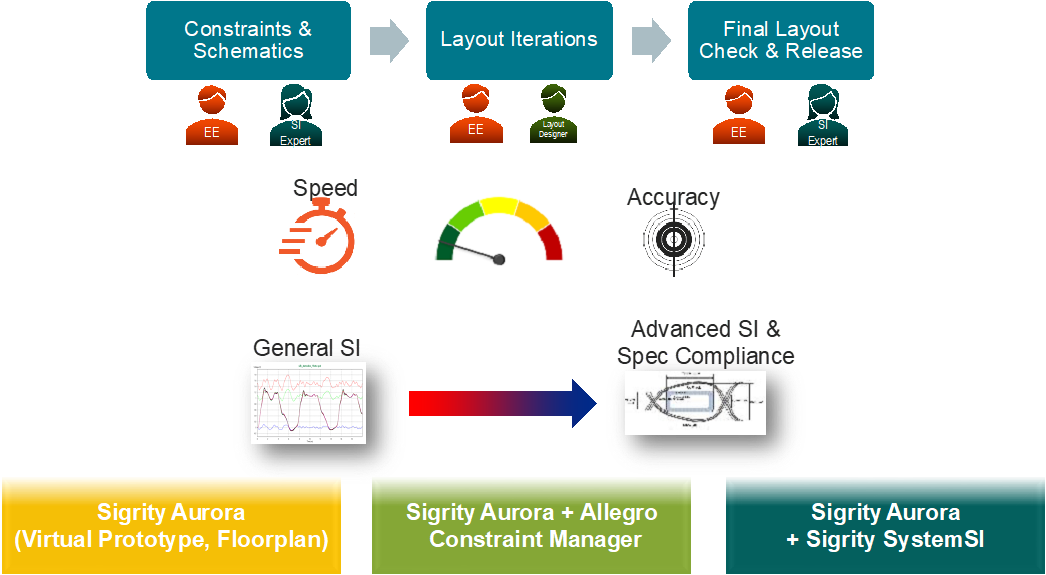

設(shè)計 PCB 時需要考慮幾個重要框架(圖 1)。

圖 1:設(shè)計分析框架

設(shè)計的第一步是原理圖;第二步是 layout,并在 layout 的后期階段進行詳細(xì)分析以確保 layout 功能符合預(yù)期。在設(shè)計周期中,任務(wù)、優(yōu)先事項和工作重點都會變化,但有一條經(jīng)驗法則經(jīng)久不衰:發(fā)現(xiàn)和糾正問題越早越好。

一般來說,設(shè)計流程的后期階段才會進行詳細(xì)的仿真、分析和優(yōu)化,通常是驗證和簽核的最后一步。一旦此時發(fā)現(xiàn)需求和性能方面的缺陷,就需要花費額外的時間和人力來解決,不可避免地導(dǎo)致項目超出預(yù)算并延遲產(chǎn)品上市;然而這些問題原本在設(shè)計早期階段就可以發(fā)現(xiàn)并解決——要在當(dāng)今競爭激烈的電子市場中保持領(lǐng)先,則不能再將分析和驗證放在設(shè)計流程的最后階段;而是從設(shè)計流程的初始階段開始,就采用設(shè)計同步分析 (In-design Analysis, IDA) 方法集成仿真和分析,將分析和驗證視為在芯片、封裝、電路板和完整系統(tǒng)級設(shè)計層面的各個階段中都不可分割的一部分。

圖 2:Allegro PCB Designer layout 環(huán)境中的設(shè)計同步分析工作流程與Cadence Sigrity Aurora PCB 分析軟件集成

設(shè)計團隊是設(shè)計過程中的一個重要因素。在設(shè)計初期, SI 工程師會來幫助理解設(shè)計約束等問題;在 layout 設(shè)計階段,layout 設(shè)計專家將進行設(shè)計;而到了最終 layout 驗證階段,SI 工程師又將再次參與;但是在整個設(shè)計過程中,SI 工程師不一定能隨時提供幫助。因此,要想按時交付設(shè)計并保質(zhì)保量,PCB 設(shè)計人員需要具備獨立執(zhí)行普通 SI/PI 仿真的能力。在 PCB 設(shè)計環(huán)境中直接嵌入仿真工作流程,賦能設(shè)計人員,有助于確保設(shè)計符合預(yù)期并按時交付。

串?dāng)_和阻抗匹配等普遍的 SI/PI 問題往往需要在設(shè)計初期被快速解決。在設(shè)計后期,仿真的細(xì)節(jié)精確度非常重要,但在開始階段,設(shè)計人員通常只需要確保方向正確。仿真精度與速度往往無法兼得,需要取舍。如果在一開始就需要細(xì)節(jié)精確度,設(shè)計人員可以縮小工作范圍,只考慮設(shè)計的一個部分;而如果整個設(shè)計必須盡早進行精確仿真,那么分析工作流程可以利用復(fù)雜的分布式計算資源,確保速度精度雙管齊下。

2

電源設(shè)計分析工作流程

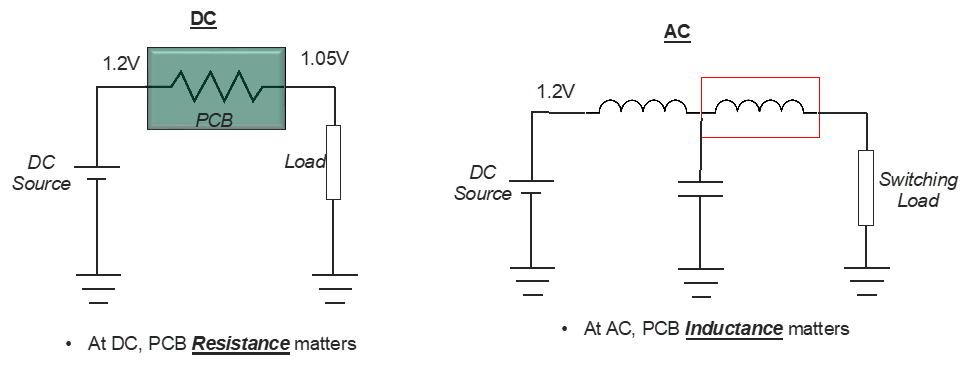

PCB 設(shè)計人員面臨的一個主要挑戰(zhàn)是為負(fù)載供電。電源正確的直流(幅度)和交流(紋波)對于發(fā)射 (Tx) 和接收 (Rx) 信號至關(guān)重要(圖 3)。

圖 3:發(fā)射和接收信號的元件需要充足且穩(wěn)定的直流和交流電源

對于直流電路,電阻很重要;對交流電路來說,重要的則是電感。直流電路包括直流電源、PCB 和 IC 負(fù)載,電流需要流向這些負(fù)載。直流電源流過 PCB 上的銅,因其電阻并非是無窮小, PCB 上會存在壓降,導(dǎo)致負(fù)載側(cè)電壓的幅度很可能會比原始電源的幅度低,因此需要分析負(fù)載端的電壓是否足夠。每種IC對供電電壓都有要求,設(shè)計人員必須確保 IC 芯片獲得了所需的電壓。

直流分析的重點是 PCB 電阻。對于交流分析,邏輯和輸入/輸出 (I/O) 電路每秒要開關(guān)數(shù)百萬個晶體管,每次晶體管開關(guān)時,都需要立即獲得電流,這不太可能來自直流電源,因為 PCB 更像是一個電感器。在較高的開關(guān)頻率下,電感阻抗遠(yuǎn)遠(yuǎn)大于電阻阻抗。因此,PCB 的電感十分關(guān)鍵。電感在很大程度上取決于 PCB 的幾何形狀,需要格外關(guān)注 PCB layout。電壓調(diào)節(jié)器模塊 (Voltage Regulator Module, VRM) 的電感幾乎一定會過高,因此需要使用局部去耦電容來提供開關(guān)負(fù)載所需的瞬時電流。電容器與其負(fù)載之間的電感量很重要:電感越大,電容器的效能就越低,因此必須找到與負(fù)載連接的電感較高的電容器,并想辦法降低電感。

電源工作流程:布線前

在設(shè)計流程的開始階段,設(shè)計人員需要面對幾十上百頁的原理圖、幾十個電壓軌,以及正確設(shè)置電源連接的要求。面對龐大而復(fù)雜的電源結(jié)構(gòu),如果能夠以可視化的方式查看電源、負(fù)載、無源壓降等位置,設(shè)計人員在避免短路或電源連接錯誤等問題上會更加得心應(yīng)手。Cadence Sigrity PowerTree 能夠可視化原理圖中的電源連接,幫助設(shè)計人員在設(shè)計早期快速仿真,并發(fā)現(xiàn)意外的電阻降低或連接不當(dāng),以便在電路圖中進行修正,避免布線后釀成大錯。

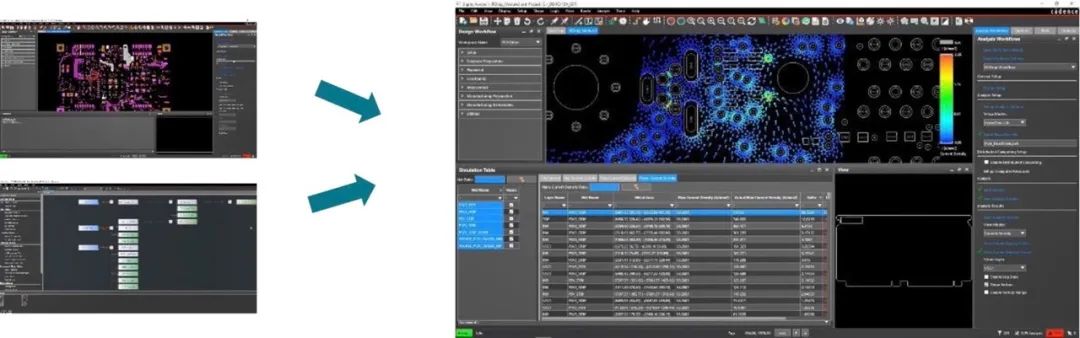

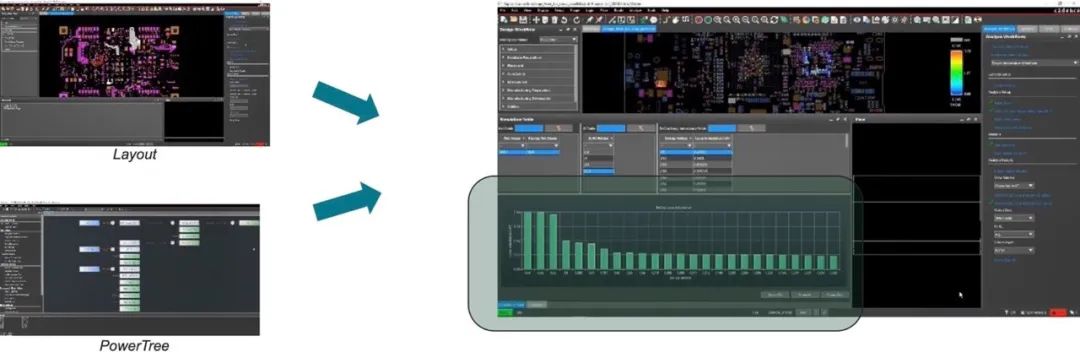

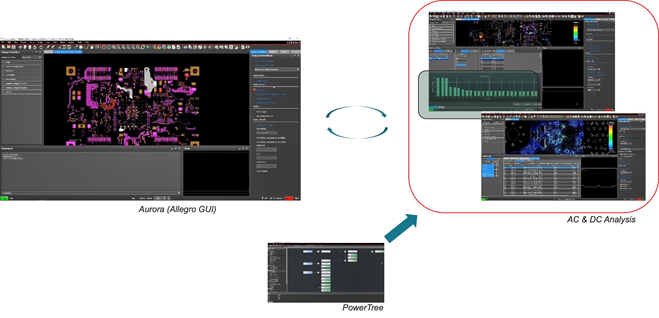

電源工作流程:layout 分析

在 layout 分析工作流程中,工程師可以使用之前創(chuàng)建的 PowerTree 文件與 layout 設(shè)計師合作創(chuàng)建電路板文件,分析直流電路并發(fā)現(xiàn)電流瓶頸。在進行直流分析時,需要重點了解流向 IC 負(fù)載的 VRM 源電流的大小、IC 獲得的電流大小以及哪些 VRM 連接到哪些IC。PowerTree 文件已經(jīng)捕獲了所有這些信息,可以在 layout 環(huán)境中提供運行直流壓降分析的一切所需,實現(xiàn)壓降、電流、電流密度、過孔電流等參數(shù)的可視化(圖 4)。

圖 4:PCB layout 與 PowerTree 相結(jié)合,進行壓降分析

還可以利用 CadenceCelsius Thermal Solver 中的電熱協(xié)同仿真功能進行熱影響分析,以了解電流密度的大小、產(chǎn)生的熱量,以及是否可以有效散熱。

交流分析以類似的方式進行。設(shè)計人員擁有電路板和 PowerTree 文件,可以快速運行交流分析,查看數(shù)百/數(shù)千個去耦電容的放置是否妥當(dāng),以及電容器與過孔的距離是否可以接受(圖 5)。所選過孔上每個電容器的電感都會顯示出來,設(shè)計人員可以快速查看環(huán)路電感中的異常值,發(fā)現(xiàn)去耦電容的不佳位置。如果有一個小型去耦電容的電感值過高,就意味著 layout 出了問題,設(shè)計人員需要先更改 layout,之后再繼續(xù)設(shè)計。

圖 5:PCB layout 與 PowerTree 相結(jié)合,進行去耦電容位置分析

IDA 可以利用 PowerTree 在布線前階段已經(jīng)獲得的信息,幫助設(shè)計人員快速了解 layout 的質(zhì)量,并在設(shè)計流程的早期解決問題。

3

SerDes 合規(guī)設(shè)計流程

SerDes 收發(fā)器的工作頻率極高,會導(dǎo)致許多問題,所以在設(shè)計方面的容錯率很低。未進行均衡的 SerDes 設(shè)計在接收器處可能無法獲得良好的眼圖,因此要使用 IBIS-AMI 模型模擬 Tx 和 Rx 處的均衡,以顯示展開的眼圖。在高速信號下,層之間的過渡非常敏感,必須選擇合適的介電材料,甚至是過孔的位置也變得十分重要,以便盡量減少對通道的影響。

高速 SerDes 通道的 PCB 設(shè)計人員通常會在設(shè)計初期與 SI 專家一起研究過孔結(jié)構(gòu)。過孔結(jié)構(gòu)的優(yōu)化可決定串行鏈路合規(guī)測試能否通過。

SerDes 設(shè)計挑戰(zhàn)和解決方案

電氣工程的基本規(guī)則是,速度越高,需要考慮的細(xì)節(jié)就越多。對于以前在低速設(shè)計中可以忽略的小結(jié)構(gòu),如果設(shè)計不當(dāng),可能會在高速設(shè)計中產(chǎn)生災(zāi)難性的影響。過孔會造成阻抗不連續(xù),降低信號質(zhì)量。因此需要仔細(xì)設(shè)計過孔結(jié)構(gòu),以便預(yù)測它的行為。

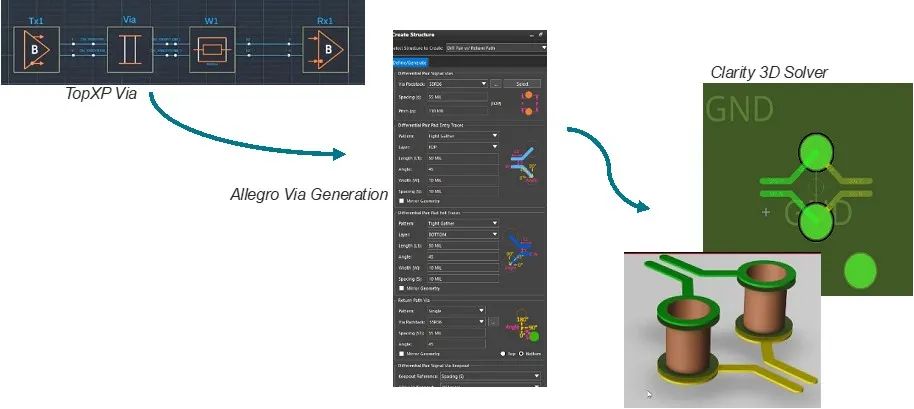

傳統(tǒng)的做法是在原理圖階段預(yù)先設(shè)計結(jié)構(gòu)中的每個過孔,滿足速度要求。而利用設(shè)計工具中內(nèi)置的技術(shù),可以更高效地完成這一耗時的手工流程,輕松設(shè)計、仿真和優(yōu)化用于高速信號傳輸?shù)倪^孔。

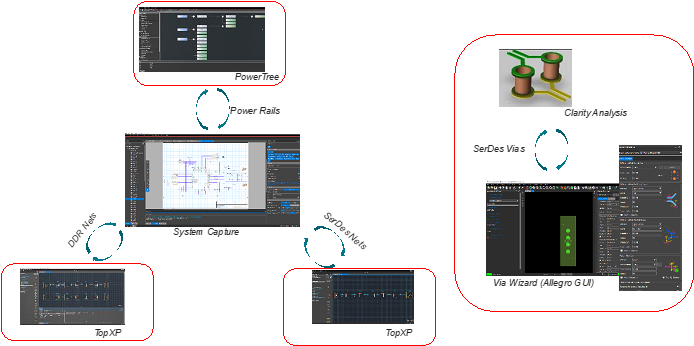

Cadence Sigrity Aurora 工作流程包括過孔向?qū)?/strong>,可快速生成基于 Allegro 的過孔結(jié)構(gòu)。利用這一自動化流程,工程師可以在簡單易用的 Allegro 環(huán)境中自行創(chuàng)建過孔結(jié)構(gòu),然后使用 Cadence Clarity 3D Solver 進行分析(圖 6)。

圖 6:利用 Sigrity Aurora 過孔向?qū)Чぷ髁鞒蹋焖偕苫?Allegro 的過孔結(jié)構(gòu),并使用 Clarity 3D Solver 對過孔進行分析和優(yōu)化

按照慣例,這屬于 SI 專家的工作范疇,但有了 IDA 工具,PCB 設(shè)計人員不必依賴 SI 專家的幫助,可以自主完成。整個流程簡單易用,包括設(shè)置結(jié)構(gòu),然后在過孔向?qū)Лh(huán)境中打開 Clarity 3D Solver,運行仿真,評估結(jié)構(gòu)的有效性,并在流程早期階段進行調(diào)整。

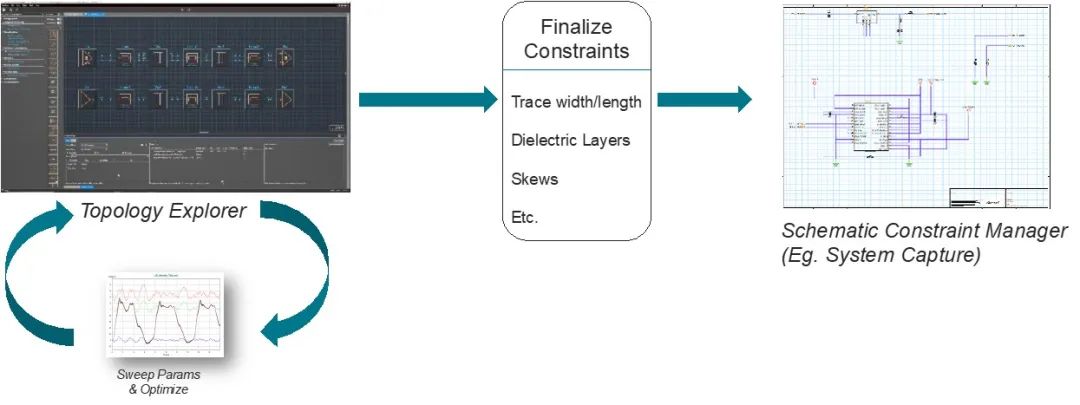

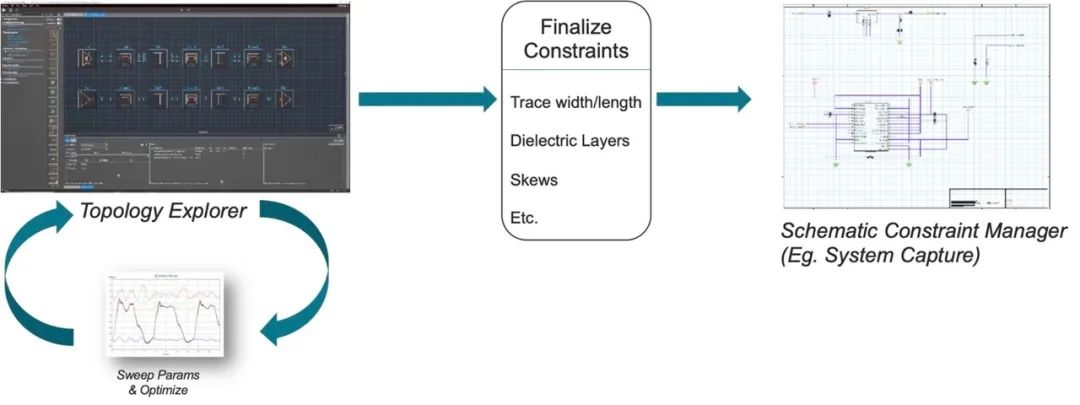

SerDes 面臨的另一個挑戰(zhàn)是通道設(shè)計中的損耗。在高速運行時,介質(zhì)材料的損耗可能非常大,因此對通道性能而言,選擇合適的材料、長度等至關(guān)重要。許多問題,如堆疊、走線寬度和距接地平面的高度,都需要預(yù)先確定。使用 Sigrity Topology Explorer(TopXp)工具對設(shè)計中提取的信號進行仿真,設(shè)置并掃描參數(shù)掃描,將最小/最大長度/間距值輸入 Allegro 原理圖規(guī)則管理器(Allegro System Capture)。初步規(guī)則和原理圖流程如圖 7 所示。隨著設(shè)計的推進,根據(jù)最終確定的堆疊和材料,可以對這些規(guī)則進行調(diào)整。

圖 7:使用 Sigrity Topology Explorer (TopXp) 中的 sweep manager 工具處理 SerDes 規(guī)則和原理圖工作流程

原理圖階段結(jié)束后,開始進入 layout 階段,下一個挑戰(zhàn)是規(guī)范合規(guī)。規(guī)范取決于技術(shù):PCIe、USB 等,每種技術(shù)都有自己的要求,所以這是一個復(fù)雜的過程。在分析過程中,一定要使用正確的發(fā)射器和接收器 IBIS-AMI 模型。對于通道,可以使用 Cadence 工具來準(zhǔn)確地建立通道模型和地址規(guī)范。

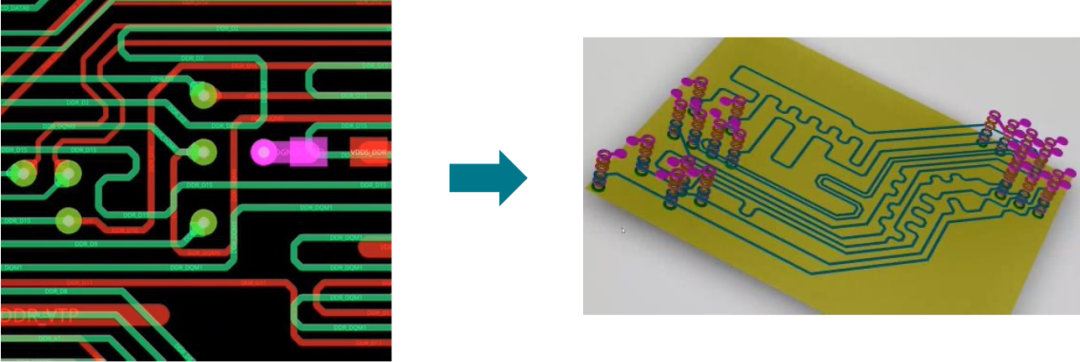

具體而言,可以使用 layout 設(shè)計師創(chuàng)建的電路板文件,選擇幾個或所有通道(取決于時間是否充足),然后對整個通道運行 2.5 或全 3D 分析(圖 8)。

圖 8:通道準(zhǔn)確建模,實現(xiàn)規(guī)范合規(guī)的工作流程

利用通道提取的結(jié)果,可以根據(jù)所需的協(xié)議運行合規(guī)分析。這類分析可能需要重復(fù)幾次,因為往往會出現(xiàn)一些在初步階段沒有確定的模糊要求,需要額外的迭代。

4

DDR 合規(guī)分析流程

DDR 的速度不如 SerDes 快,在某些方面也沒有 SerDes 那么復(fù)雜,但會帶來更多的信號完整性挑戰(zhàn)。某些 DDR 的速度可能與 SerDes 的最低速度重疊,而且有大量的單端和差分網(wǎng)絡(luò),它們都需要滿足復(fù)雜的信號完整性要求。

DDR 設(shè)計挑戰(zhàn)

早期階段的 DDR 信號完整性問題通常涉及阻抗匹配和信號不連續(xù)、雙列直插式內(nèi)存模塊 (Dual In-line Memory Modules ,DIMM) 等樁線、端接優(yōu)化和走線串?dāng)_等普遍的問題。盡管是基本要求,但重要的是要確保考慮到這些以及更復(fù)雜的問題,而且越早越好。為此,與 SerDes 一樣,可以通過Sigrity Topology Explorer進行掃描,從而快速檢查這些問題。通過仿真掃描可以確定約束條件,并將其與原理圖一起保存(圖 9)。

圖 9:在原理圖規(guī)則管理器中優(yōu)化 TopXp 拓?fù)鋻呙?/i>

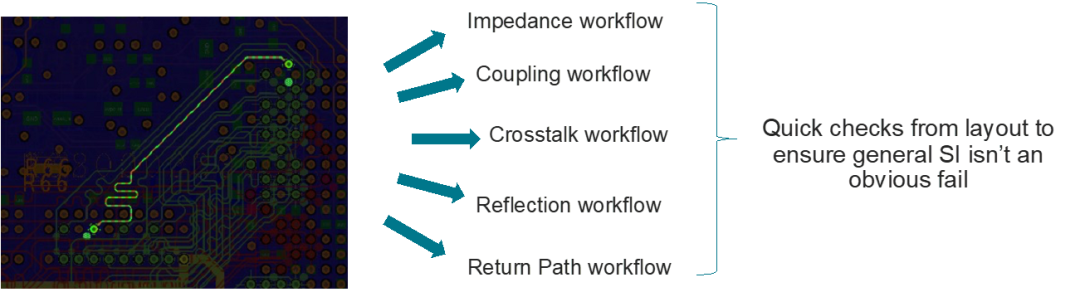

生成帶規(guī)則的初步原理圖后,即進入 layout 階段。在這一階段,IDA 可為 PCB 設(shè)計人員提供早期布局驗證,增強對layout 正確性的信心。為此,可以在 Allegro layout 環(huán)境中使用 Sigrity Aurora 工作流程快速運行一系列慣例的 SI 分析(阻抗、耦合、串?dāng)_、反射、返回路徑等),在走線上直觀地顯示問題所在,減少 SI 專家和 layout 設(shè)計人員的反復(fù)溝通,及時準(zhǔn)確地快速解決問題,縮短設(shè)計時間。

如果 layout 設(shè)計人員無法解決上述問題,則可以再次使用 Sigrity Typology Explorer來運行迭代。如此一來,設(shè)計人員還可以在 layout 階段對初步規(guī)則進行精細(xì)調(diào)整,更新數(shù)值,使之可用于其他信號。

除了通常在原理圖和 layout 階段解決的一般信號完整性問題外,DDR 的性質(zhì)帶來了三個其他挑戰(zhàn):同步開關(guān)噪聲 (Simultaneous Switching Noise, SSN)、過孔串?dāng)_和 JEDEC 標(biāo)準(zhǔn)合規(guī)。

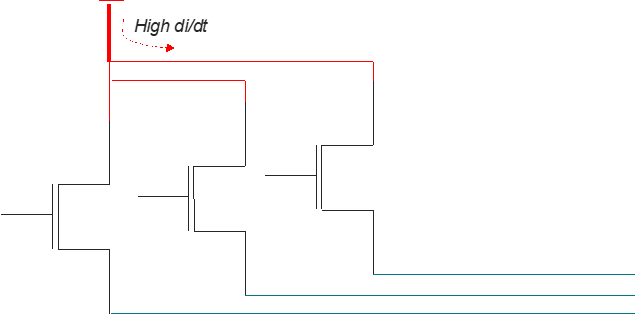

SSN 挑戰(zhàn)

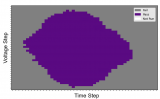

在 SSN 中,晶體管驅(qū)動單個比特的輸出,從電壓軌獲取所需功率并將其輸入到網(wǎng)絡(luò)中。通常,可從 IBIS 文件或分析中捕獲晶體管的行為。使用 DDR 時,多個網(wǎng)絡(luò)可以同時切換,并且狀態(tài)之間的轉(zhuǎn)換會有高電流變化率 (di/dt) 要求,這會影響電壓電平,反過來又影響轉(zhuǎn)換(圖 10)。有兩種模型對 SSN 的精確建模至關(guān)重要:兼顧電源影響的 IBIS 模型和 PDN 精確模型。

圖 10:多個網(wǎng)絡(luò)可同時切換,這對 di/dt 有很高的要求,因此電壓電平和轉(zhuǎn)換相互影響

返回路徑過孔的挑戰(zhàn)

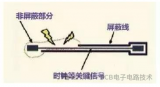

在圖 11 左側(cè),綠色的線代表數(shù)據(jù)線 (DQ) 信號過孔,粉紅色區(qū)域是接地 (GND) 過孔,它將兩個接地平面拼接在一起。在圖片右側(cè),其中一個信號在綠色頂層上有一條走線,而第二條線將作為具有理想返回路徑的參考線。

圖 11:信號過孔的返回路徑

然而,返回電流必須流到倒數(shù)第二層,為此要找到最近的路徑。信號直接流向信號過孔,而返回路徑則位于信號的正下方,然后信號必須找到通向縫合過孔的路徑,然后再返回,這樣就又回到底層。所有信號過孔都會經(jīng)歷同樣的情況——它們都使用相同的縫合過孔作為返回路徑,從而導(dǎo)致過孔-過孔串?dāng)_。這是一種 3D 現(xiàn)象,而不是簡單的 2D 并行的問題。需要進行 2.5 或 3D 分析來準(zhǔn)確建模,借助 Sigrity Aurora 分析工作流程,即便不是 SI 專家也能完成這一任務(wù)。

JEDEC 規(guī)范的復(fù)雜性

JEDEC 的要求非常復(fù)雜,并且含有許多符號或縮略語(Vix, tDQSS, tDSS, tDS, tDSH tDH, tVAC 等....)。此外,不同技術(shù)(如 DDR、低功耗 DDR (Low Power DDR, LPDDR)、圖形 DDR (Graphics DDR, GDDR))、不同版本(DDR3 與 DDR4)以及不同總線(如地址與數(shù)據(jù)、時鐘信號 (Clock Signal, CLK) 與 DQ 選通 (DQ Strbe, DQS))的要求也各不相同。

例如,DDR4 數(shù)據(jù)要求矩形眼圖模板,需要測量誤碼率 (Bit Error Rate, BER), DDR5 則要求的是菱形。在 Cadence PCB layout 環(huán)境中的分析工作流程中,可以使用 Sigrity PowerSI 和 Clarity 3D Solver 提取引擎,進行詳細(xì)、精確的互連建模,輕松應(yīng)對 SSN、返回路徑過孔和 JEDEC 規(guī)范合規(guī)挑戰(zhàn)。

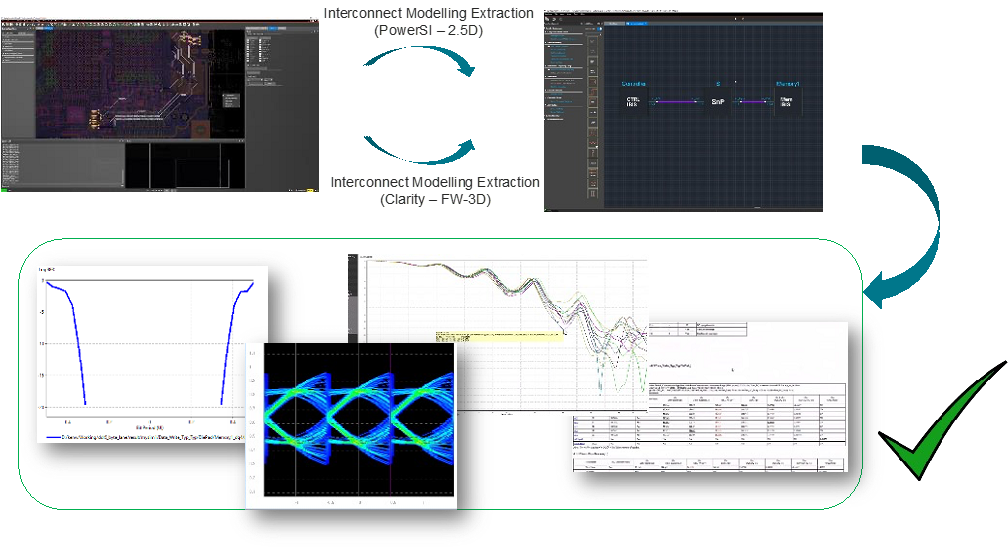

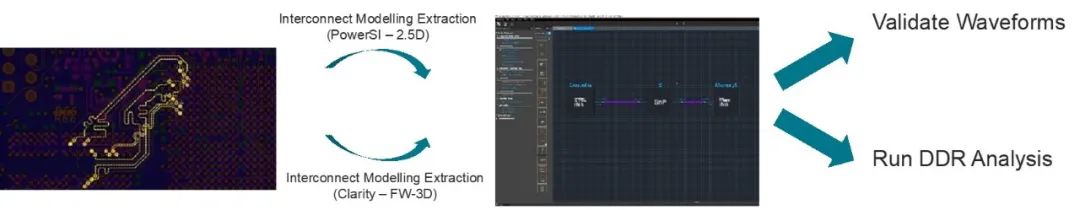

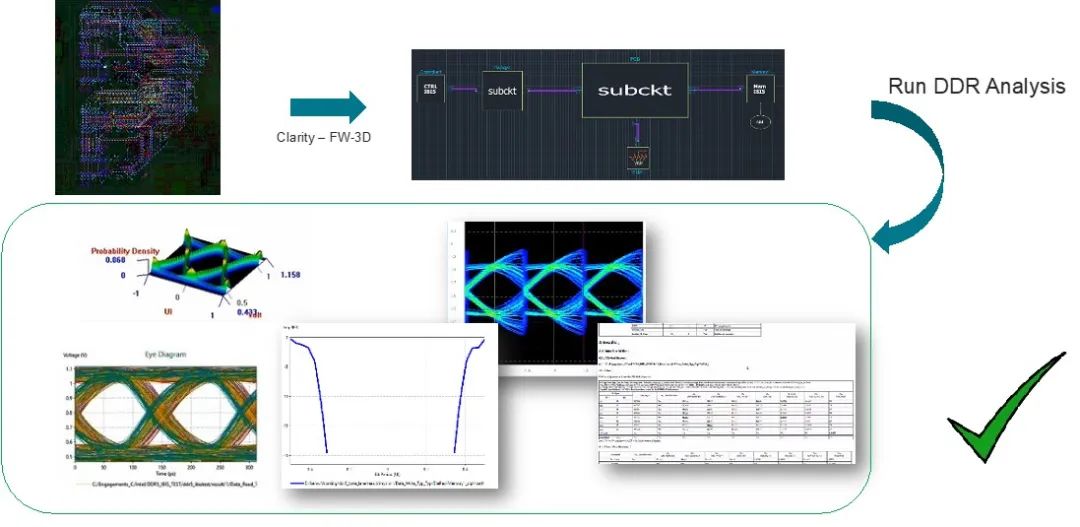

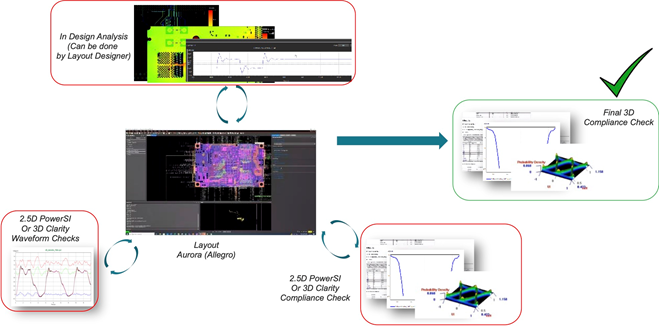

互連模型提取

在 DDR 工作流程的后期,網(wǎng)絡(luò)已經(jīng)鋪設(shè)完成,初步的 DDR 檢查也已經(jīng)完成。現(xiàn)在,需要提取 2.5 或 3D 互連模型進行 layout 驗證。按時間安排,可以針對一個部分、一個通道或幾個信號進行提取。根據(jù)已提取的信息,可執(zhí)行快速波形驗證,確保波形正確(圖 12),還可以使用 Sigrity PowerSI 2.5D 或 Clarity 3D Solver 運行快速 DDR 分析,確保設(shè)計滿足所有要求。

圖 12:提取互連模型用于驗證波形和運行 DDR 分析

通過這種流程,設(shè)計人員還可以有條不紊地檢查過孔串?dāng)_效應(yīng)、兼顧電源影響的效應(yīng)和其他高級效應(yīng),確保通道符合 DDR 規(guī)范。同樣,這一流程使 PCB 設(shè)計人員能夠獨立完成大部分驗證工作,減少對 SI 專家的依賴。

然后,在最終檢查中,使用 Clarity 3D Solver 對整個電路模塊進行全波 3D 仿真分析,確保捕捉到每個細(xì)節(jié),并運行 DDR 合規(guī)分析檢查(圖 13)。

圖 13:在最終設(shè)計檢查中,使用 Clarity 3D Solver 對整個模塊進行 DDR 分析

對于合規(guī)分析,仿真工作流程會針對所選的特定協(xié)議提供所有結(jié)果。如果設(shè)計通過這一流程,就表示電路板的功能一切正常。

5

電路板設(shè)計示例

本例是一個真實的 PCB 設(shè)計,展示了如何使用 Cadence Allegro/Sigrity/Clarity來簡化設(shè)計過程。圖 14 展示了設(shè)計的規(guī)則階段。

圖 14:PCB 設(shè)計實例的規(guī)則階段

該設(shè)計處于原理圖階段,PowerTree 文件用于顯示電源軌并驗證其設(shè)置是否正確。在這一階段,還將運行一些迭代 DDR 仿真,以確保首次通過的規(guī)則正確無誤。也可以采用同樣的流程運行 SerDes 仿真,確保選擇合適的電介質(zhì)、堆疊準(zhǔn)確無誤等。與此同時,設(shè)計人員可以使用 Clarity 3D Solver為 SerDes 設(shè)計設(shè)置正確的通孔結(jié)構(gòu)并運行分析,然后將其用于 layout 中。

下一階段是電源分析,如圖 15 所示。

圖 15:PCB 設(shè)計實例的電源分析階段

現(xiàn)在可以使用初期的 layout 和先前設(shè)置的 PowerTree 文件來執(zhí)行初步的交流和直流分析,確保有足夠的電源平面用于直流壓降,并且電感足夠低,以便電容器在高頻下有效工作。由于 layout 和 PowerTree 文件在前一階段已經(jīng)完成設(shè)置,這一階段進行起來要快得多,也容易得多。

圖 16:PCB 實例的高速設(shè)計階段

在這一階段,PCB 設(shè)計人員與 layout 專家一起運行慣例 SI 分析,找出信號不連續(xù)的問題。使用 Cadence 流程,layout 設(shè)計人員可以直觀地發(fā)現(xiàn)并糾正問題,而無需讓 PCB 設(shè)計人員參與迭代。設(shè)計交回到 PCB 設(shè)計人員手中時,細(xì)節(jié)問題已經(jīng)糾正,設(shè)計版面更加整潔,花費的時間也更少。PCB 設(shè)計可以直接進入 2.5D 或 3D 通道提取階段,以執(zhí)行波形檢查,甚至還可以執(zhí)行一些合規(guī)檢查。此時已接近設(shè)計的尾聲,因此可能只需要檢查某些層的合規(guī)性。

最后一步是使用 Clarity 3D Solver 對 SerDes 和 DDR 進行完整的全波 3D 合規(guī)檢查,以驗證整個設(shè)計。

本文結(jié)論

利用設(shè)計同步分析 (IDA) 在設(shè)計流程早期發(fā)現(xiàn) SI/PI 問題,有助于快速完成復(fù)雜的高速和/或高密度電路板的驗證和最終簽核。雖然 PCB 設(shè)計人員可能需要稍長的時間,來完成設(shè)計迭代并糾正基本的 SI/PI 問題,但這樣可以減少重新設(shè)計,為項目節(jié)省大量的時間和成本。

本文重點闡述了要成功將產(chǎn)品推向市場,PCB 設(shè)計團隊需要解決的三大關(guān)鍵問題:電源分析、SerDes 鏈路合規(guī)和 DDR 存儲器接口合規(guī)。采用上述方法,PCB 設(shè)計人員能夠依靠自己的力量,在預(yù)算范圍內(nèi)按時交付合格的產(chǎn)品,而無需等待 SI 和 PI 專家抽出時間提供幫助,也不必使用復(fù)雜難懂的分析工具。

-

電源

+關(guān)注

關(guān)注

184文章

17706瀏覽量

249982 -

pcb

+關(guān)注

關(guān)注

4319文章

23083瀏覽量

397551 -

電路板

+關(guān)注

關(guān)注

140文章

4954瀏覽量

97704 -

PCB設(shè)計

+關(guān)注

關(guān)注

394文章

4683瀏覽量

85559

發(fā)布評論請先 登錄

相關(guān)推薦

華為發(fā)布兩大關(guān)鍵創(chuàng)新技術(shù)方向

高速PCB設(shè)計指南

改善升壓轉(zhuǎn)換器PCB布局的五個步驟

中國信通院發(fā)布“2024云計算十大關(guān)鍵詞”

高速pcb與普通pcb的區(qū)別是什么

高速pcb布線規(guī)則有哪些

高速pcb的定義是什么

Ansys多物理場簽核解決方案獲得英特爾代工認(rèn)證

Ansys和英特爾代工合作開發(fā)多物理場簽核解決方案

MES系統(tǒng)實施的幾大關(guān)鍵步驟

如何利用 PCB 設(shè)計改善散熱?

示波器的三大關(guān)鍵指標(biāo)有哪些?

新思科技攜手臺積公司推出“從架構(gòu)探索到簽核” 統(tǒng)一設(shè)計平臺

高速PCB信號走線的九大規(guī)則分別是什么?

改善高速 PCB 簽核的三大關(guān)鍵

改善高速 PCB 簽核的三大關(guān)鍵

評論