Cadence員工Mohamed Naeim 博士曾在CadenceLIVE 歐洲用戶大會上做過一場題為《2D/3D 熱分析和三裸片堆疊設計實現》的演講,本文將詳細講述該演講內容。

實驗:兩個裸片是否優于一個裸片?

由于線長縮短,3D-IC 會減少功耗,帶來性能提升。在此,3D-IC 指的是將一個裸片(或兩個)擺放在另一個裸片之上,而不是指基于中介層的設計。在這種情況下,由于兩個裸片之間的熱量不易散出,將兩個裸片堆疊在一起會導致溫度升高。3D 熱分析建立在對每個裸片進行熱分析的基礎之上,因此必須要先進行有效的 2D 熱分析。

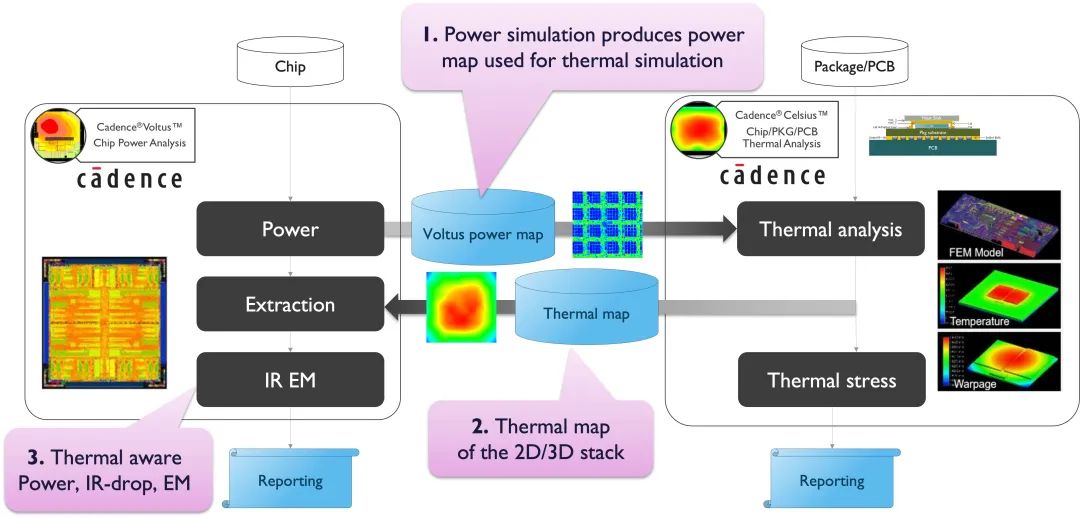

上圖是實驗設置。使用 Cadence Voltus IC Power Integrity Solution 生成用于熱仿真的功耗圖,然后再用 Celsius Thermal Solver 生成熱功耗圖。這樣就能對功耗、壓降和電子遷移進行兼顧熱影響的分析。

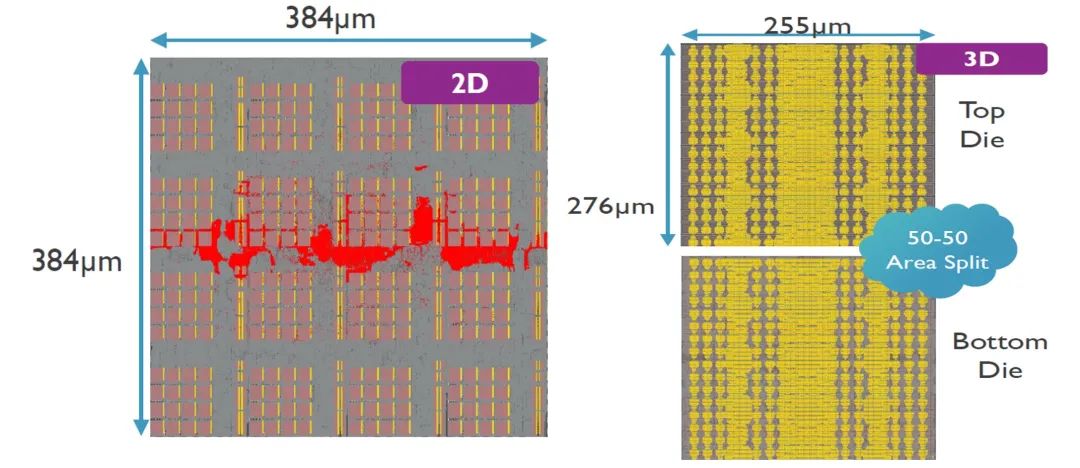

使用的實驗設計是一個多核心集群,有 256 個 32 位 RISC-V 內核,無 L2 高速緩存,和一個 MemPool 組。該集群有 200 萬標準單元和 384 個內存宏。由于線長較短,簡單地將設計隨意一分為二,的確可以實現 3D-IC 設計的性能提高,但正如預期的那樣,與 2D 基線(將整個芯片設計成一個裸片)相比,溫度有所升高。

可以采用三種方法來改善這種情況:

改進封裝和冷卻技術

不要按 1:1 的比例拆分設計,而是將存儲單元放置在邏輯單元上 (Memory-on-Logic ,MoL)

或者反過來,將邏輯單元放置在存儲單元上 (Logic-on-Memory,LoM)

上圖左側顯示的是基線(全部位于一個裸片上),右側顯示的是相應的 3D 設計,整個設計對半拆分成頂部和底部裸片。

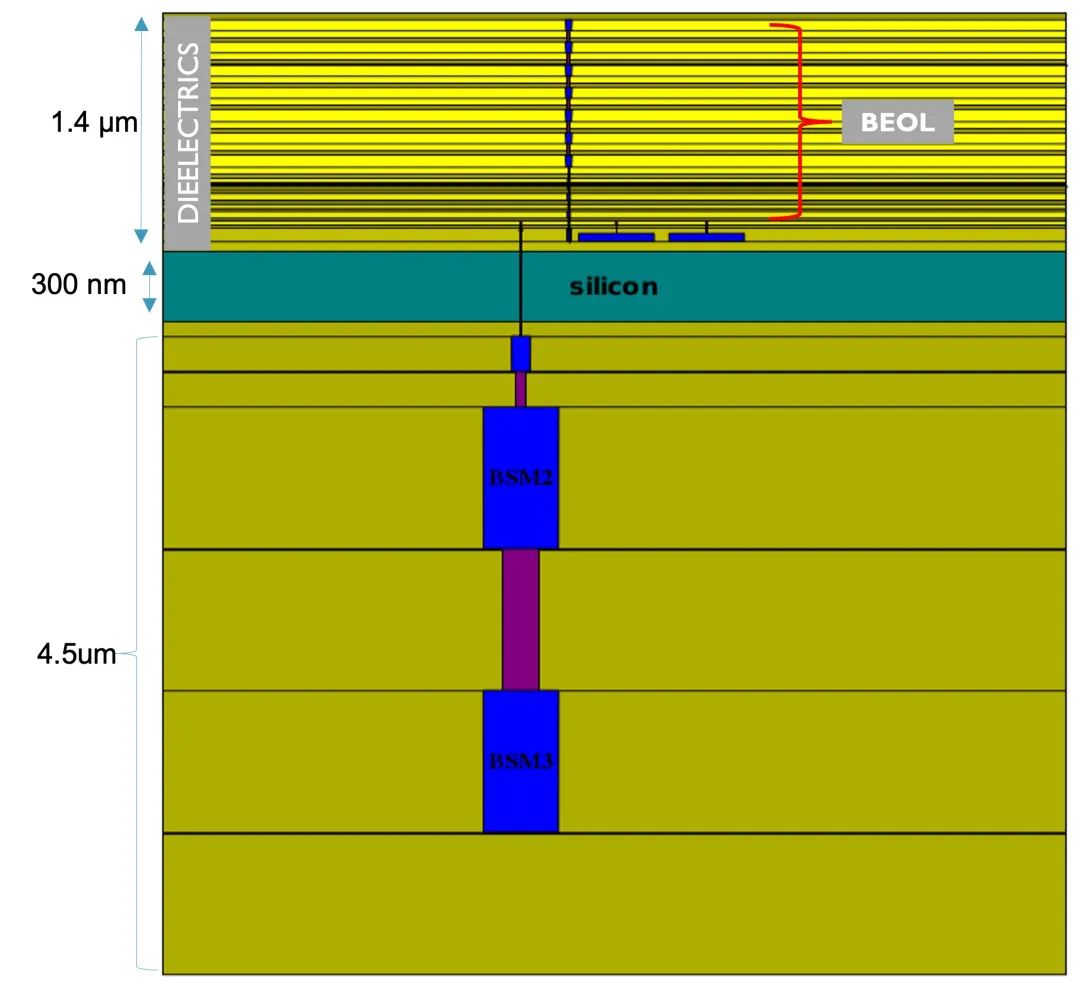

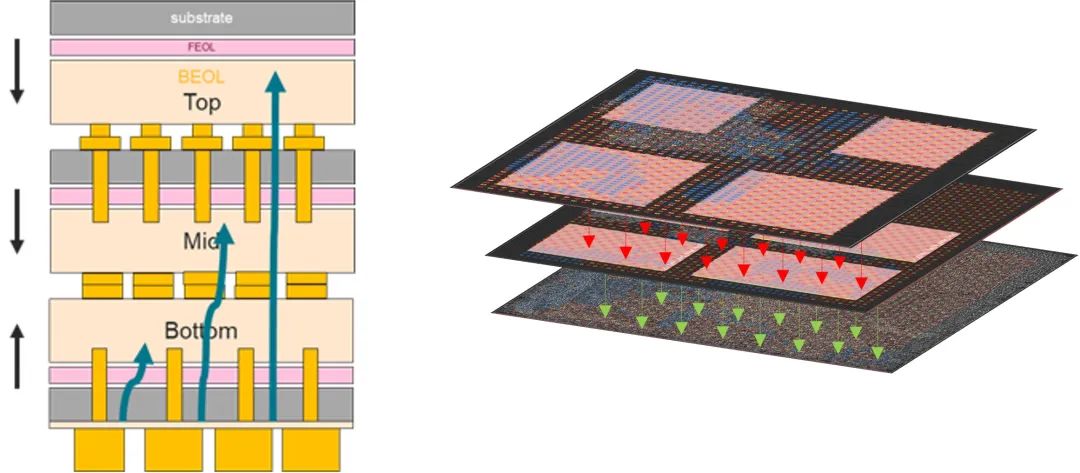

上圖是 3D 版本中各層的堆疊方式。底部裸片的基板厚度為 300 納米,總厚度為 6.2 微米。底層裸片有一個背面電源分配網絡 (Backside Power Delivery Network ,BSPDN)。頂部裸片沒有背面金屬,硅基板厚度為 500 微米,BEOL 厚度為 1.4 微米,總厚度為 501.4 微米。這是一個普通的正面電源分配網絡。

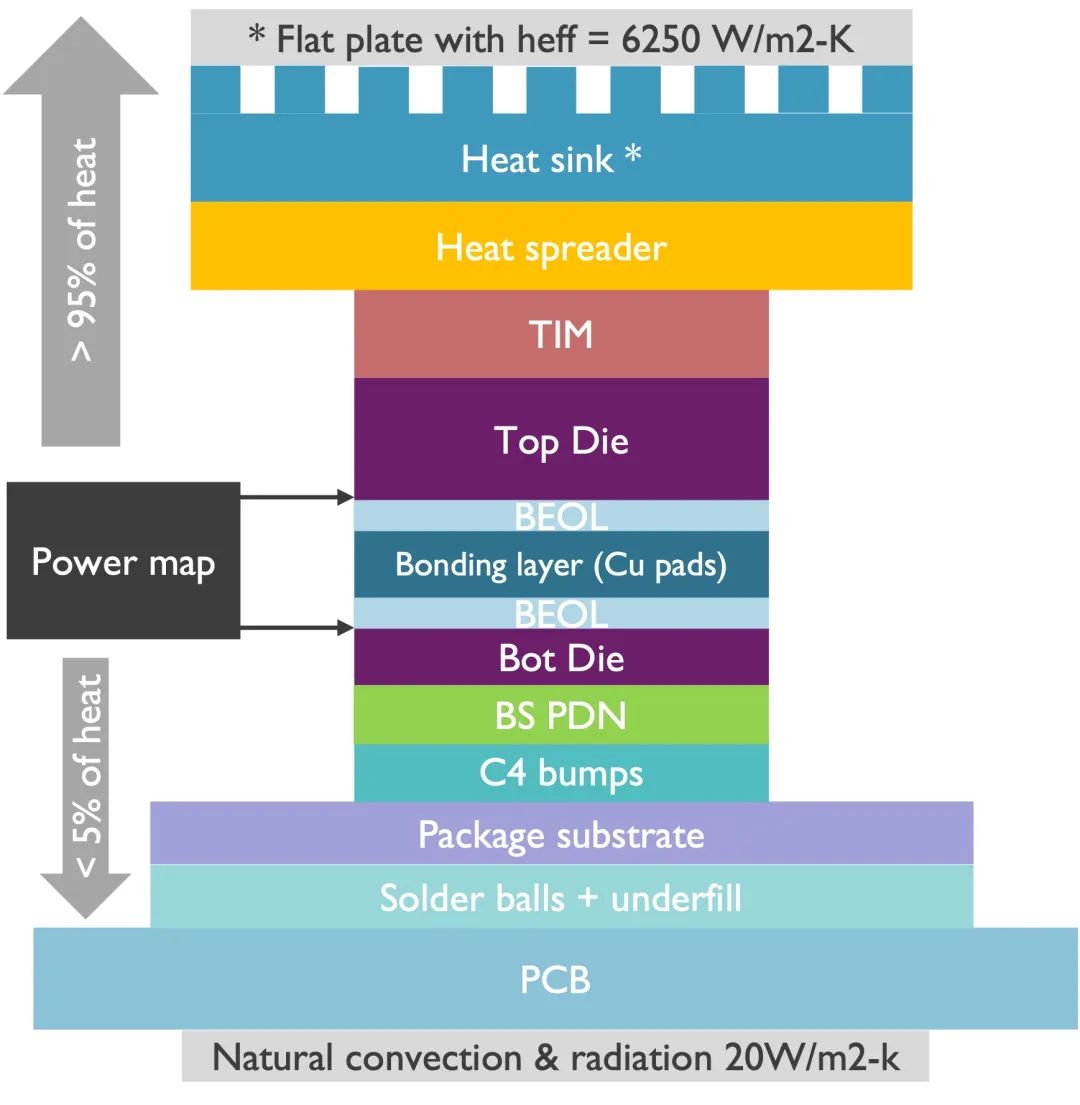

這不僅僅是兩個裸片那么簡單。底部有 PCB,還帶焊球,頂部有散熱器和散熱片,中間還有鍵合層。

實驗結果

以 1.5GHz 的工作頻率進行功耗密度評估,在活動性為 10% 時進行靜態功耗分析。邏輯裸片的功耗密度因更小的 footprint 和緩沖器的插入而有所增加。邏輯裸片的功耗密度比 2D 基線設計高 2.15 倍。

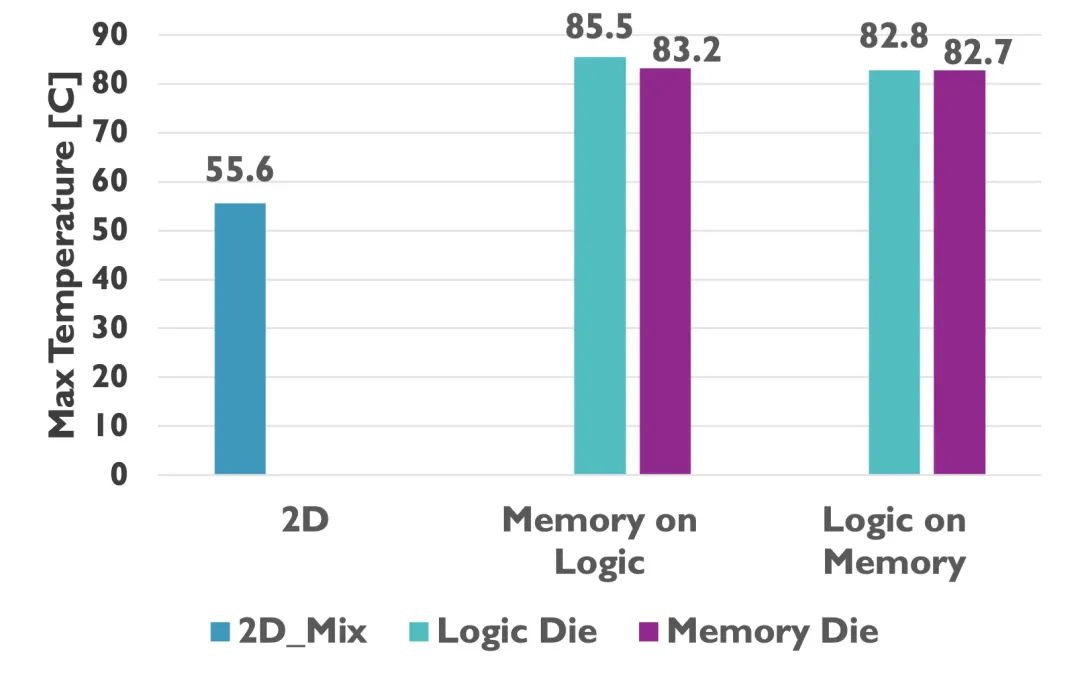

將 2D-Mix、MoL 和 LoM 進行比較,不難看出:由于采用了 BSPDN,底層裸片基底為 300 納米。對于采用 MoL 和 LoM 的 3D-IC,其最高溫度分別提高了 29.9°C 和 27.2°C(見上圖)。

三裸片堆疊

之所以采用堆疊三個而非兩個裸片的設計,是因為系統級芯片(SoC))以存儲器為主導。例如,一個擁有 L1 高速緩存、64 個內核、4 個 DMA 通道和 128 位寬 L2 高速緩存的多核 SoC,存儲器就占了 68% 的硅面積。

將三個裸片堆疊在一起,可以讓更多存儲器宏位于上層裸片上,從而改善 PPA。

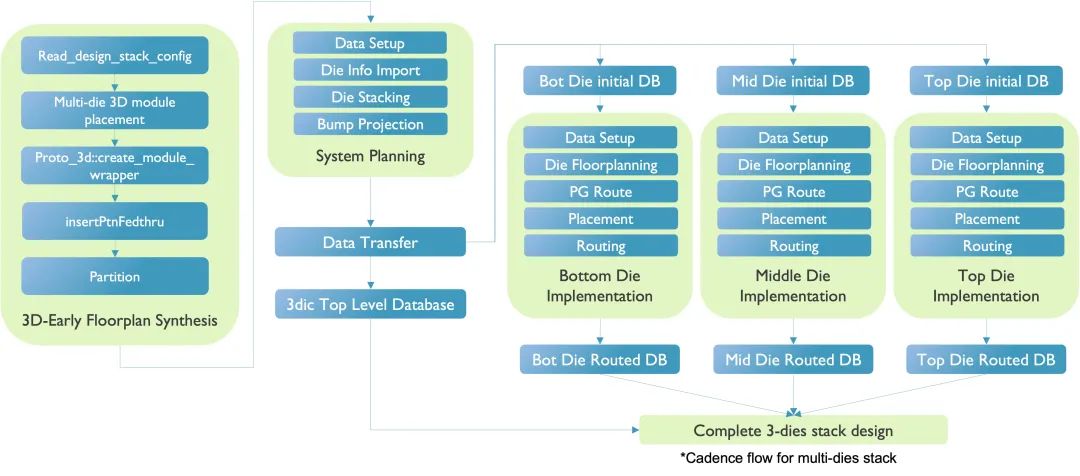

上圖展示了如何使用 Cadence Integrity 3D-IC 工具實現三裸片堆疊設計。

如上圖所示,它屬于存儲器-存儲器-邏輯堆疊,上面兩個裸片上只有存儲器。這項工作仍在進行中,因此 Mohamed 尚未報告功耗和散熱結果。

結論

與 2D 基線相比,3D 設計的溫度更高

LoM 的最高溫度比 MoL 的最高溫度低 2.7℃

在 3D-IC 設計中考慮熱效應非常重要:

兼顧熱影響的壓降(增加 4.7%)

兼顧熱影響的電源網絡阻抗(增加 2.8%)

多裸片(兩個以上)堆疊有望解決“內存墻”(Memory Wall) 瓶頸

下一步是為大型 SoC 實現三裸片堆疊,并進行全面的熱分析。

這些多裸片堆疊的最終結果是將 PPAC 變為 PPACT(功耗、性能、面積、成本、溫度)。

多裸片堆疊為設計人員提高良率、PPA、拓展功能提供了一種未來方向。從 PPAC 到 PPACT,Cadence Celsius Thermal Solver 與用于 IC 封裝/PCB 的 Sigrity 技術相集成,能夠實現精確的電熱協同仿真和熱分析,助力團隊應對熱升溫挑戰。

-

IC

+關注

關注

36文章

6103瀏覽量

178577 -

3D

+關注

關注

9文章

2953瀏覽量

110083 -

仿真

+關注

關注

51文章

4246瀏覽量

135394 -

2D

+關注

關注

0文章

67瀏覽量

15462

發布評論請先 登錄

HT 可視化監控頁面的 2D 與 3D 連線效果

芯片3D堆疊封裝:開啟高性能封裝新時代!

AN-1249:使用ADV8003評估板將3D圖像轉換成2D圖像

傅里葉光場顯微成像技術—2D顯微鏡實現3D成像

中興通訊攜手中國移動推出AI裸眼3D創新產品

中興通訊全場景AI終端應用與裸眼3D新品亮相

3D封裝熱設計:挑戰與機遇并存

裸眼3D筆記本電腦——先進的光場裸眼3D技術

紫光展銳助力全球首款AI裸眼3D手機發布

中興通訊與中國移動發布全球首創AI裸眼3D新品,引領3D科技新浪潮

英倫科技裸眼3D系列:革新視界,盡享未來科技魅力!

評論