一.硬件設計

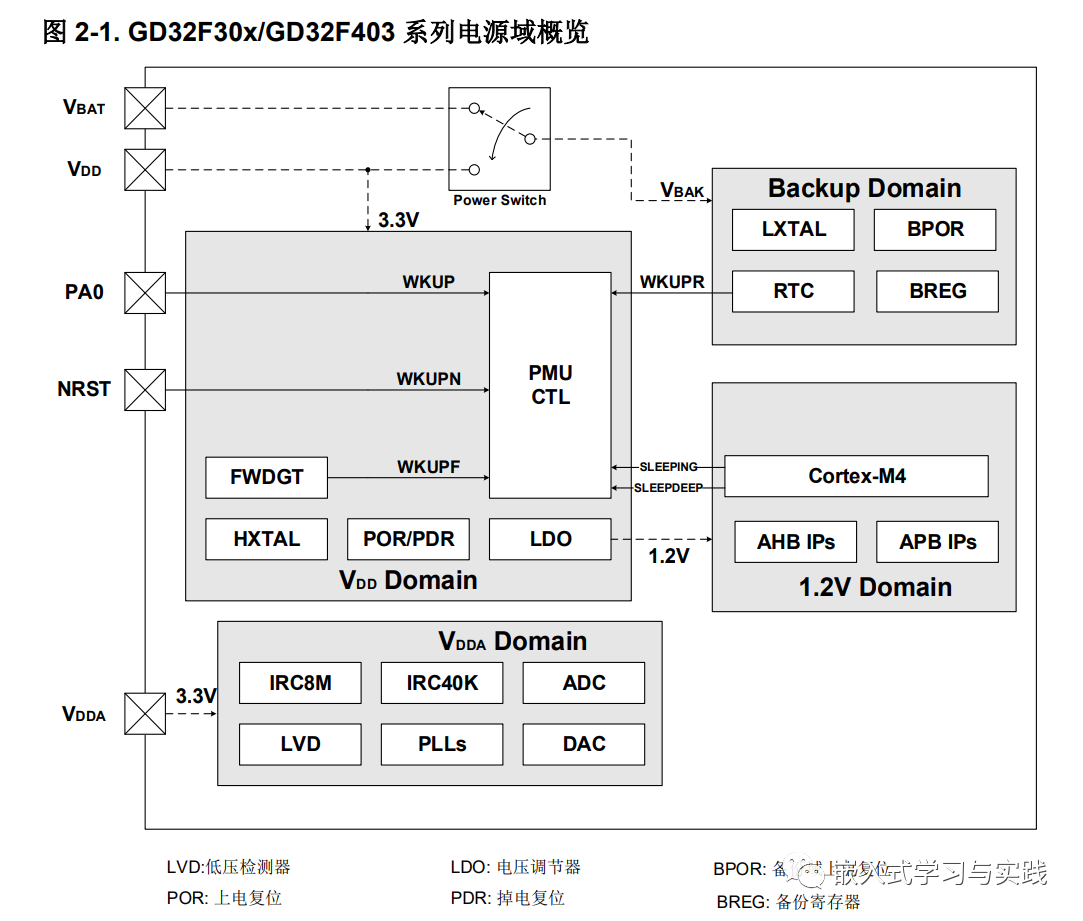

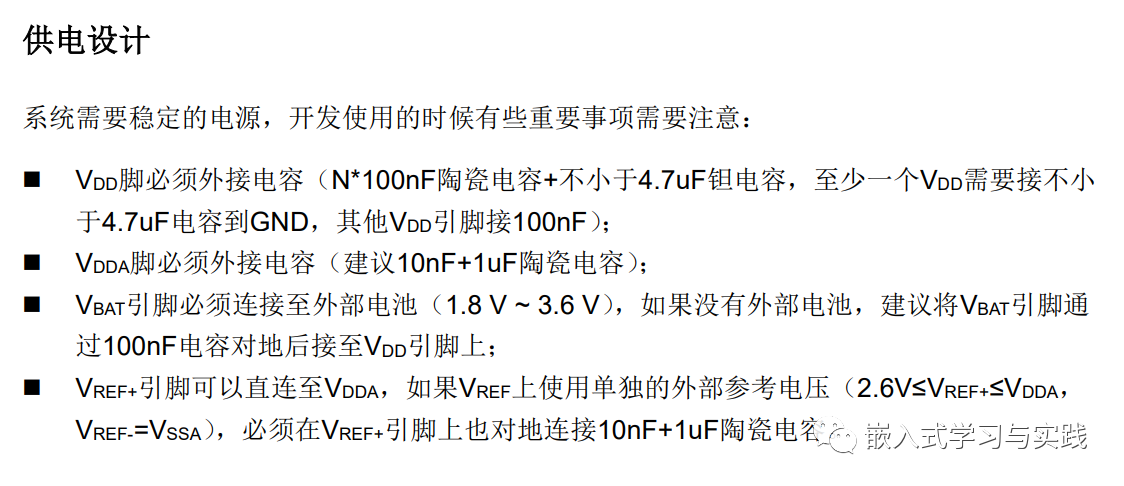

1.電源

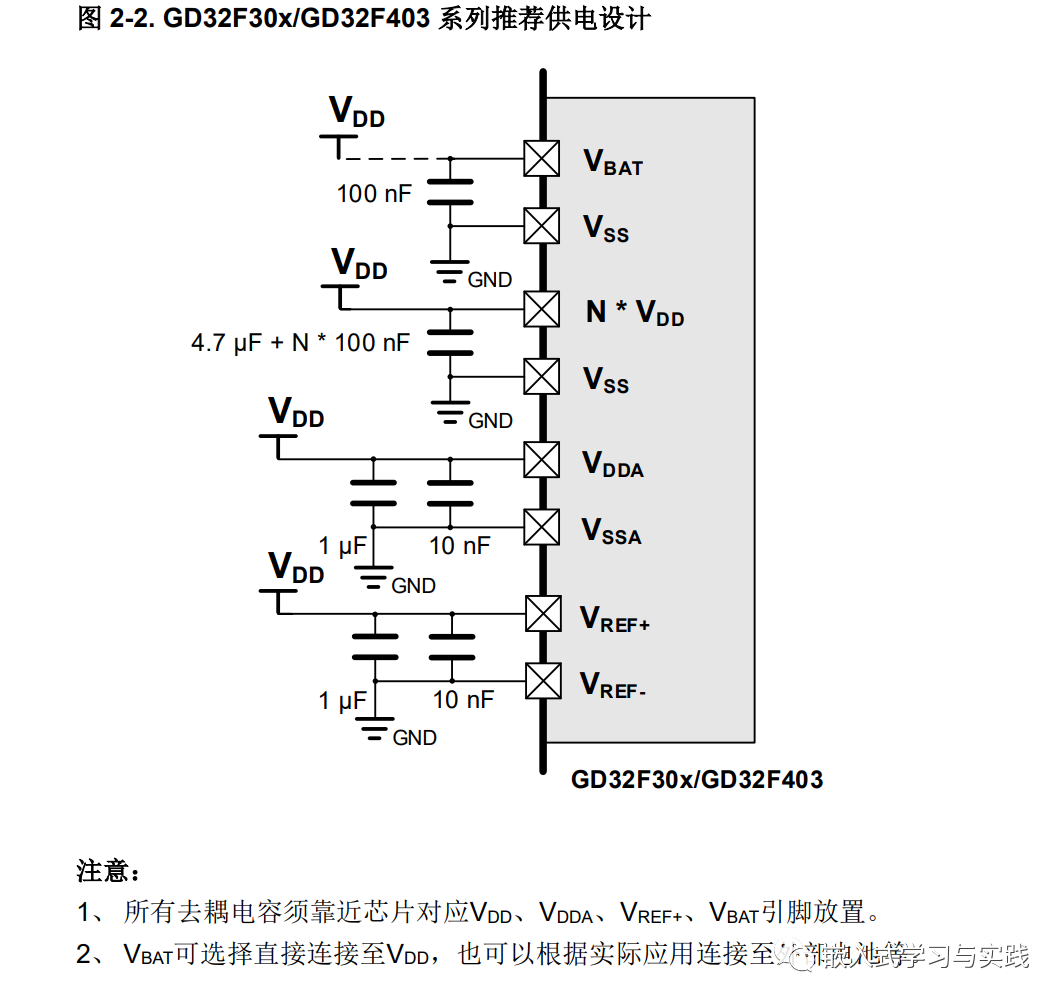

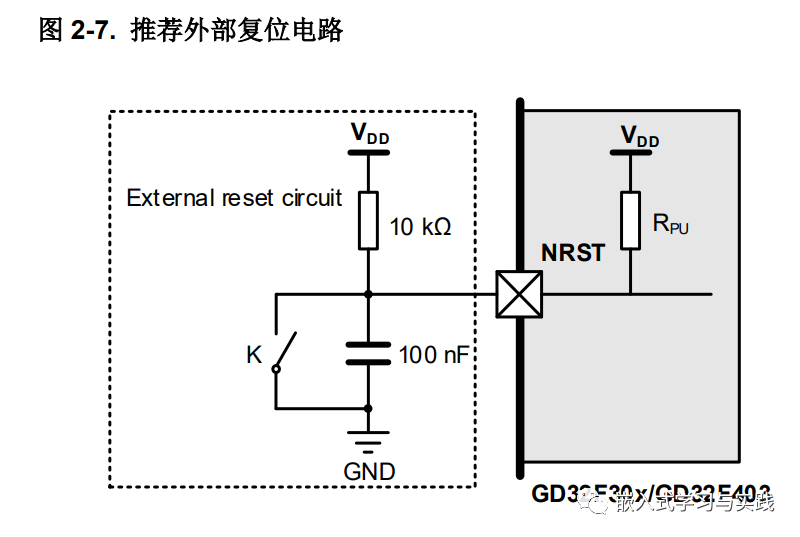

2.復位

注意:

1. 內部上拉電阻40kΩ,建議外部上拉電阻建議10kΩ,以使得電壓干擾不會導致芯片工作異常;

2. 若考慮靜電等影響,可在NRST管腳處放置ESD保護二極管;

3. 盡管MCU內部有硬件POR電路,仍推薦外部加NRST復位阻容電路;

4. 如果MCU啟動異常(由于電壓波動等),可適當增加NRST對地電容值,拉長MCU復位完成時間,避開上電異常時序區。

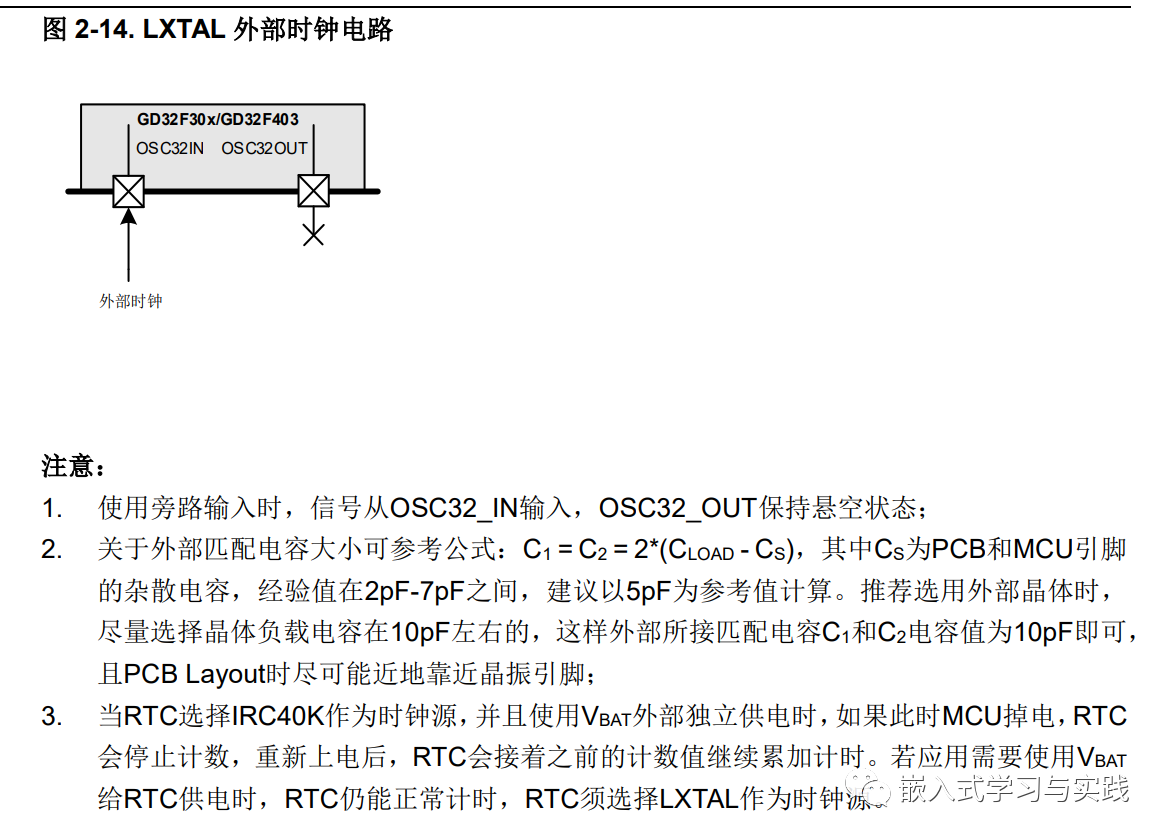

3.時鐘

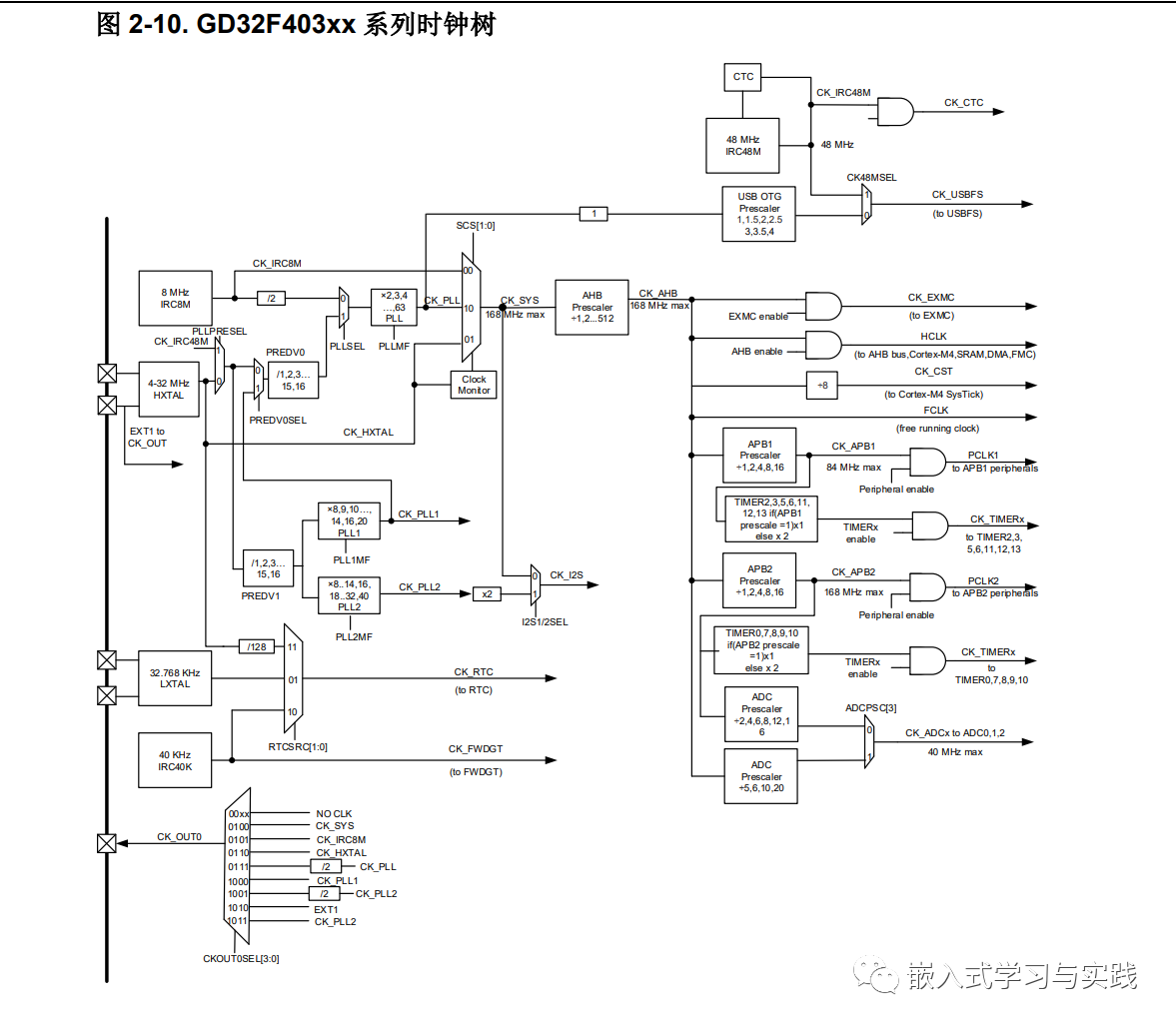

GD32F30x/GD32F403系列內部有完備的時鐘系統,可以根據不同的應用場合,選擇合適的時鐘源,時鐘主要特征:

4-32MHz外部高速晶體振蕩器(HXTAL);

8MHz內部高速RC振蕩器(IRC8M);

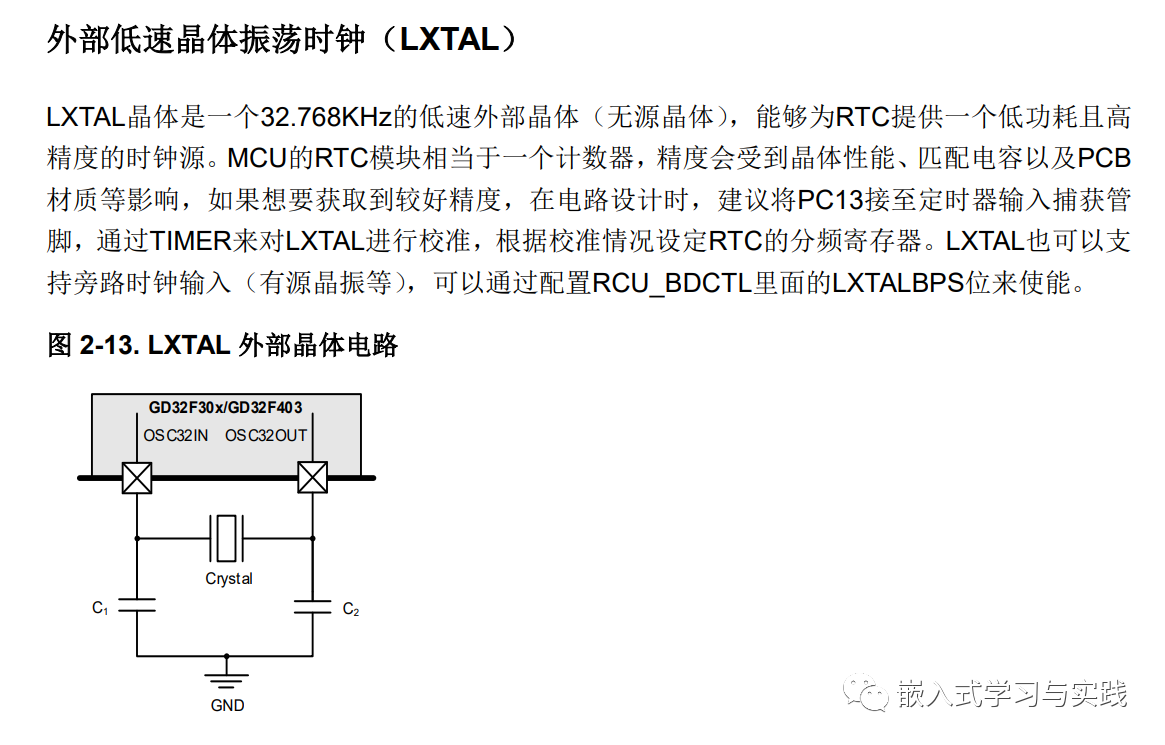

32.768KHz外部低速晶體振蕩器(LXTAL);

48 MHz內部高速RC振蕩器(IRC48M);

40kHz內部低速RC振蕩器(IRC40K);

PLL時鐘源可選HXTAL、IRC8M或IRC48M;

HXTAL時鐘可監控;

時鐘樹如下:

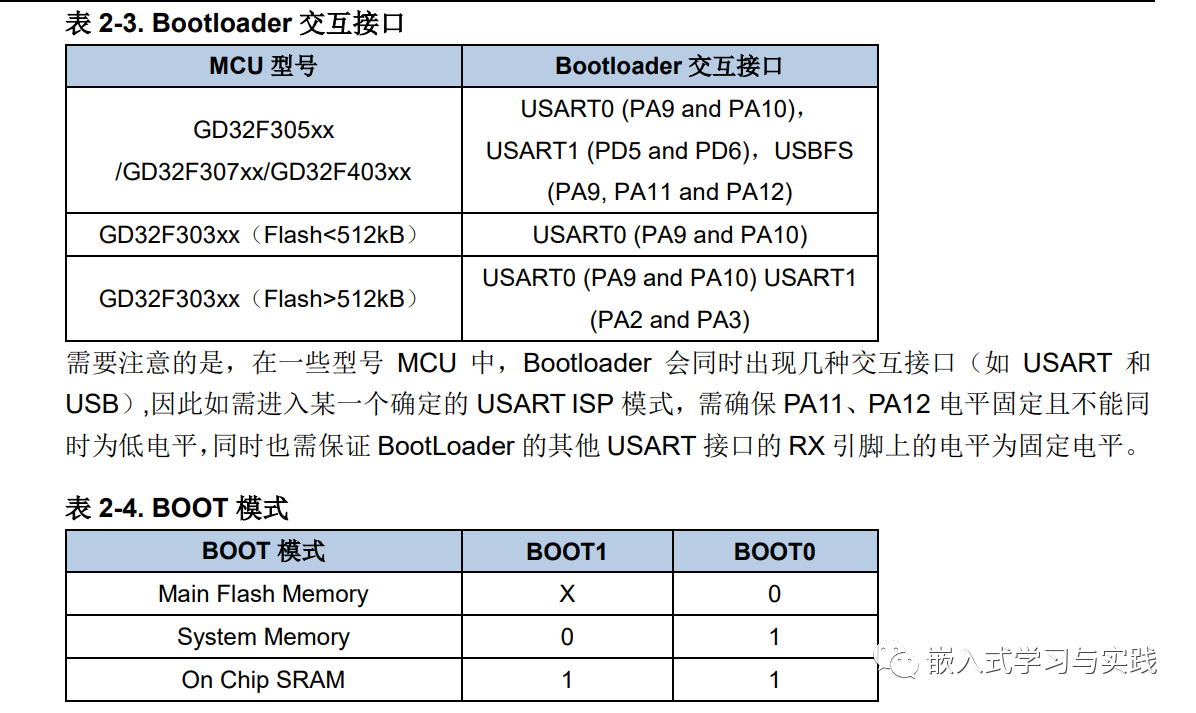

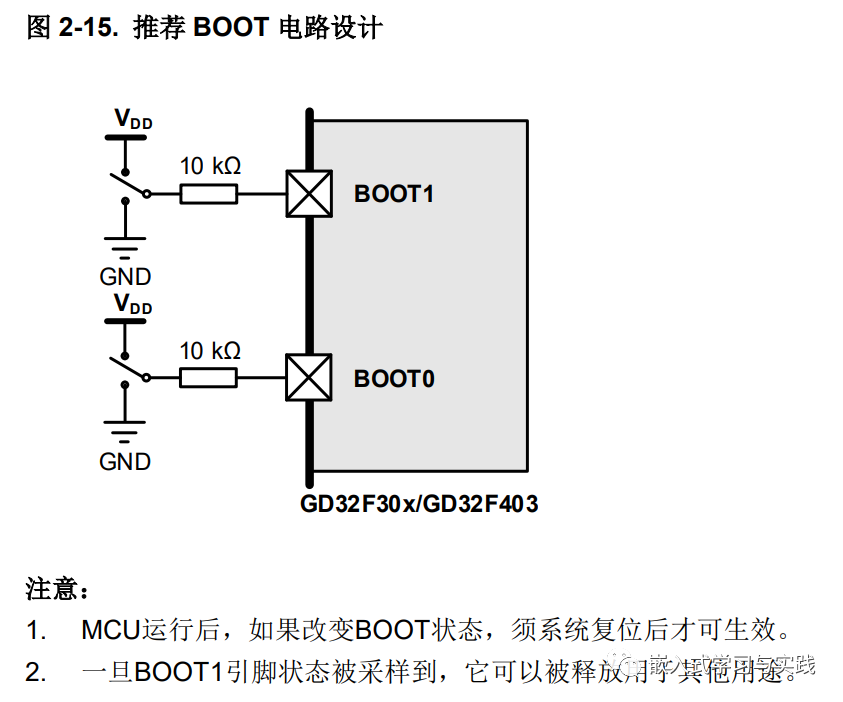

4.啟動配置

GD32F30x/GD32F403系列提供三種啟動方式,可以通過BOOT0和BOOT1來進行相關的配置。

用戶可以配置BOOT0和BOOT1,進行上電復位或系統復位,從而確定啟動選項。電路設計時,運行用戶程序,BOOT0不能懸空,建議通過一個10kΩ電阻到GND;運行System Memory進行程序更新,需要將BOOT0接高,BOOT1接低,更新完成后,再將BOOT0接低上電才能運行用戶程序;SRAM執行程序多用于調試狀態下。

嵌入式的 Bootloader 存放在系統存儲空間,用于對 FLASH 存儲器進行重新編程。在GD32F305xx/ GD32F307xx/ GD32F403xx設備中,Bootloader可以通過USART0 (PA9 andPA10),USART1 (PD5 and PD6),USBFS (PA9, PA11 and PA12)和外界交互。在GD32F303xx(Flash<512kB)設備中,Bootloader可以通過USART0 (PA9 and PA10) 和外界交互, 在GD32F303xx(Flash>512kB)設備中,Bootloader可以通過USART0 (PA9 and PA10) USART1(PA2 and PA3)和外界交互。

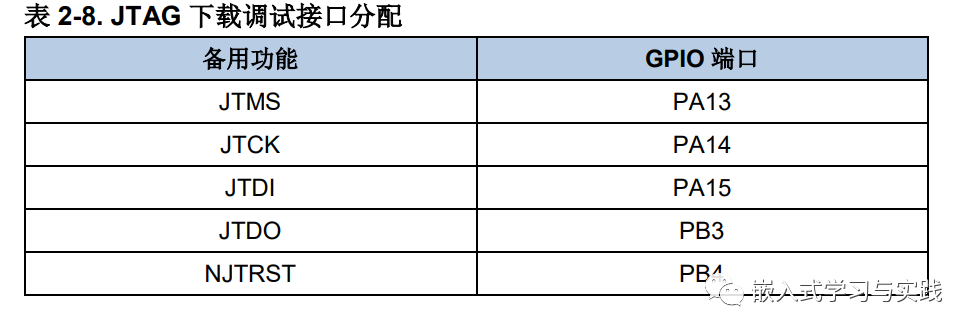

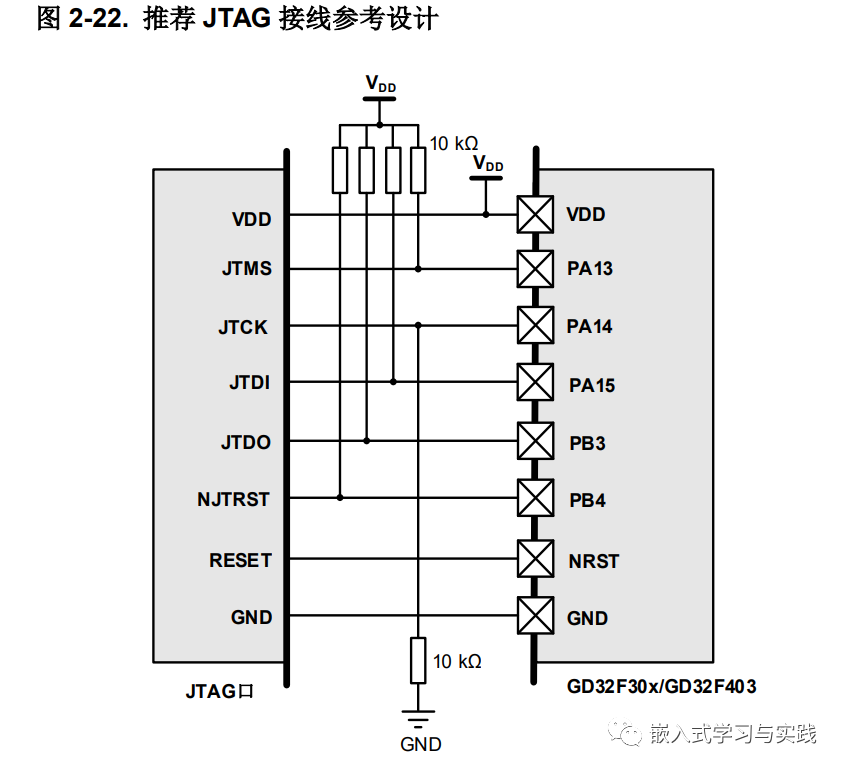

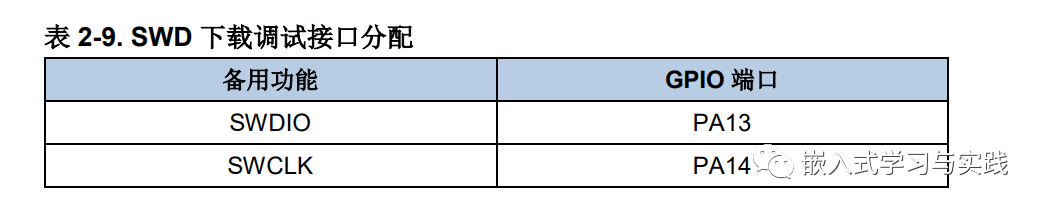

5.下載調試

GD32F30x/GD32F403系列內核支持JTAG調試接口和SWD接口。JTAG接口標準為20針接口,其中5根信號接口,SWD接口標準為5針接口,其中2根信號接口。

注意:復位后,調試相關端口為輸入PU/PD模式,其中:

PA15:JTDI為上拉模式;

PA14:JTCK / SWCLK為下拉模式;

PA13:JTMS / SWDIO為上拉模式;

PB4:NJTRST為上拉模式;

PB3:JTDO為浮空模式。

有以下幾種方式可以提高SWD下載調試通信的可靠性,增強下載調試的抗干擾能力。

1. 縮短SWD兩個信號線長度,最好15cm以內;

2. 將SWD兩根線和GND線編個麻花,纏在一起;

3. 在SWD兩根信號線對地各并幾十pF小電容;

4. SWD兩根信號線任意IO串入100Ω~1KΩ電阻。

6.典型外設

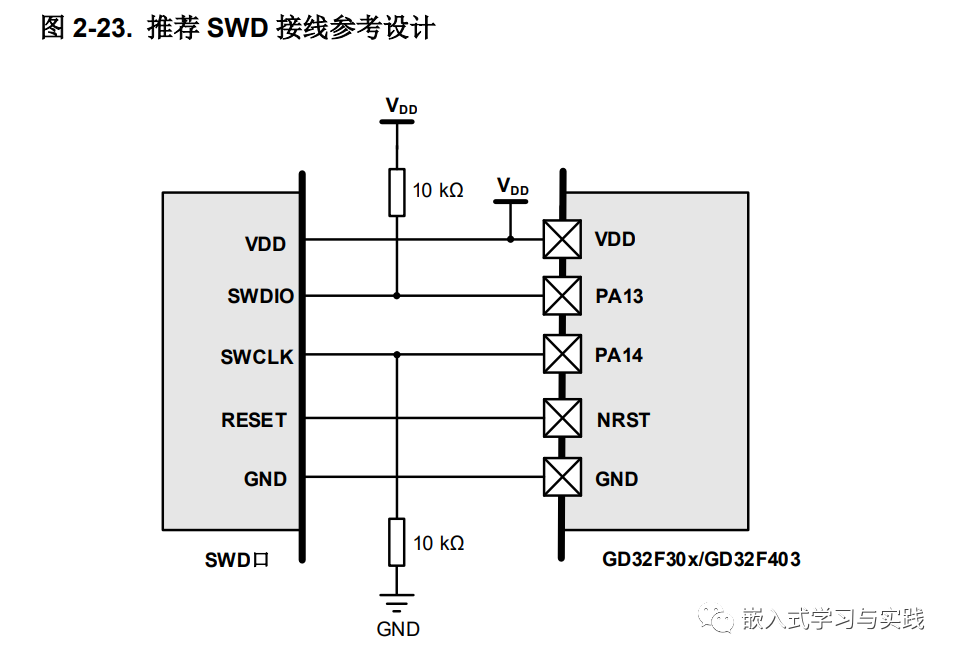

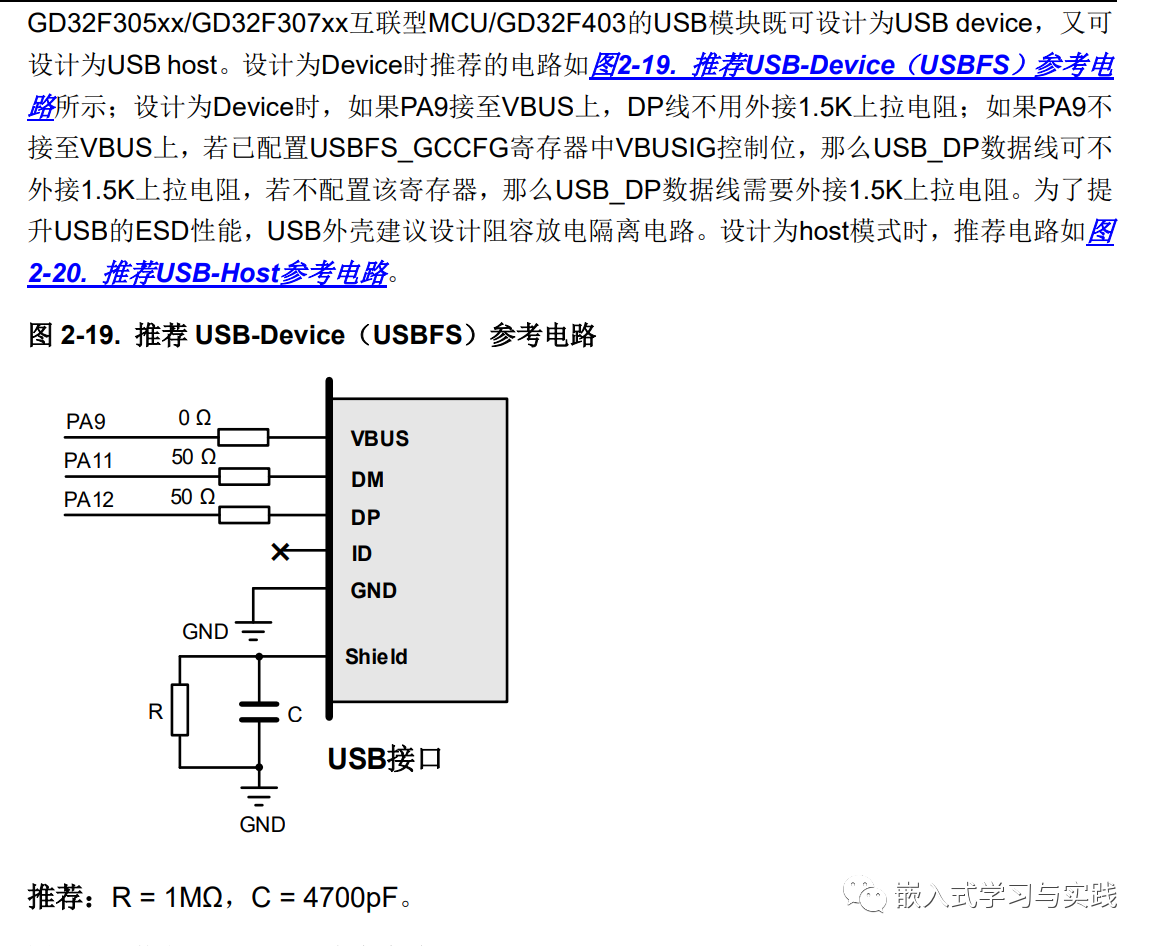

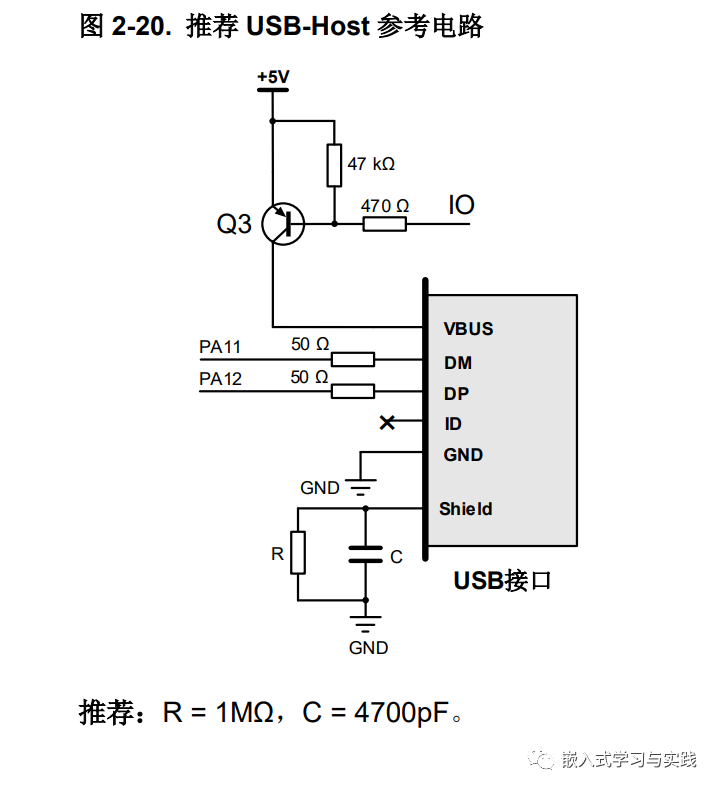

ubs外設電路

二.PCB Layout

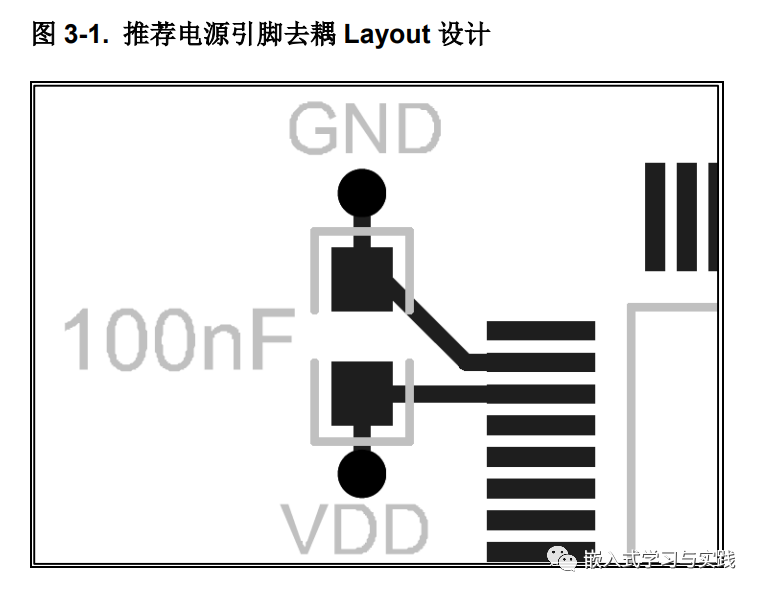

1.電源去耦電容

GD32F30x/GD32F403系列電源有VDD、VDDA、VREF+和VBAT四個供電腳,100nF去耦電容采用陶瓷即可,且需要保證位置盡可能地靠近電源引腳。電源走線要盡量使得經過電容后再到達MCU電源引腳,建議可通過靠近電容PAD處打Via的形式Layout。

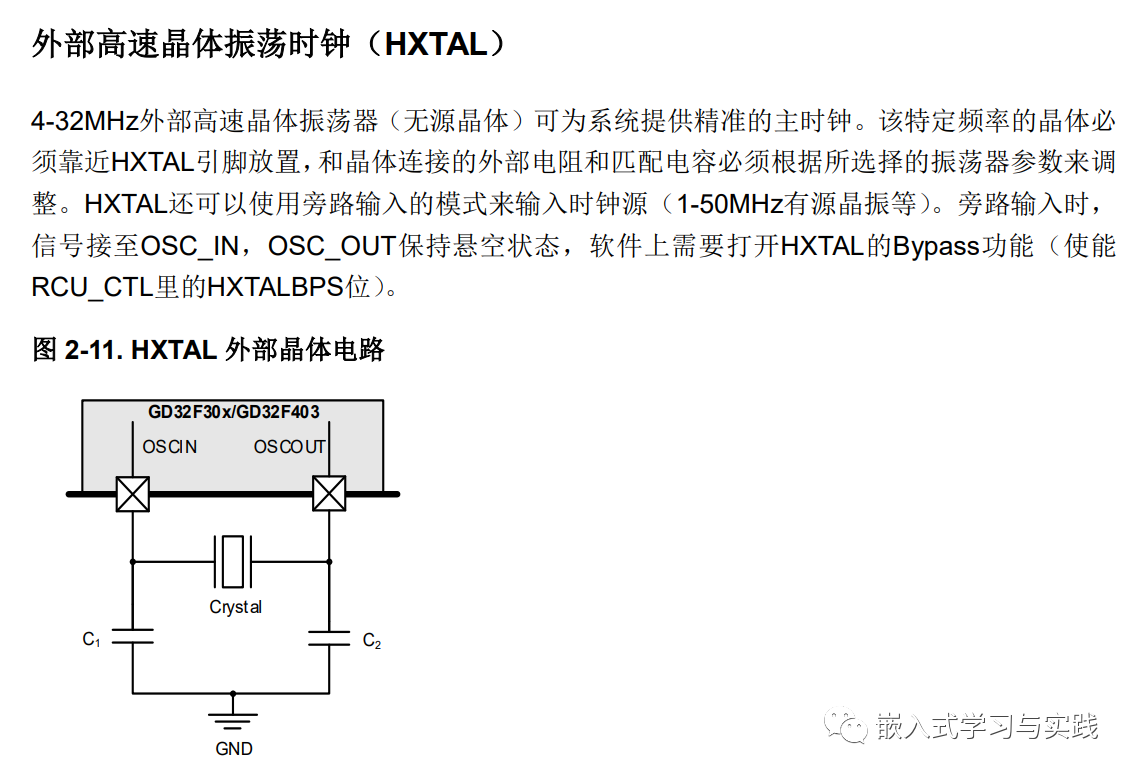

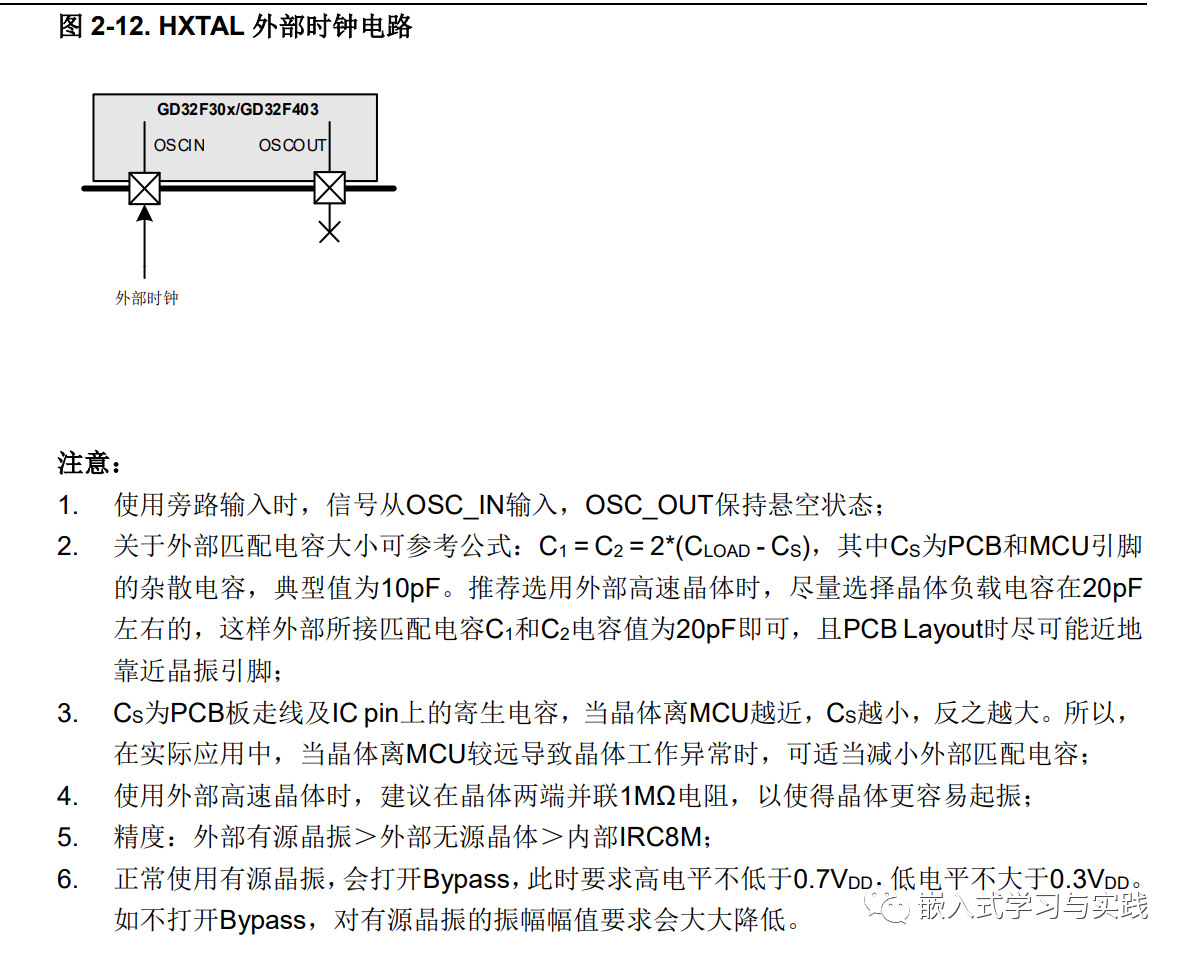

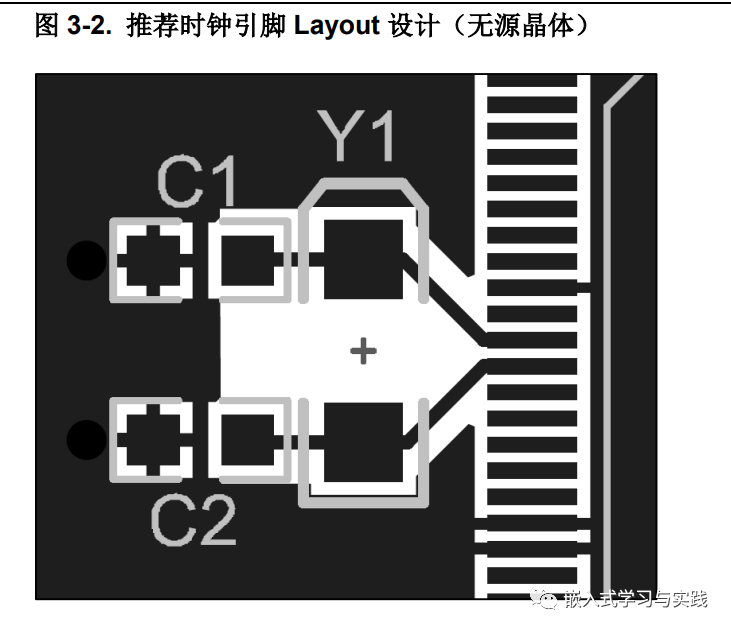

2.時鐘電路

GD32F30x/GD32F403系列時鐘有HXTAL和LXTAL,要求時鐘電路(包括晶體或晶振及電容等)靠近MCU時鐘引腳放置,且盡量時鐘走線由GND包裹起來。

注意:

1. 晶體盡量靠近MCU時鐘Pin,匹配電容等盡量靠近晶體;

2. 整個電路盡量與MCU在同層,走線盡量不要穿層;

3.時鐘電路PCB區域盡量禁空,不走任何與時鐘無關走線;

4. 大功率、強干擾風險器件及高速走線盡量遠離時鐘晶體電路;

5.時鐘線進行包地處理,以起到屏蔽效果。

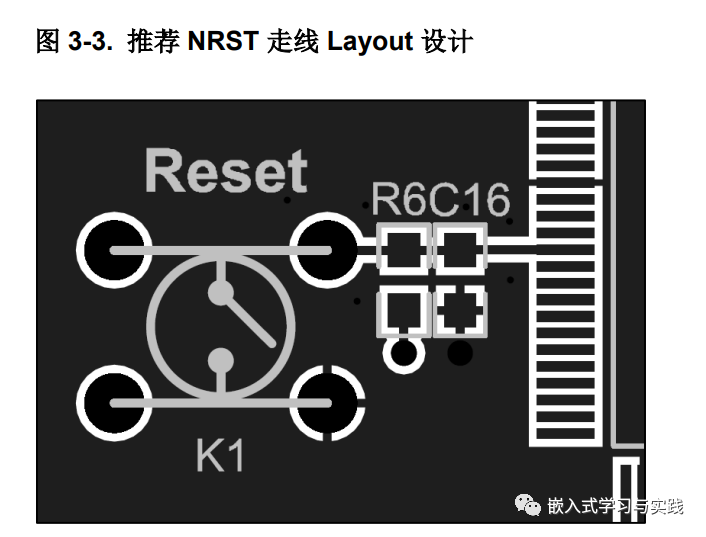

3.復位電路

注意:復位電路阻容等盡可能地靠近MCU NRST引腳,且NRST走線盡量遠離強干擾風險器件及高速走線等,條件允許的話,最好將NRST走線做包地處理,以起到更好的屏蔽效果。

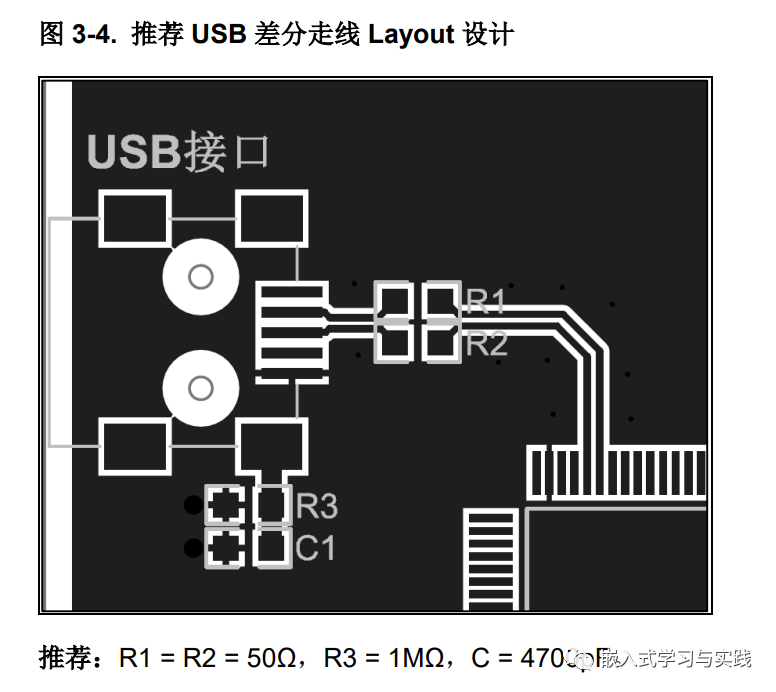

4.USB 電路

USB模塊有DM、DP兩根差分信號線,建議PCB走線要求做特性阻抗90ohm,差分走線嚴格按照等長等距規則來走,且盡量使走線最短,如果兩條差分線不等長,可在終端用蛇形線補償短線。

由于阻抗匹配考慮,串聯匹配電阻建議50Ω左右即可。當USB終端接口離MCU較遠的時候,需要適當增大該串聯電阻值。

注意:

1.布局時擺放合理,以縮短差分走線距離;

2. 優先繪制差分線,一對差分線上盡量不要超過兩對過孔,且需要對稱放置;

3. 對稱平行走線,保證兩根線緊密耦合,避免90°、弧形或45°走線方式;

4. 差分走線上所接阻容、EMC等器件,或測試點,也要做到對稱原則。

對于USB HS模塊,MCU與外部HS PHY之間的數據線與信號控制線也盡量走短,需要用蛇形線做等長處理,注意事項如下:

1.布局時擺放合理,USB HS-PHY芯片與MCU之間盡量緊湊;

2. 布線時,以信號線中最長的一根線長度為目標,將其他信號線通過蛇形走線補償即可。

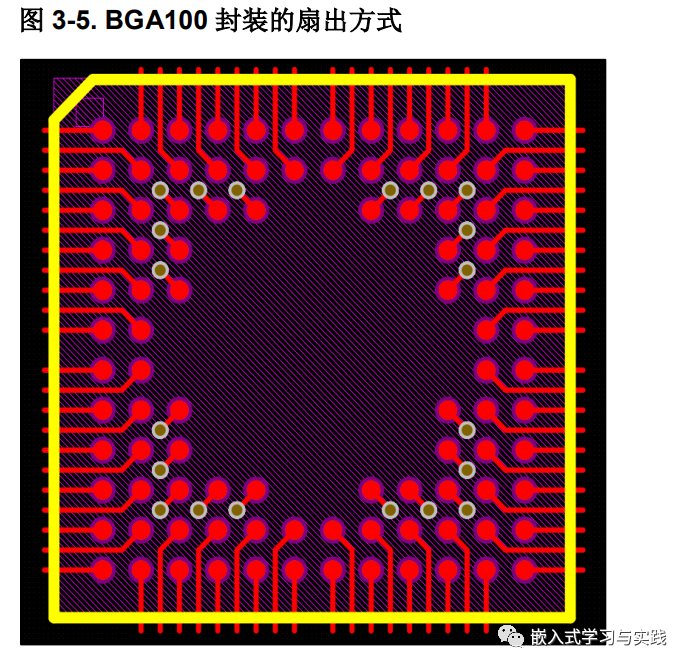

5.BGA 走線

GD32F403x 系列中包含 BGA100 的封裝,對應的型號為 GD32F403VxH6,該芯片走線和其它 BGA 芯片類似,先對各個球型焊盤進行扇出,再進行布線操作。對于0.5 mm Pitch 的 BGA封裝,若將 BGA 焊盤大小設置為 0.25/0.35,過孔距焊盤以及線寬線距為 3 mil 時,可以使用Dog bone 型扇出,扇出后如圖 3-5. BGA100 封裝的扇出方式所示,過孔距焊盤距離為 4.5mil;但此種布線對 PCB 制造商工藝要求較高,需與 PCB 制造商溝通后再進行布線,若制造商工藝達不到要求,可對此BGA 封裝打盤中孔以及盲埋孔

來源: 嵌入式學習與實踐

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理

審核編輯 黃宇

-

單片機

+關注

關注

6035文章

44554瀏覽量

634675 -

mcu

+關注

關注

146文章

17125瀏覽量

350996 -

pcb

+關注

關注

4319文章

23081瀏覽量

397525 -

Layout

+關注

關注

14文章

403瀏覽量

61741

發布評論請先 登錄

相關推薦

【高手問答】從事單片機軟硬件開發15年的工程師們,與您探討單片機軟硬件設計

單片機硬件學習思路

多個單片機硬件系統的案例分析

單片機數據采集系統PCB板制作

【畢設狗】【單片機畢業設計】基于單片機的溫控水杯的設計(實物+proteus仿真+源碼+原理圖+PCB+軟件設計流程

單片機新手指導3:STM32單片機學習步驟---偏硬件方向

單片機硬件設計和PCB Layout參考

單片機硬件設計和PCB Layout參考

評論