又到了一年一度的招聘季節,有粉絲私信問了一個問題,一個關于以前流傳出來的大廠面試的題目,個人覺得算是比較經典的題目,也是工作中經常遇到的一個問題,所以準備寫一篇回答下。

題目內容

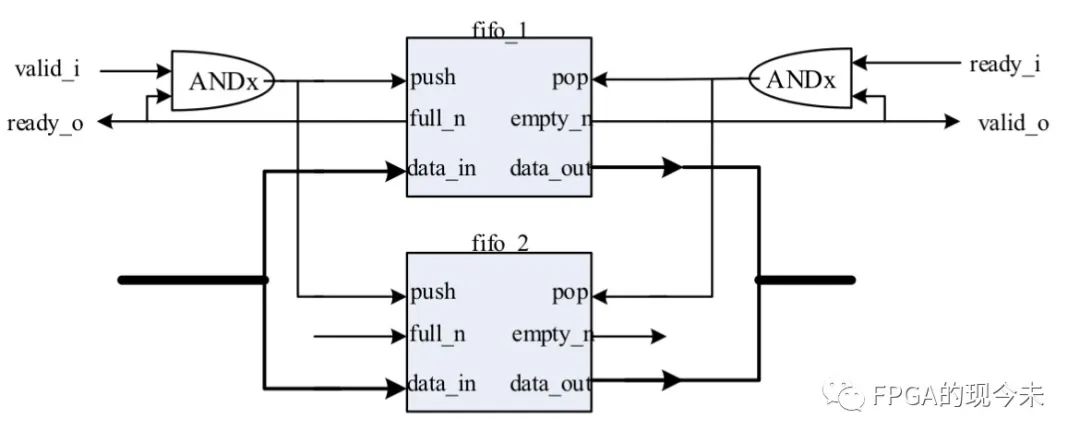

有一個數據需要從A時鐘域同步到B時鐘域,數據位寬是512bit的,但是考慮到其他原因,目前只允許使用256bit異步FIFO(已經考慮空度滿寫的保護),因此設計了一個方案,如下圖所示,請問該方案有什么問題?如何優化?

分析

通過上圖我們可以看到,512bit的數據,被分成了2組256bit的數據,采用同一個寫使能信號寫入到2個不同的異步FIFO中。在讀這一側,通過一個FIFO的空信號,同時將2個FIFO中的數據讀出來。乍一看起來好像沒有什么問題,且仿真的話,也不會有問題。但是在實際芯片中卻不是這么回事。主要的錯誤就是誤認為完全相同的異步FIFO在空、滿信號狀態上表現也一樣。

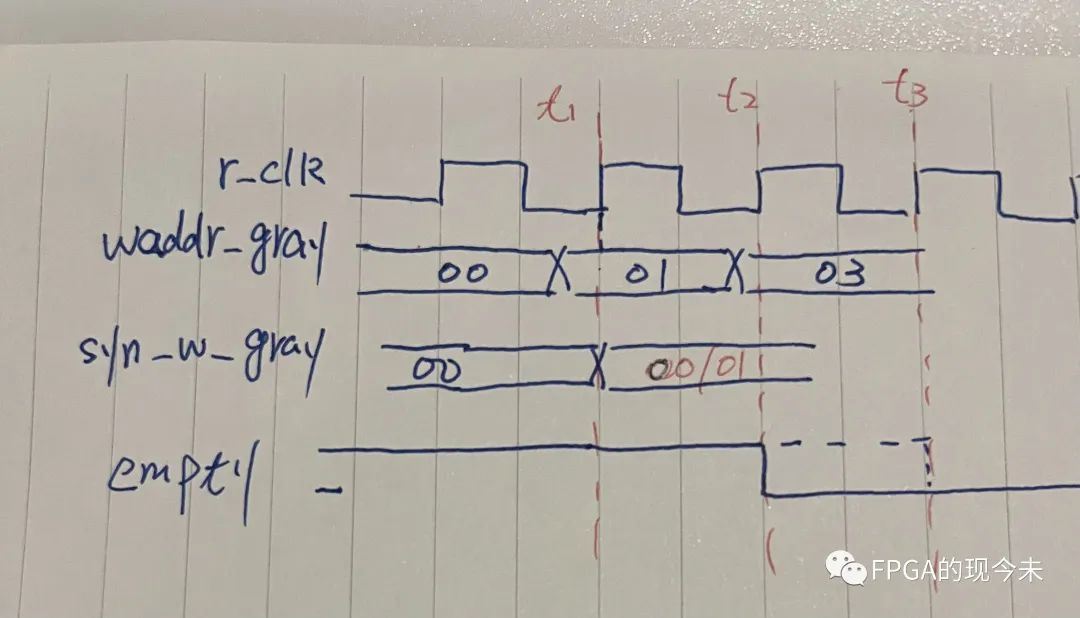

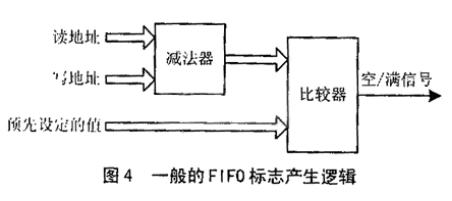

我們知道異步FIFO的空滿信號是通過格雷碼地址經過轉換后比較得到的,而格雷碼在穿越異步時鐘域的時候,由于亞穩態,有可能造成穿越的結果出現延遲。如下圖所示,在t1時刻,寫地址的格雷碼已經由00變成01,即寫入了一個數據。讀時鐘r_clk在采樣的過程中,由于亞穩態寫地址同步后,可能得到01,或者00,如果得到01,那么在t2時刻empty信號就可以拉低了,如果是00,那么在t2時刻empty不會拉低,需要在t3時刻拉低。

一句話總結,對于2個完全一樣的異步FIFO,即使同時寫入數據,在讀時鐘域,empty信號的產生也是不一樣的,同樣,在寫時鐘域,full信號的產生也是不一樣的。

解決方案

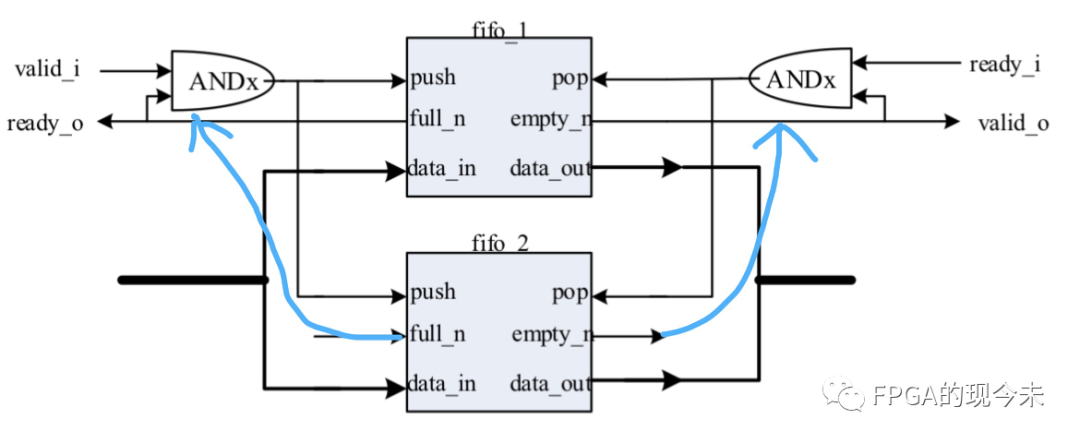

這個問題的解決方案其實很簡單,寫入測,ready_o信號的產生不能只使用fifo_1的滿信號,也要使用fifo_2的滿信號,即ready_o = full1_n & full2_n(full低電平有效)。同理,在讀數據的時候,不能只看fifo_1是否空,必須是2個fifo都不空的時候才可能讀數據。

總結

其實上面這個題目在實際項目是經常用到的。2個FIFO被同時寫入的時候,默認為2個FIFO是同時不空的,通過上面的分析,我們知道異步FIFO不是這么回事,那同步FIFO呢?理論上來講,同步FIFO是同時不空的。但是不同廠家設計的FIFO,其特性可能也有差異,從代碼的可移植性和可靠性來講,也不建議采用一個FIFO為空就推斷另一個FIFO也為空的方案,必須嚴格遵守:使用哪個FIFO,就要使用它的空、滿信號。

-

fifo

+關注

關注

3文章

387瀏覽量

43651 -

信號

+關注

關注

11文章

2790瀏覽量

76731 -

時鐘域

+關注

關注

0文章

52瀏覽量

9535 -

異步FIFO

+關注

關注

0文章

20瀏覽量

8354

發布評論請先 登錄

相關推薦

面試問題-難忘的面試經歷

異步FIFO結構及FPGA設計

高速異步FIFO的設計與實現

Camera Link接口的異步FIFO設計與實現

異步FIFO結構及FPGA設計

異步FIFO的設計分析及詳細代碼

基于FPGA的異步FIFO設計方法詳解

基于異步FIFO結構原理

異步FIFO相關面試問題

異步FIFO相關面試問題

評論