01時鐘方案

1、避免內部產生時鐘

我們設計時要盡可能避免在內部產生時鐘,如果操作不當,會導致設計功能和時序問題。總而言之,盡量在代碼中避免操作時鐘。

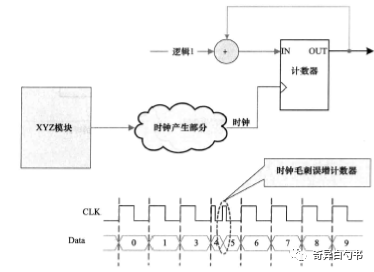

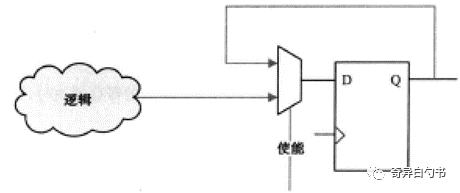

組合邏輯搭建的時鐘會引入毛刺,使功能出現問題,數據輸入有毛刺會被過濾,但是時鐘端毛刺會有明顯問題。如圖所示為組合邏輯產生的時鐘效果。

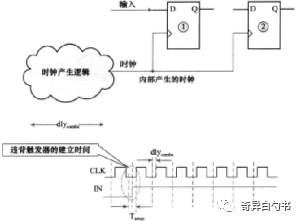

解決辦法:在組合邏輯產生的時鐘后面加入一個寄存器,用寄存器輸入作為后續的時鐘輸入。但是由于組合邏輯會增加時鐘線上的延遲,在一些情況下,邏輯延遲會導致時鐘偏移比兩個寄存器之間的數據延遲大。這樣會違背寄存器的時序要求。

2、分頻時鐘

在設計中盡量保證所需的時鐘來自PLL。若要對主時鐘進行分頻時,始終使用同步計數器或者狀態機。產生輸出時鐘時用寄存器進行輸出,而不應該用組合邏輯。

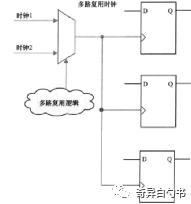

3、多路時鐘復用

多路時鐘復用器,可以使同一個邏輯擁有不同的時鐘。前提是得滿足以下標準:

- 在初始化配置后,時鐘多路邏輯就不再改變;

- 在測試時,設計會繞過功能時鐘多路邏輯而選擇普通時鐘;

- 在時鐘切換時,寄存器始終處于復位狀態;

- 在時鐘切換時產生的短暫錯誤響應沒有負面影響

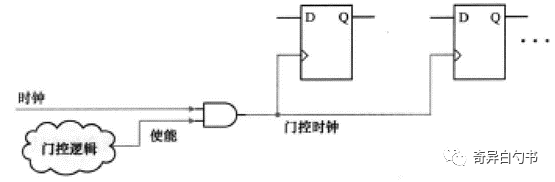

4、門控時鐘

門控時鐘使用使能信號開關時鐘,實現對某些門控電路的控制。在時鐘關閉時,對應的時鐘域的寄存器就會停止翻轉。所以門控時鐘時減少功耗的有效手段之一。

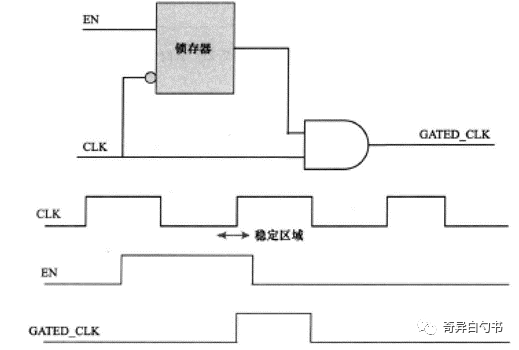

顯而易見,這種方式并不是同步設計,會導致時鐘偏移以及毛刺現象。下圖是同步時鐘門控使能,不過此種方式由于時鐘一直在不停的驅動,雖然后面寄存器輸出保持不變,卻并沒有停止工作,因此不能達到降低功耗的作用。

那有沒有既滿足同步要求又降低功耗的設計呢?

首先需要知道功耗到底耗在哪。傳統的同步設計中,系統時鐘連接到每個寄存器的時鐘端,這使得功耗主要由三個部分組成:

- 在時鐘沿變化的組合邏輯所產生的的功耗

- 由觸發器產生的功耗

- 設計中時鐘樹產生的功耗

時鐘門控能夠大幅降低觸發器的功耗,時鐘門控可以存在于時鐘樹的根部、末端或者兩者之間任何位置。由于 時鐘樹幾乎消耗了整個芯片功耗的50% ,因此最好始終在根部產生或者關閉時鐘。

基于鎖存器的門控時鐘電路是在上述門控時鐘電路中加入一個電平敏感時鐘的鎖存。其只需要保證EN信號在時鐘上升沿附近穩定不變就可以。如此就可以保證輸出不含任何毛刺與尖峰脈沖。

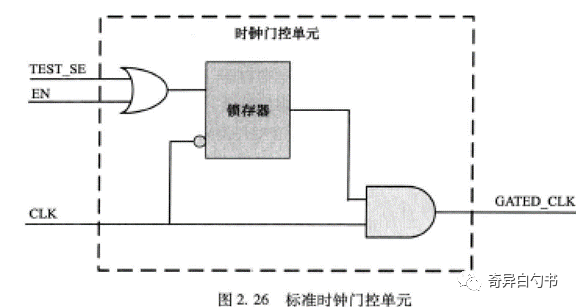

為了保證較高的生產缺陷覆蓋率,有必要保證在插入掃描鏈時門控時鐘電路是完全可控和可觀察的。加入Test控制信號,使得測試狀態下不管使能值是多少都能被時鐘驅動。大多數ASIC生產商都提供“門控時鐘單元”作為標準單元庫的一部分。

02復位信號設計方案

復位的基本目的是使SoC進入一個能進行穩定操作的確定狀態 。好的設計會在系統沒有明確要求的情況下為SoC的每個觸發器都提供復位信號。但是在某些情況下,當流水線的寄存器在高速應用中使用時,應該去掉某些寄存器的復位信號以使設計達到更高的性能。

1、同步復位和異步復位

同步復位: 復位信號只有在時鐘的有效沿到來時才能影響或者復位觸發器的狀態。

同步復位的優點:

1)同步復位一般能確保電路100%同步;

2)同步復位會綜合為更小的觸發器;

3)同步復位確保復位只發生在有效時鐘沿,可過濾毛刺。

同步復位缺點:

1)同步復位可能需要一定長度的脈寬,保證時鐘有效沿附近復位信號有效;

2)復位信號可能經過多級組合邏輯,會存在潛在問題;

3)復位電路需要復位時鐘,門控時鐘電路中,可能因為時鐘無效導致復位無效。

異步復位: 復位觸發器在設計時加入了一個復位引腳,通過復位信號直接控制。

異步復位優點:

1)保證數據路徑上的整潔干凈;

2)不管有沒有時鐘都可以復位。

異步復位缺點:

1)異步復位信號不一定可以被I/O口直接驅動;

2)異步復位為異步過程,撤銷異步信號時,若剛好處于時鐘有效沿,會使電路進入亞穩態;

3)板機系統或者其他造成的噪聲毛刺引起偽復位。

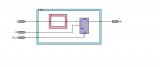

2、常用的解決方案:異步復位,同步釋放。

所謂異步復位同步釋放,是指復位信號到來時不受時鐘信號的同步,復位信號釋放時需要進行時鐘信號的同步。

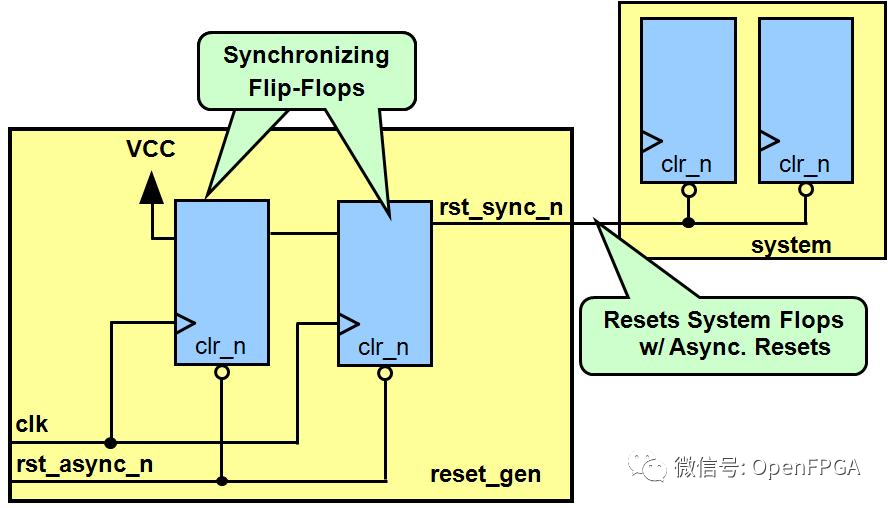

上圖清楚地展示了異步復位和同步釋放兩個階段。

異步復位階段:當rst_async_n有效時,此時第二個D觸發器的輸出rst_sync_n立即置為低電平,實現異步復位。

同步釋放階段:假設rst_async_n在clk的上升沿時撤除,那么第一級觸發器處于亞穩態,但是由于兩級觸發器的緩沖作用,第二級觸發器的輸入為clk到來前第一級觸發器的輸出,即為低電平。因此,此時第二級觸發器的輸出一定是穩定的低電平,方框左中觸發器仍然處于復位狀態。在下一個clk到來時,第一級觸發器的輸出已經是穩定的高電平了,故rst_sync_n已經是穩定的高電平,此時復位釋放,實現同步釋放。

代碼示例:

always@(posedge clk, negedge rst_async_n)begin

if (!rst_async_n) begin

rst_s1 <= 1'b0;

rst_s2 <= 1'b0;

end

else begin

rst_s1 <= 1'b1;

rst_s2 <= rst_s1;

end

end

assign rst_sync_n = rst_s2;

rst_async_n=0時,rst_sync_n會被立即復位為0,輸出到后續電路用于異步復位;rst_async_n=1時,假設此時恰好在時鐘沿附近,會造成recovery或者removal的違例,但經過DFF1和DFF2的兩級同步,rst_sync_n釋放沿與時鐘沿同步,送入到后續電路不會再有recovery和removal違例出現。

可以看到,異步復位、同步釋放其最顯著特征是既保留了異步復位的功能,又避免了異步復位釋放時所面臨的recovery或者removal違例問題。

03小結

本文簡單介紹了在ASIC設計中常用的時鐘方案選擇和處理復位信號時的方案選擇。時鐘設計上,應盡可能避免通過內部邏輯產生時鐘,需要多個時鐘域時可以選擇用PLL產生分頻時鐘。需要考慮功耗的情況下可以選擇帶鎖存器的門控時鐘來降低功耗。在處理復位信號時,一般采用異步復位、同步釋放的方法,既保留異步復位的功能,又避免了復位信號釋放時的恢復時間和去除時間違例問題。

在后續的文章中,面對時鐘,還將介紹更為復雜棘手的多時鐘切換問題。

-

寄存器

+關注

關注

31文章

5355瀏覽量

120513 -

時鐘

+關注

關注

11文章

1735瀏覽量

131533 -

組合邏輯

+關注

關注

0文章

47瀏覽量

10047 -

異步復位

+關注

關注

0文章

47瀏覽量

13322 -

復位信號

+關注

關注

0文章

54瀏覽量

6329

發布評論請先 登錄

相關推薦

FPGA時鐘內部設計方案

外加電壓檢測復位電路設計方案

STM32電源管理、復位、時鐘

時鐘與復位信號設計方案

時鐘與復位信號設計方案

評論