01亞穩態理論

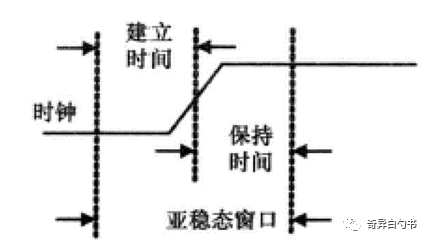

亞穩態(Metastability)是由于輸入信號違反了觸發器的建立時間(Setup time)或保持時間(Hold time)而產生的。建立時間是指在時鐘上升沿到來前的一段時間,數據信號就要提前準備好并穩定,保持時間是指時鐘上升沿到來后的一段時間,數據信號需要保持住。建立時間和保持時間是觸發器的固有屬性,由工藝決定。

如果數據信號在亞穩態窗口內發生變化,那么觸發器的輸出就會變成一段時間的“未知態”。這種狀態對于電路而言是有害的,且需要一段時間才能回到穩定狀態。

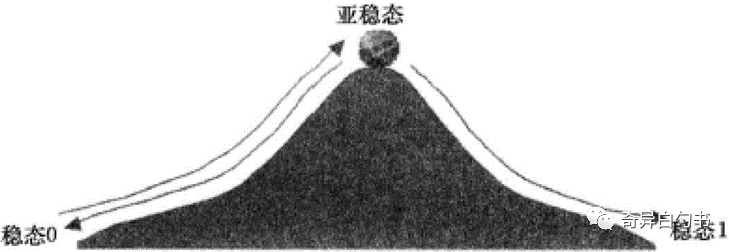

眾所周知,數字電路中的穩定狀態“0”或“1”一般是由TTL電平決定,所謂的亞穩態就是當觸發器電平工作在低電平與高電平之間的狀態,這個狀態一般會在1到2個時鐘周期恢復到“0”或“1”的穩定狀態,但是無法確定到底回到哪個穩態。

如同在一個小土坡上滾一個球,當產生亞穩態時,可能“推力”較大,球翻過了山坡,最后回到了穩態“1”;也可能“推力”不足,球又回滾到穩態“0”,這種情況下,輸出就可能產生毛刺。

02如何減少亞穩態

實際設計中,可能產生亞穩態的原因有:

- 輸入信號是異步信號;

- 時鐘偏移、擺動(上升/下降時間)高于容限值;

- 信號在兩個沒有固定相位關系的時鐘域進行跨時鐘域工作;

- 組合延遲使得觸發器的數據輸入在亞穩態窗口發生。

一個最簡單粗暴的解決辦法就是確保時鐘周期足夠長來避免亞穩態,這個時鐘周期要大于準穩態的解析時間,也要大于通往下一級觸發器路徑上的任何邏輯延遲,不過這樣做與性能要求相悖,實用性不大。因此實際工作中往往通過解決時序上的問題來降低亞穩態發生的概率:

- 跨時鐘域傳輸可以采用同步器、握手協議等;

- 采用響應更快的觸發器(縮短亞穩態窗口);

- 異步信號的采集可以采用異步FIFO對跨時鐘域數據進行緩沖設計;

- 降低工作頻率(就是增加時鐘周期,不是優選方案)

-

TTL

+關注

關注

7文章

541瀏覽量

71990 -

fifo

+關注

關注

3文章

402瀏覽量

44846 -

數字電路

+關注

關注

193文章

1641瀏覽量

81977 -

觸發器

+關注

關注

14文章

2039瀏覽量

62186 -

亞穩態

+關注

關注

0文章

47瀏覽量

13539

發布評論請先 登錄

評論