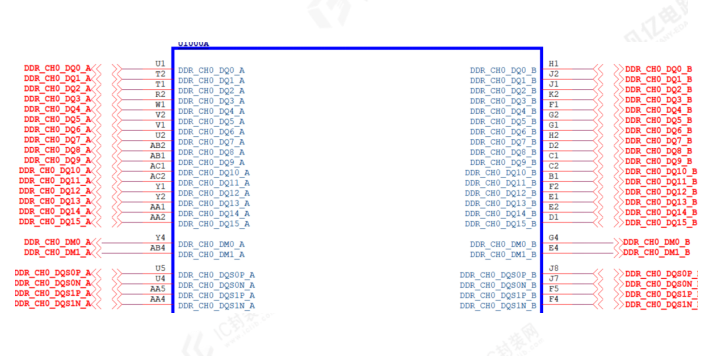

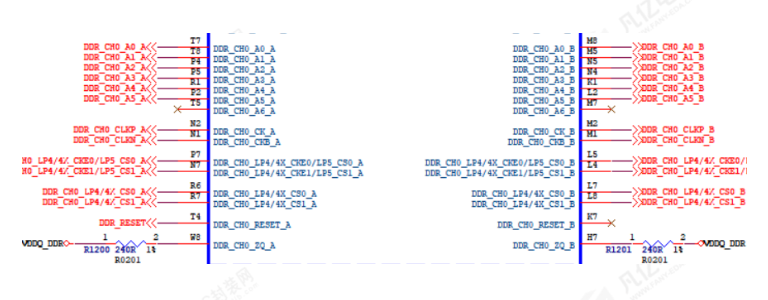

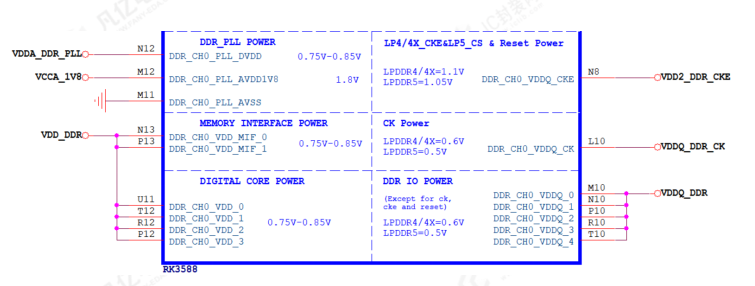

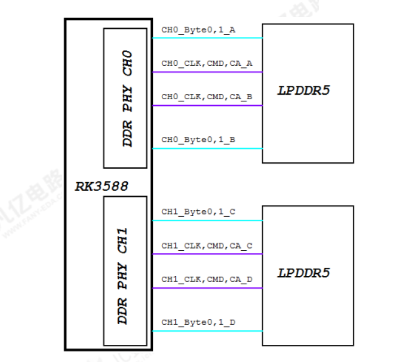

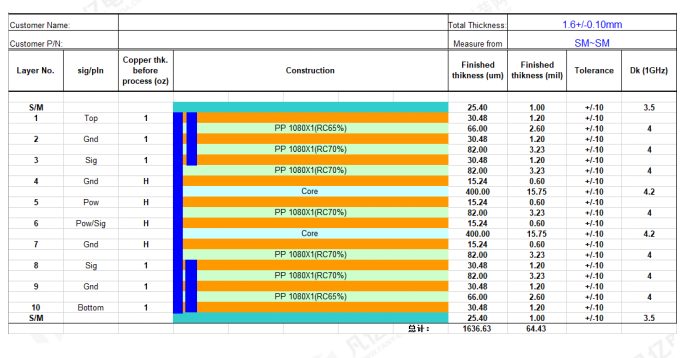

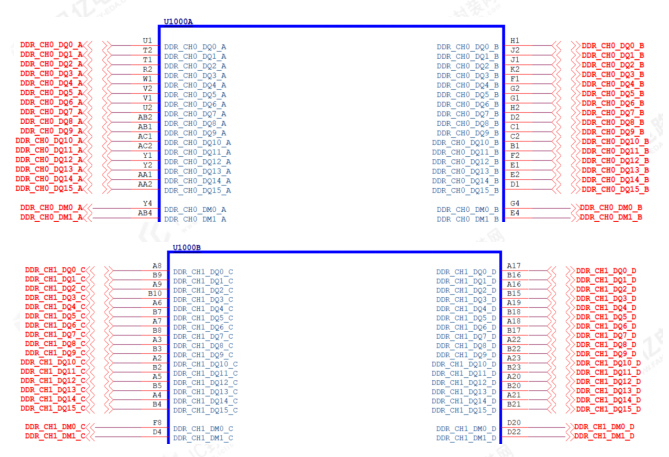

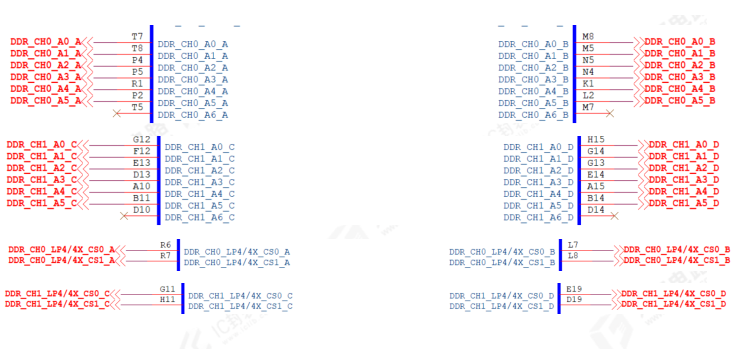

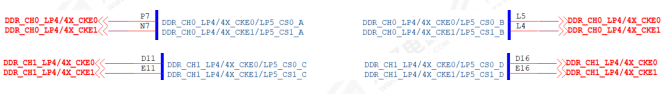

RK3588 DDR 控制器接口支持 JEDEC SDRAM 標準接口,原理電路16位數據信號如圖8-1所示,地址、控制信號如圖8-2所示,電源信號如圖8-3所示。電路控制器有如下特點:

1、兼容 LPDDR4/LPDDR4X/LPDDR5 標準;

2、支持 64bits 數據總線寬度,由 4 個 16bits 的 DDR 通道組成,每個通道容量最大尋址地址 8GB;4個通道容量可支持總容量達到 32GB;

3、兩個 16bits 組成一個 32bits 通道,2 個 32bits 通道(即圖紙中 CH0、CH1 通道)不能采用不同容量的顆粒配置,如 4GB+2GB;

4、支持 Power Down、Self Refresh 等模式;

5、具有動態 PVT 補償的可編程輸出和 ODT 阻抗調整。

圖 8-1 RK3588 DDR部分數據信號管腳

圖 8-2 RK3588 DDR部分地址、控制信號管腳

圖 8-3 RK3588 DDR部分電源管腳

DDR電路設計建議

1、RK3588 DDR PHY 和各 DRAM 顆粒原理圖保持與瑞芯微原廠設計一致性,包含DDR電源部分的去耦電容;

2、K3588 可支持 LPDDR4/LPDDR4X、LPDDR5,這些 DRAM 具有不同 I/O 信號,根據 DRAM 類型選擇對應的信號;

3、DQ,CA 順序全部不支持對調,如果PCB布線需要調整管腳,與瑞芯微原廠FAE溝通;

4、LPDDR4/4x/LPDDR5 的顆粒 ZQ 必須接 240ohm 1%到 VDDQ_DDR_S0 電源上;

5、LPDDR4/4x 的顆粒 ODT_CA 必須接 10Kohm 5%到 VDD2_DDR_S3 電源上;

6、內置 Retention 功能,DDR 進入自刷新期間,DDR 控制器端 DDR_CH_VDDQ_CKE 的電源腳需要保持供電,其它電源可關閉;DDR 顆粒的 VDDQ 電源在 tCKELCK 關閉 5ns 后也可以關閉,其它電源不能關;

7、LPDDR5 引入了 WCK 時鐘;LPDDR5 有兩個工作時鐘,一個是 CK_t 和 CK_c,用于控制命令、地址的操作;一個是 WCK_t 和 WCK_c,WCK 可以是 CK 頻率的 2 倍或 4 倍運行;當 Write 時,WCK 是時鐘也是 Write data strobe;當 Read 時,WCK 是 DQ 和 RDQS 的時鐘,RDQS 是 Read data strobe 信號;

8、RK3588 支持 DVFSC Mode(運行 LPDDR5 時),DVFSC 模式支持在 VDD2L(0.9V)和 VDD2H(1.05V)兩個電壓之間進行切換,即高頻運行時采用 VDD2H 電壓工作,低頻運行時采用 VDD2L 電壓工作。

DDR 拓撲結構與匹配方式設計

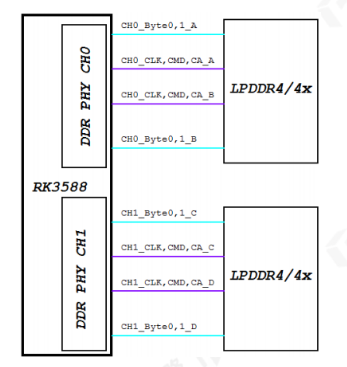

1、LPDDR4/4x 2 顆 32bit 時,DQ、CA 采用點對點拓撲結構,如圖8-4所示,匹配方式為LPDDR4 顆粒 DQ、CLK、CMD、CA 都支持 ODT,全部點對點連接即可;

2、LPDDR5 2 顆 32bit 時,DQ、CA 采用點對點拓撲結構,如圖8-5所示,匹配方式為LPDDR5 顆粒 DQ、CLK、CMD、CA 都支持 ODT,全部點對點連接即可。

圖 8-4 LPDDR4 點對點拓撲結構

圖 8-5 LPDDR5 點對點拓撲結構

DDR 電源設計和上電時序要求

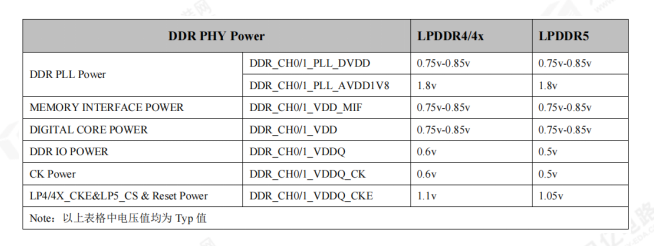

1、RK3588 DDR PHY 供電電源匯總如表8-1所示:

表8-1 RK3588 DDR PHY 供電電源

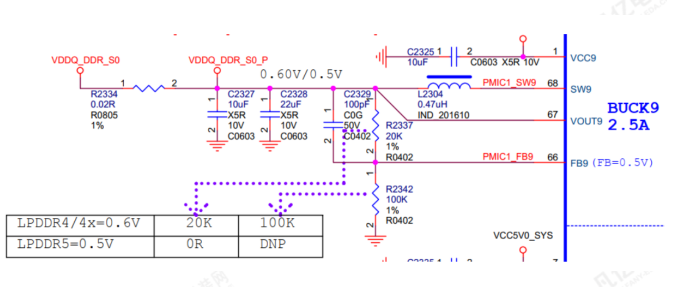

2、LPDDR4/4x/LPDDR5 顆粒供電電源匯總如表8-2所示:

表8-2 LPDDR4/4x/LPDDR5 供電電源

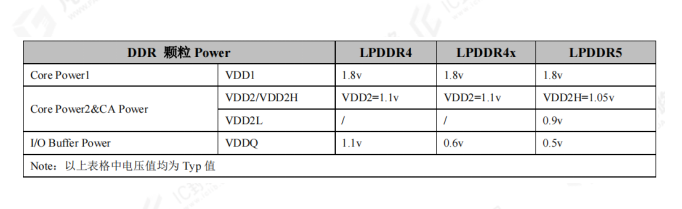

DDR 電源設計電路建議

1. 采用雙 PMIC 電源方案時供電電路

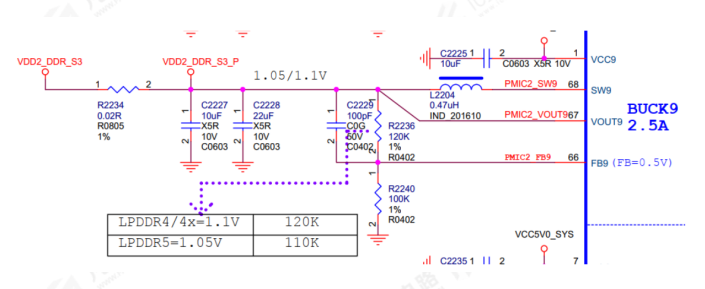

1.1 采用瑞芯微配套PMIC 型號為 RK806-2,務必注意,根據實際使用 DRAM 顆粒,同步修改 PMIC2 RK806-2 FB9(pin66)的分壓電阻阻值,使得 VDDQ_DDR_S0 輸出電壓與顆粒相匹配,如圖8-6所示;

圖 8-6 RK806-2 BUCK9 FB參數調整

1.2 采用瑞芯微配套PMIC 型號為RK806-2,務必注意,根據實際使用DRAM顆粒,同步修改PMIC2 RK806-2 FB9(pin66)的分壓電阻阻值,使得VDD2_DDR_S3輸出電壓與顆粒相匹配,如圖8-7所示;

圖 8-7 RK806-2 BUCK9 FB 參數調整

2. 采用單 PMIC 電源方案時供電電路

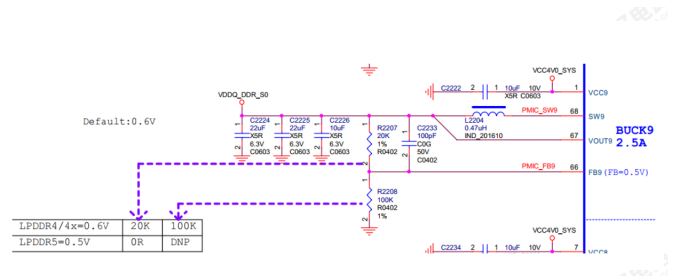

1、采用瑞芯微配套PMIC 型號為 RK806-1,務必注意,根據實際使用 DRAM 顆粒,同步修改 PMIC RK806-1 FB9(pin66)的分壓電阻阻值,使得 VDDQ_DDR_S0 輸出電壓與顆粒相匹配,如圖8-8所示;

圖 8-8 RK806-1 BUCK9 FB 參數調整

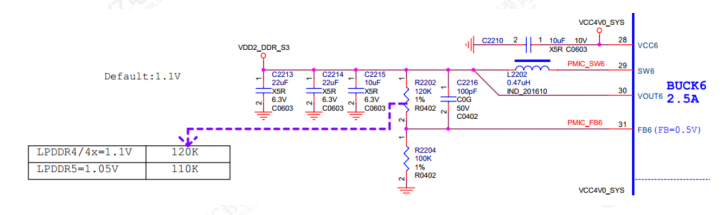

2、采用瑞芯微配套PMIC型號為RK806-1,務必注意,根據實際使用DRAM 顆粒,同步修改PMIC RK806-1 FB6(pin31)的分壓電阻阻值,使得VDD2_DDR_S3輸出電壓與顆粒相匹配,如圖8-9所示;

圖 8-9 RK806-1 BUCK6 FB 參數調整

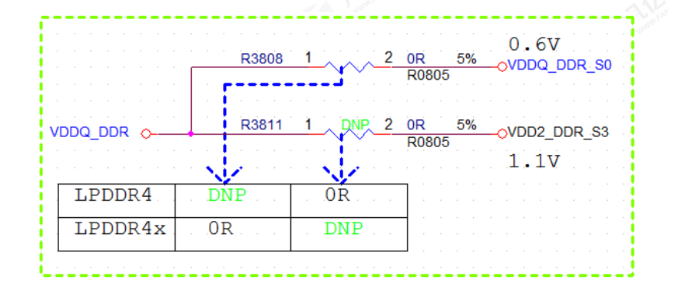

3、瑞芯微原廠RK3588電路圖紙參考模板里提供了LPDDR4 和 LPDDR4x 兼 容 設 計,需要注意的是:必須根據實際物料選擇相應的電路。貼 LPDDR4 顆粒時,只需要貼 R3811 電阻,R3808 不貼;貼 LPDDR4x 顆粒時,只需要貼 R3808 電阻,R3811 不貼,如圖8-10所示。

圖 8-10 LPDDR4/LPDDR4x 兼容設計電源選擇

DDR電路疊層與阻抗設計

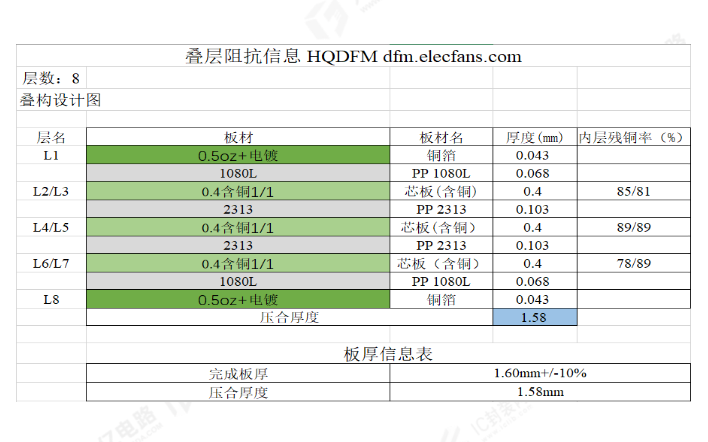

8層通孔板1.6mm厚度疊層與阻抗設計

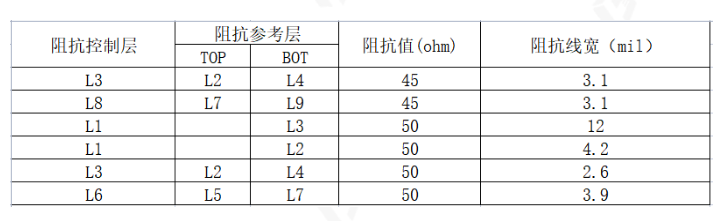

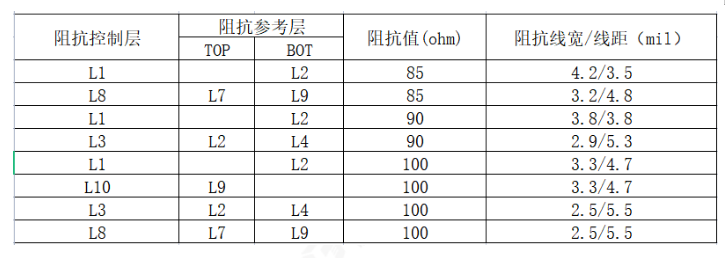

在8層通孔板疊層設計中,頂層信號 L1 的參考平面為 L2,底層信號 L8 的參考平面為 L7。建議層疊為TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基銅厚度建議全部采用 1oZ,厚度為1.6mm。詳細的疊層與阻抗設計過程見白皮書第2章。板厚推薦疊層如圖8-11所示,阻抗線寬線距如圖8-12所示。

圖 8-11 8層通孔1.6mm厚度推薦疊層

圖 8-12 8層通孔1.6mm厚度各阻抗線寬線距

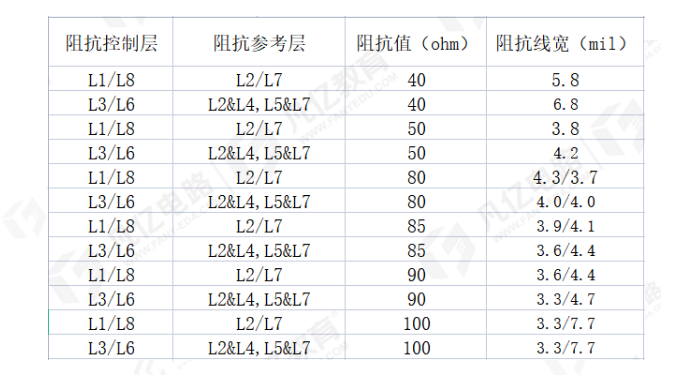

10層1階HDI板1.6mm厚度疊層與阻抗設計

在10層1階板疊層設計中,頂層信號L1的參考平面為L2,底層信號L10的參考平面為L9。建議層疊為TOP-Signal/Gnd-Gnd/Power-Signal-Gnd/Power-Gnd/Power-Gnd/Power-Signal-Gnd-Bottom,其中L1,L2,L9,L10,建議采用1oZ,其它內層采用HoZ。詳細的疊層與阻抗設計過程見白皮書第2章。板厚推薦疊層如圖8-13所示,阻抗線寬線距如圖8-14所示。

圖8-13 10層1階HDI板疊層設計

圖8-14 10層1階HDI板阻抗設計

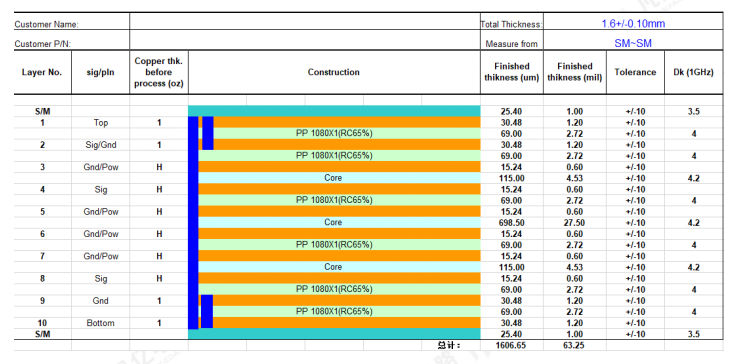

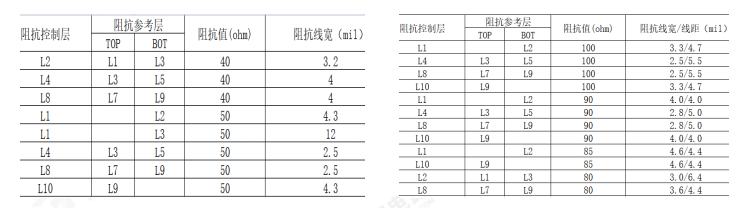

10層2階HDI板1.6mm厚度疊層與阻抗設計

在10層2階板疊層設計中,頂層信號L1的參考平面為L2,底層信號L10的參考平面為L9。建議層疊為TOP-Gnd-Signal-Gnd-Power-Signal/Pow -Gnd-Signal-Gnd-Bottom,其中L1,L2,L3,L8,L9,L10,建議采用1oZ,其它內層采用HoZ。細的疊層與阻抗設計過程見白皮書第2章。板厚推薦疊層如圖8-15所示,阻抗線寬線距如圖8-16與8-17所示。

圖8-15 10層2階HDI板疊層設計

圖8-16 10層2階HDI板單端阻抗設計圖

圖8-17 10層2階HDI板差分阻抗設計圖

DDR電路阻抗線與阻抗要求

1、所有通道數據DQ、DM單端信號阻抗40歐姆,如果疊層無法滿足40歐目標阻抗,至少保證阻抗滿足45ohm±10%,40歐目標阻抗信號余量會更大,45歐目標阻抗信號余量會更小,如圖8-18所示;

圖 8-18 CH0與CH1通道數據DQ、DM阻抗線

2、所有通道地址、控制單端信號阻抗40歐姆,如圖8-19所示;

圖 8-19 CH0與CH1通道地址、控制阻抗線

3、CKE單端信號阻抗50歐姆,如圖8-20所示;

圖 8-20 CH0與CH1通道CKE阻抗線

4、所有通道數據鎖存信號DQS與時鐘差分信號阻抗80歐姆,如果疊層無法滿足80歐目標阻抗,至少保證阻抗滿足90ohm ±10%,如圖8-21所示;

圖 8-21 CH0與CH1通道DQS與CLK差分阻抗線

DDR電路PCB布局布線要求

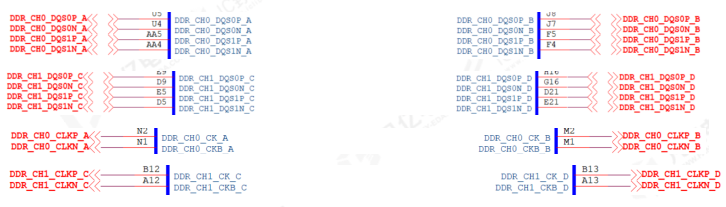

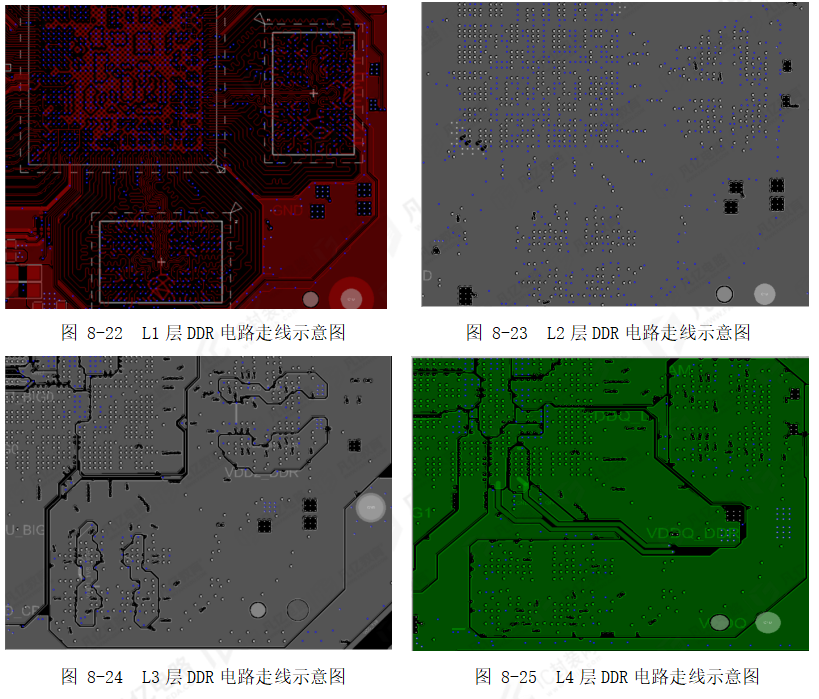

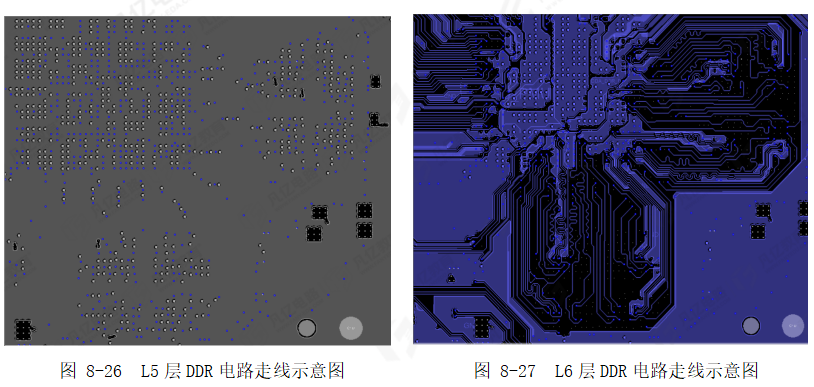

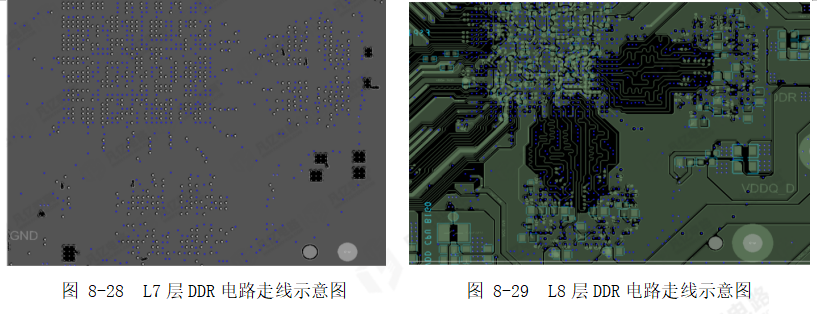

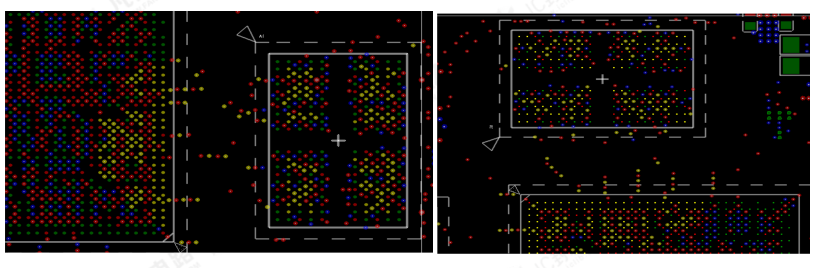

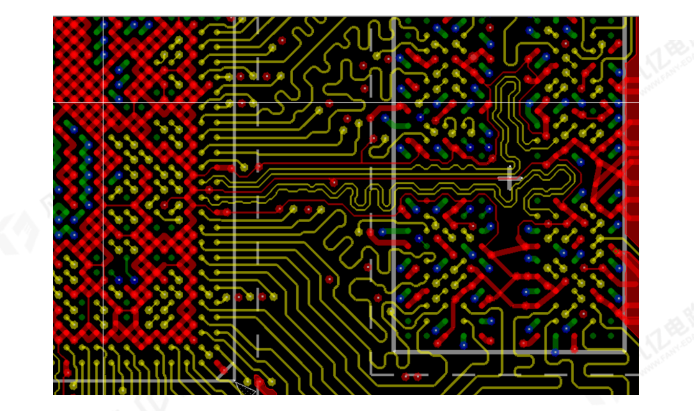

1、由于RK3588 DDR接口速率最高達4266Mbps,PCB 設計難度大,所以強烈建議使用瑞芯微原廠提供的 DDR 模板和對應的 DDR 固件。DDR 模板是經過嚴格的仿真和測試驗證后發布的。在單板PCB設計空間足夠的情況下,優先考慮留出DDR電路模塊所需要的布局布線空間,拷貝瑞芯微原廠提供的 DDR 模板,包含芯片與DDR顆粒相對位置、電源濾波電容位置、鋪銅間距等完全保持一致。如圖8-22至8-29所示。

2、如果自己設計 PCB,請參考以下PCB 設計建議,強烈建議進行仿真優化,然后與瑞芯微原廠FAE進行確認,確認沒問題以后在進行打樣調試。

-

CPU 管腳,對應的 GND 過孔數量,建議嚴格參考模板設計,不能刪減 GND 過孔。8 層通孔的 PCB模板,CPU 管腳 GND 過孔設計如圖8-30所示,黃色為DDR管腳信號,地管腳為紅色;

圖 8-30 RK3588地過孔示意圖

-

信號換層前后,參考層都為 GND 平面時,在信號過孔 25mil(過孔和過孔的中心間距)范圍內需要添加 GND 回流過孔(黃色為DDR信號,紅色為GND信號),改善信號回流路徑,GND 過孔需要把信號換層前后 GND 參考平面連接起來。一個信號過孔,至少要有一個 GND 回流過孔,盡可能增加 GND 回流過孔數量,可以進一步改善信號質量,如圖8-31所示;

圖 8-31 信號換層添加地過孔示意圖

-

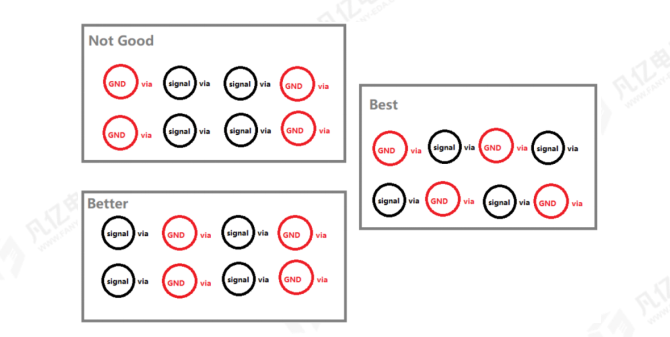

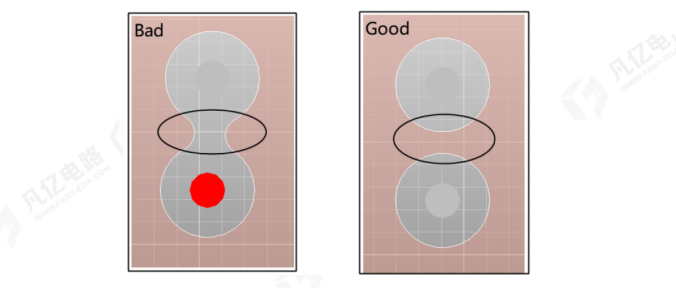

GND 過孔和信號過孔的位置會影響信號質量,建議 GND 過孔和信號過孔交叉放置如圖8-32所示,雖然同樣是 4 個 GND 回流過孔,4 個信號過孔在一起的情況要避免,這種情況下過孔的串擾最大;

圖 8-32 回流地過孔的位置示意圖

-

8 層板,建議 DDR 信號走第一層、第六層、第八層。DQ、DQS、地址和控制信號、CLK 信號都參考完整的 GND 平面。如果 GND 平面不完整,將會對信號質量造成很大的影響;

-

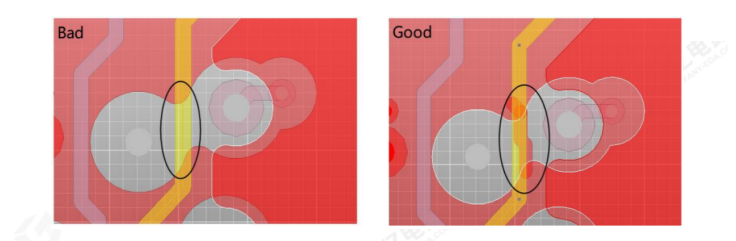

如圖8-33所示,當過孔導致信號參考層破裂時,可以考慮用 GND 走線優化下參考層,改善信號質量;

圖 8-33 地平面割裂補全示意圖

-

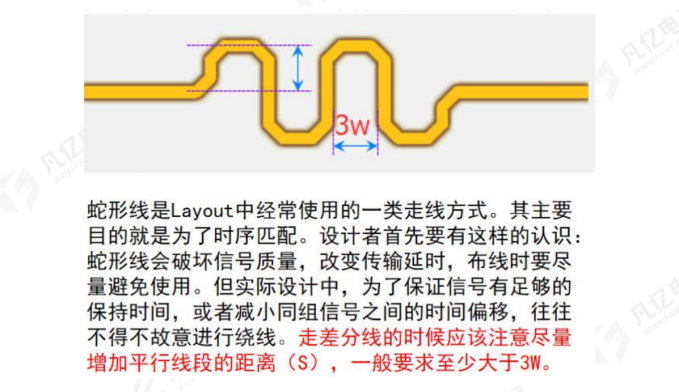

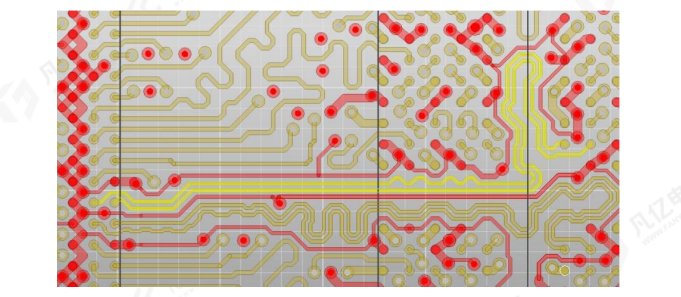

繞線自身的串擾會影響信號延時,走線繞等長時注意按圖8-34所示;

圖 8-34 蛇形走線示意圖

-

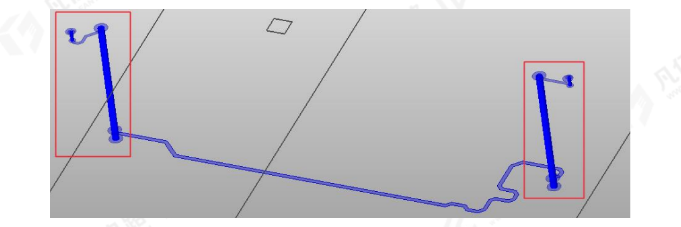

在做等長時,需要考慮過孔的延時,如圖8-35所示;

圖 8-35 過孔延遲示意圖

-

非功能焊盤會破壞銅皮,以及增大過孔的寄生電容,需要刪除過孔的非功能焊盤,做無盤設計;

-

走線距離過孔越近,參考平面越差,走線距離過孔鉆孔距離建議≧8mil,有空間的地方增大間距;

-

調整過孔位置,優化平面的裂縫,不要造成平面割裂,起到改善回流路徑的作用,如圖8-36所示;

圖 8-36 過孔優化示意圖

-

DQS、CLK、WCLK 信號需要做包地處理,包地線或銅皮建議每隔≦400mil,打一個 GND 過孔,如圖8-37所示;

圖 8-37 差分信號包地示意圖

-

對于 VDD_DDR 電源,DCDC 區域電源換層時,建議打≧6 個 0503 過孔;

-

對于 VDDQ_DDR 電源,DCDC 區域電源換層時,建議打≧6 個 0503 過孔;

-

對于 VDD2_DDR 電源,DCDC 區域電源換層時,建議打≧6 個 0503 過孔;

-

對于 VDD1_1V8_DDR 電源,電源平面換層時,建議至少打≧2 個 0402 過孔;

-

每個電容焊盤建議至少一個過孔,對于 0603 或者 0805 封裝的電容建議一個焊盤對應兩個過孔,過孔的位置要靠近管腳放置,減小回路電感。

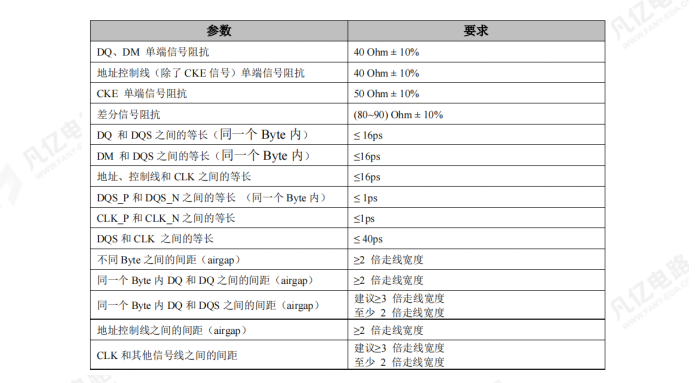

DDR電路PCB設計時序要求

由于 8 層板,表層和內層都有走線。無論是單端信號還是差分信號,表層走線和內層走線,速率有差異。表層走線,單端信號和差分信號速率有差異。內層走線,單端信號和差分信號差異較小。過孔速率和走線速率有差異,為了減小速率差異對信號余量的影響,設計規則需要按等延時來要求。PCB 設計時,需要按實際制板的疊層設置疊層參數,同時把封裝延時,和過孔延時考慮進來,具體的時序要求如表8-3所示。

表8-3 LPDDR4阻抗、時序表

聲明:-

pcb

+關注

關注

4319文章

23080瀏覽量

397518

原文標題:DDR模塊電路的PCB設計建議

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

HDMI模塊的PCB設計

專業PCB設計,高速PCB設計,PCB設計外包, PCB Layout,PCB Design,PCB畫板公司,PCB設計公司,迅安通科技公司介紹

PCB設計中的爬電距離:確保電路板安全可靠

如何理解PCB設計的爬電距離?

PCB設計與PCB制板的緊密關系

電路仿真和PCB設計軟件

PCB設計的EMC有哪些注意事項

PCB設計中的常見問題有哪些?

儲能PCB設計與制造思考 探討儲能PCB設計與制造中的關鍵要素

DDR模塊電路的PCB設計建議

DDR模塊電路的PCB設計建議

評論