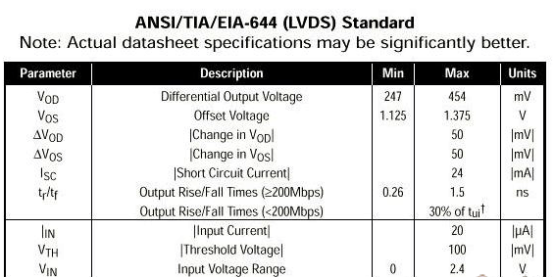

LVDS電平是根據(jù)ANSI/EIA/TIA-644定義的一種電平標(biāo)準(zhǔn),其標(biāo)準(zhǔn)定義的相關(guān)參數(shù)如下:

圖1 LVDS電平標(biāo)準(zhǔn)

標(biāo)準(zhǔn)參數(shù)的制定一方面取決于器件的制造工藝水平,另一方面取決于該標(biāo)準(zhǔn)面向的應(yīng)用場(chǎng)景的性能要求。這意味著在不同的參數(shù)里,思考參數(shù)的取值的方法可能大相徑庭。

- LVDS電平基本原理

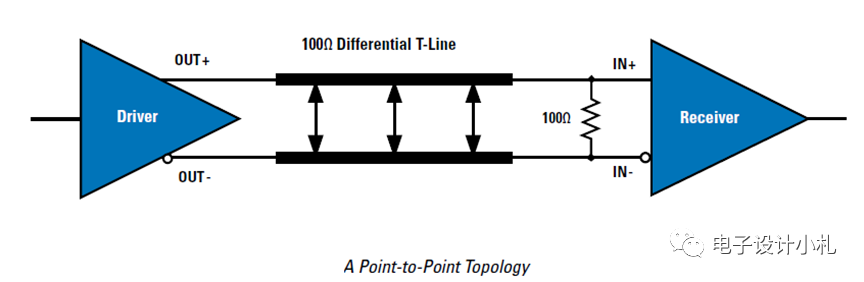

圖2 LVDS發(fā)送和接收電路的結(jié)構(gòu)

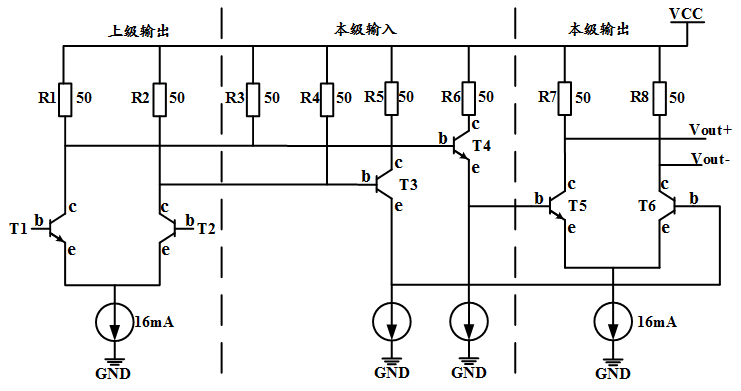

LVDS的發(fā)送電路一般為圖2所示的全橋結(jié)構(gòu),當(dāng)T1和T4導(dǎo)通時(shí),發(fā)送側(cè)輸出的電流通過(guò)末端100歐姆的匹配電阻形成回路,此時(shí)電壓上正下負(fù);當(dāng)T2和T3導(dǎo)通時(shí),末端電阻的電流流向逆轉(zhuǎn),此時(shí)電壓下負(fù)上正,LVDS即通過(guò)此來(lái)傳輸高低電平。另外,發(fā)送電路內(nèi)部一般都會(huì)有直流偏置來(lái)提供共模電壓。

2. 共模電壓

LVDS電平標(biāo)準(zhǔn)對(duì)共模電壓做了具體的要求,并且根據(jù)實(shí)際的芯片手冊(cè)來(lái)看,輸入輸出對(duì)共模電壓的要求并不一致,那么,共模電壓有什么作用,為什么共模電壓的要求會(huì)不一致呢。

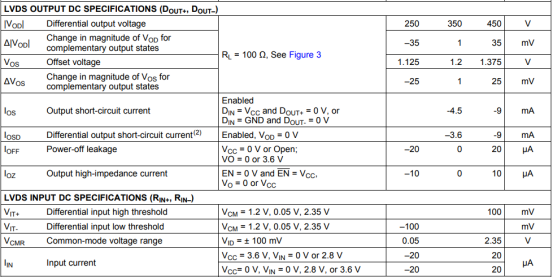

圖3 SN65LVDS049 的輸入輸出參數(shù)

圖3截取了SN65LVDS049 的相關(guān)參數(shù),可以看到其輸出共模電壓是1.125V ~ 1.375V,輸入共模電壓為0.05~2.35V,兩者相差較大,原因在于輸出參數(shù)為性能要求決定,通過(guò)內(nèi)部偏置電壓,可以滿足參數(shù)的要求,而輸入?yún)?shù)則更多的由器件本身特性決定,它表示該器件可正常工作的一個(gè)范圍。至于為什么是這么一個(gè)范圍,則需要進(jìn)一步分析。

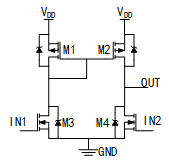

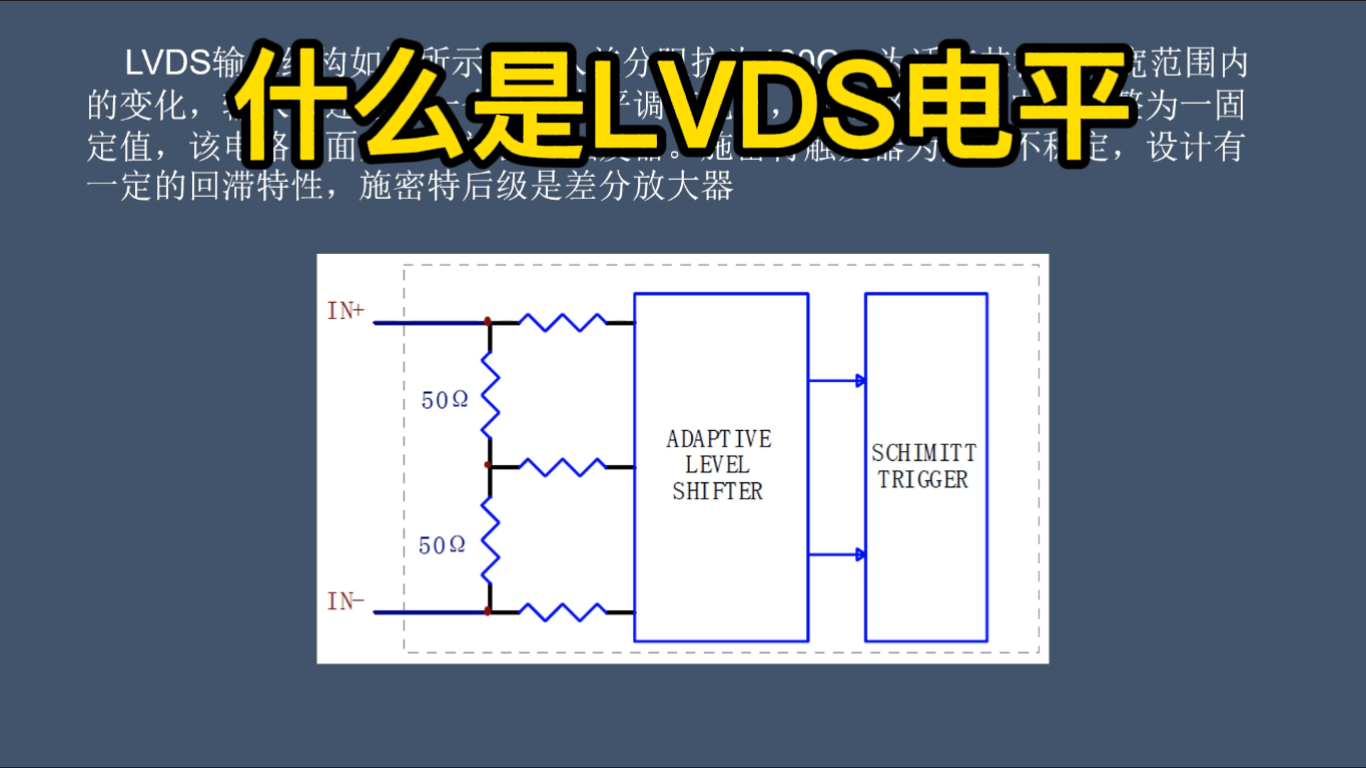

LVDS的接收器是一個(gè)運(yùn)放,運(yùn)放的輸入級(jí)如圖4所示。

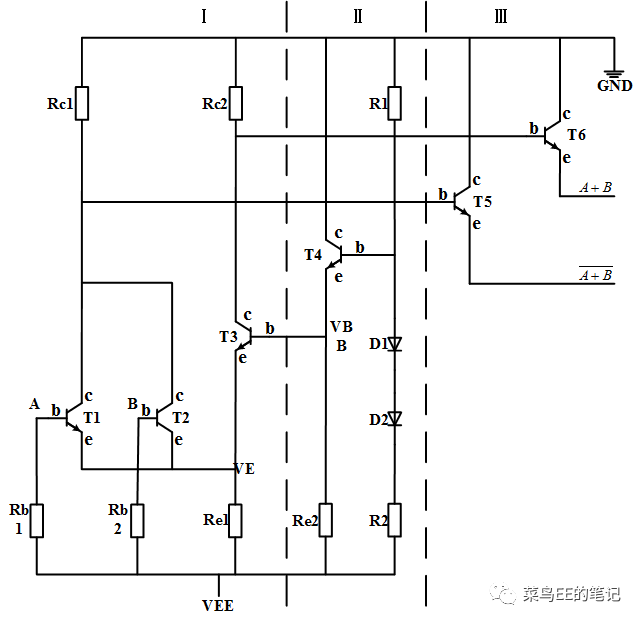

圖4 運(yùn)放輸入級(jí)的結(jié)構(gòu)

M1和M2組成電流鏡,為M3和M4組成的差分輸入對(duì)提供有源負(fù)載。使用電流鏡的原因是因?yàn)?a target="_blank">電流源的阻抗非常大,根據(jù)A v =gmR D ,理論上可以提供很大電壓增益,并且電流源也可提供穩(wěn)定的偏置電流,減小溫度的影響。MOS管的跨導(dǎo)gm在飽和區(qū)較大且較為穩(wěn)定,所以在放大電路中,MOS管一般工作在飽和區(qū)。為了滿足這個(gè)要求,我們需要對(duì)MOS管的工作點(diǎn)進(jìn)行設(shè)置,這也是共模電壓的任務(wù)。

為了簡(jiǎn)化分析,假設(shè)MOS的開(kāi)啟電壓為0,如若要使MOS管工作在飽和區(qū),要滿足V gd

Vcm -VDD -Von(sat)

即:

Vcm

顯然,Vcm應(yīng)大于Vth ,故有:

Vth

可見(jiàn),輸入共模電壓的取值是比較寬泛的,所以,當(dāng)輸入電壓的值較大,輸入共模電壓的值自然會(huì)升高。而輸出共模電壓的值是內(nèi)部偏置電壓決定的,兩者存在差異是正常的。

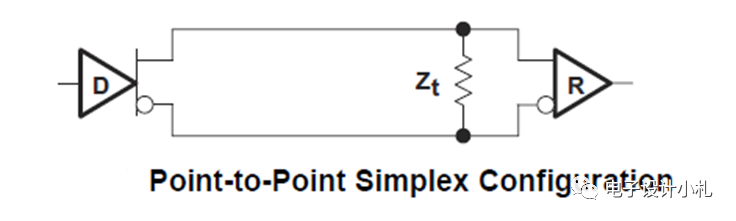

- 終端電阻、偏置電流源以及輸入門限電壓

終端匹配電阻取值100ohm主要是為了阻抗匹配。從標(biāo)準(zhǔn)上看,偏置電流源的大小也是可以調(diào)節(jié)的,擺幅低時(shí)傳輸距離短,但是可以達(dá)到更高的頻率,反之則傳輸距離可以變長(zhǎng)但頻率上限會(huì)降低。門限電壓則可由器件工藝控制,是一個(gè)硬性指標(biāo)。

-

運(yùn)放

+關(guān)注

關(guān)注

47文章

1166瀏覽量

53138 -

lvds

+關(guān)注

關(guān)注

2文章

1043瀏覽量

65848 -

接收電路

+關(guān)注

關(guān)注

13文章

86瀏覽量

25156 -

電平標(biāo)準(zhǔn)

+關(guān)注

關(guān)注

0文章

4瀏覽量

6603 -

LVDS電平

+關(guān)注

關(guān)注

0文章

3瀏覽量

1650

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

淺談LVDS、CML、LVPECL三種差分邏輯電平之間的互連

電平標(biāo)準(zhǔn)M-LVDS接口學(xué)習(xí)筆記

電平標(biāo)準(zhǔn)LVDS接口學(xué)習(xí)筆記

求助LVDS電平轉(zhuǎn)HCSL的轉(zhuǎn)換電路

LVDS信號(hào)電平特性

MAX9376 LVDS/任意邏輯至LVPECL/LVDS、

ECL電平、LVDS電平、TTL電平_簡(jiǎn)單的比較

LVDS和CML與LVPECL的同種差分邏輯電平之間的互連教程

LVDS電平以及LVDS25電平能否約束到這個(gè)BANK上呢?

CML電平學(xué)習(xí)筆記

ECL/PECL/LVPECL電平學(xué)習(xí)筆記

LVDS電平學(xué)習(xí)筆記

LVDS電平學(xué)習(xí)筆記

評(píng)論