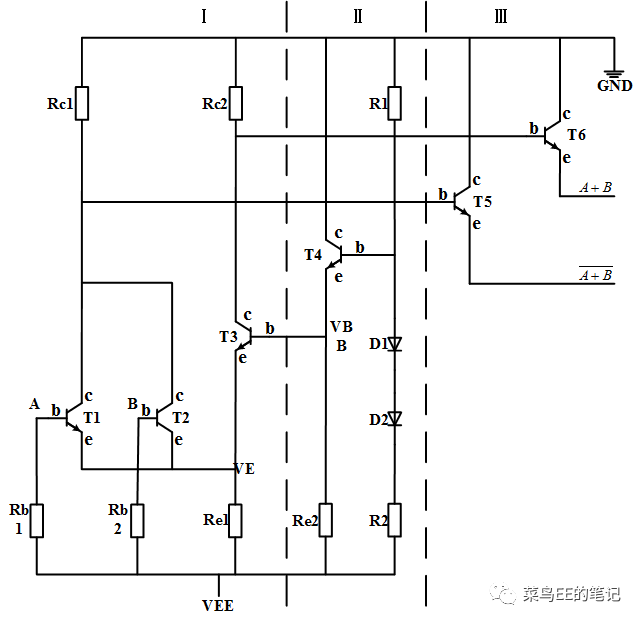

1.基本原理

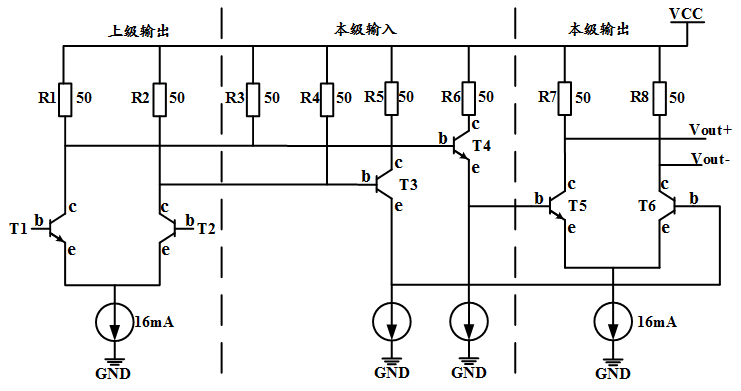

CML電路如圖1 所示,輸入部分為一射隨器,假設T3管為N端,T4管為P端,當P大于N時即輸入為高電平,反之為低電平。由于輸入部分為射隨器,輸出端接收到高低電平的相位與輸入端一致,當接收為高電平時,T5導通,其射極電位被鉗位,導致T6截止,16mA電流均從T5流過,此時輸出為低電平。輸入為低時情況類似。可見,CML輸入輸出存在倒相的關系。

圖1

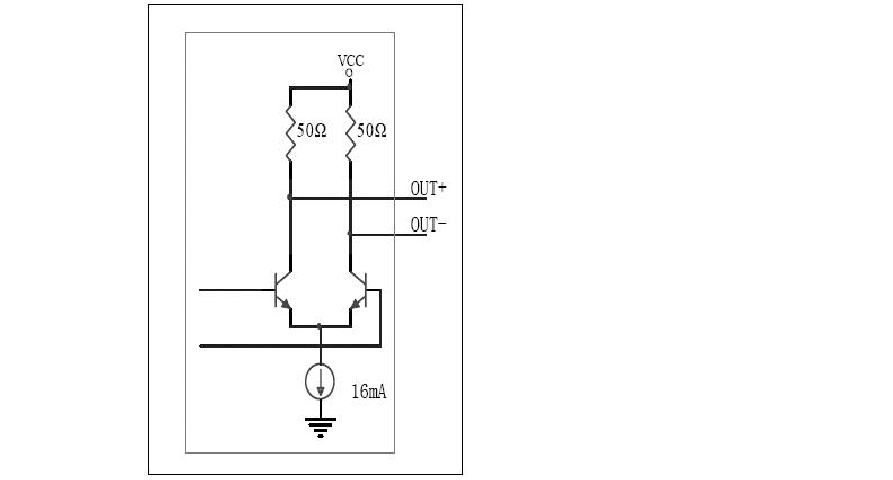

2.為什么CML電路差分輸出需要一個16mA的電流源?

差分放大電路使用一個電流源進行偏置,可以提高其共模抑制比,并且提供一個穩定的靜態工作點(差分放大電路的具體分析另起一文)。電流源的大小影響的是輸出電平的擺幅,而擺幅會影響傳輸的速率、距離以及電路的功耗,16mA應為綜合考慮以上因素得到的一個標準(具體未考證)。

- 相關計算

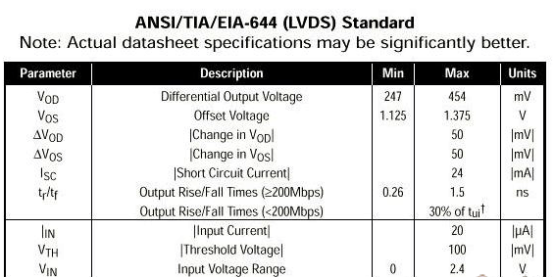

一般資料中對CML電平輸入輸出相關參數的描述如下:假定CML 輸出負載為一50Ω上拉電阻,直流耦合時,單端CML 輸出信號的擺幅為Vcc ~ Vcc-0.4V。在這種情況下,差分輸出信號擺幅為800mV,共模電壓為Vcc-0.2V。若CML輸出采用交流耦合至50Ω負載,CML 輸出共模電壓變為Vcc-0.4V,單端CML 輸出信號的擺幅為Vcc-0.2~Vcc-0.6V,差分信號擺幅仍為800mV。那么,以上數據是怎么來的呢?

直流耦合:

直流耦合時,差分對的電流回路如圖2所示。輸出差分對的直流、交流回路是一致的。首先對其進行靜態分析,由于T1、T2參數對稱,故16mA電流平均流過T1、T2,每個管流過8mA的電流,分到R1~R4四個電阻上,每個電阻流過的電流為4mA,所以直流耦合時的共模電壓為:

當有差模電壓輸入時,T1、T2只會導通一個(以T1導通為例),16mA電流由R1、R3一起提供,每個電阻提供8mA電流,因此單端擺幅為:

圖2

由共模電壓定義:

設單端輸出電壓高電平為x,低電平為x-0.4,差分輸出時一端為高另一端為低,則有:

解得,x為VCC,單端電壓變化范圍為VCC~VCC-0.4。

那么,為什么差分擺幅為800mV呢?

當T1導通、T2截止時,VOUT-為VCC,VOUT+為VCC-0.4V,兩者壓差為400mv;當T2導通、T1截止時,VOUT+為VCC,VOUT-為VCC-0.4V,兩者壓差也為400mv,似乎差分擺幅也應該為400mv,實則不然。分析如下:

當T1導通、T2截止時,VOUT-為VCC,VOUT+為VCC-0.4V,此時為輸出差分電壓的低電平,其值為:

當T2導通、T1截止時,VOUT+為VCC,VOUT-為VCC-0.4V,此時為輸出差分電壓的高電平,其值為:

故差分擺幅為:

交流耦合:

交流耦合時,T1、T2的電流回路如圖3所示。首先進行靜態分析,由于電容的隔直作用,R3、R4不能向T1、T2提供直流分量,所以16mA電流由R1、R2提供,流過每個電阻的電流為8mA,可得共模電壓為:

圖3

當有差模電壓輸入時,T1、T2只會導通一個(以T1導通為例),由于電容通交流,16mA電流由R1、R3一起提供,每個電阻提供8mA電流,因此單端擺幅為:

單端電壓的輸出范圍為VCC-0.2~VCC-0.6V,差分擺幅為800mV交流耦合時(以T1導通為例),16mA電流均流過T1一個管,但是輸出電壓最大為VCC-0.2,表示即使在T2截止,R2上也有電流流過,且流向只能時通過電容、R4、形成回路,這個電流應為應為電容放電過程產生的電流。

根據CML的電路分析,其輸入輸出電平為固定的,因此電平門限無需討論。

-

電平

+關注

關注

5文章

361瀏覽量

40103 -

差分放大電路

+關注

關注

18文章

161瀏覽量

50154 -

CML

+關注

關注

0文章

32瀏覽量

19545 -

差模電壓

+關注

關注

0文章

24瀏覽量

8539 -

射隨器

+關注

關注

0文章

8瀏覽量

8981

發布評論請先 登錄

相關推薦

LVDS、CML、LVPECL不同邏輯電平之間的互連(二)

淺談LVDS、CML、LVPECL三種差分邏輯電平之間的互連

hdmi是什么電平?hdmi信號里有幾對差分還有幾個單端的,差分的信號是不是cml電平?

比較器ADCMP606的CML輸出只想用到CML的正極作為輸出,負極接地可以嗎?

差分邏輯電平,LVDS、xECL、CML、HCSL/LPHCSL、TMDS等

ADCMP606是CML差分電平輸出,用到CML的正極作為輸出,負極接地可以嗎?

SN65CML100 1.5Gbps LVDS/LVPECL/CML 至 CML 轉換器/中繼器

LVDS和CML與LVPECL的同種差分邏輯電平之間的互連教程

詳解信號邏輯電平標準:CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML資料下載

CML電平學習筆記

CML電平學習筆記

評論