開關電源EMI(電磁干擾)不通過可能會帶來以下幾個壞處:

1. 電子設備受到干擾:開關電源產生的高頻噪音和諧波可能會對周圍的電子設備產生干擾。這些干擾信號可能導致其他設備的故障、降低性能或產生電磁兼容性問題。

2. 增加電磁輻射:開關電源在正常工作時會產生高頻輻射,如果沒有通過EMI測試,可能會超出國家和地區的電磁輻射標準限制。這種輻射可能會對人體健康產生潛在風險,特別是長期接觸高強度輻射可能導致身體不適或健康問題。

3. 影響通信和無線設備:開關電源未經EMI測試可能會干擾通信信號和無線設備。這些干擾信號可能對無線電頻段的正常通信產生負面影響,導致通信質量下降、數據傳輸錯誤或通信中斷。

4. 不符合法規要求:一些國家和地區有嚴格的EMI標準和法規,要求電子設備必須通過EMI測試以確保其不會對其他設備或人體健康造成干擾。開關電源未經過EMI測試無法符合這些法規要求,可能會導致產品無法上市銷售或面臨法律責任。

EMI是評估電力電子開關電源性能上的一種關鍵參數,它可以通過多種方式加以降低,添加一個EMI過濾器似乎是最明顯的選擇,但可能還有更好的方法。今天EMC小哥帶您了解更多降低EMI方法

l傳導和輻射電磁干擾的降低方法。

l調整開關電壓調節器的頻率,以降低EMI.

l應用EMI過濾器

現代電子電力系統架構正變得越來越密集,并存在大量的互通互聯關系,降低此類系統中的EMI變得越來越具有挑戰性。

EMI的主要問題來源之一是開關電源(SMPS)。SMPS可以放在系統設計或印刷電路板 (PCB) 的外部,也可以是 PCB 上設計的一部分。無論哪種方式,都必須降低EMI干擾,以便通過標準測試以及不會造成周圍的電路錯誤操作。本文上海雷卯EMC小哥將為電路設計人員提供一些在設計中控制EMI的最佳方法。

THESMPS

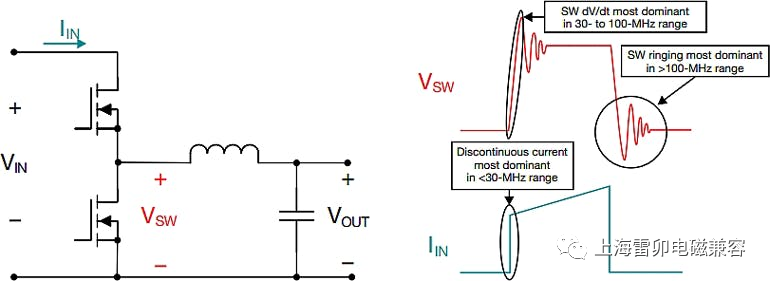

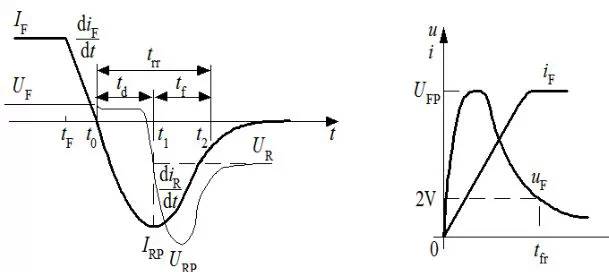

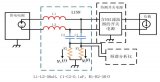

由于SMPS的效率比線性穩壓器效率顯著提高,已成為許多系統設計中的關鍵組件。功率硅MOSFET或GaN功率器件的開關導致不連續電流,是影響可靠系統運行的主要因素(圖1)。下面接著將概述一些降低各種形式 EMI 的最佳方法。

1. 本原理圖顯示了SMPS中的EMI源。

傳導EMI降低方法

傳導噪聲比輻射噪聲更容易分析;設計人員可以采用標準的電路分析方法。但是,EMI分析中的許多組件都是寄生的,不會出現在原理圖上。

當電源開關設備打開和關閉時,它們會產生較大的不連續電流。這些電流將出現在降壓轉換器的輸入端、升壓轉換器的輸出端以及反激式和降壓-升壓型轉換器設計的輸入和輸出端。

不連續電流會產生電壓紋波,這些紋波可能通過導體相互接觸傳導到系統架構的其他部分。轉換器輸入端的此類電流應通過輸入濾波器進行濾波,以減輕電壓干擾。功率轉換器的輸出也可能需要濾波器來幫助通過EMI標準。

共模噪聲通常更難分析,因為它通常是由寄生電容的充電/放電引起的,寄生電容在散熱器或變壓器繞組間電容最高。

輻射EMI降低方法

輻射噪聲可以通過兩種方式進行評估:

l用幾米外的天線測量的電磁噪聲。

l用靠近磁性元件的“嗅探器探頭”測量的磁噪聲。

電磁場的起因通常是電路中包含高頻諧波的電流,這些諧波在回路中流動。減小環路面積、di/dt或電流峰值幅度將有助于降低輻射噪聲。

開關調壓器中的抖動

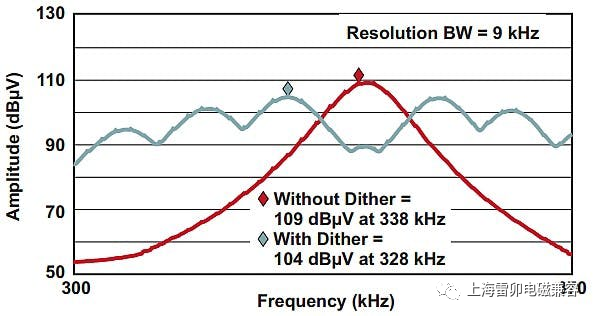

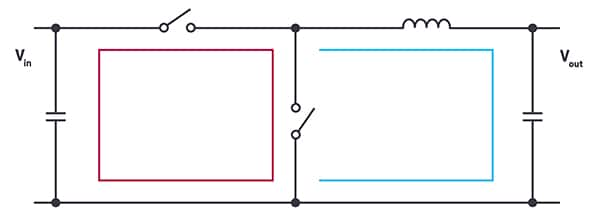

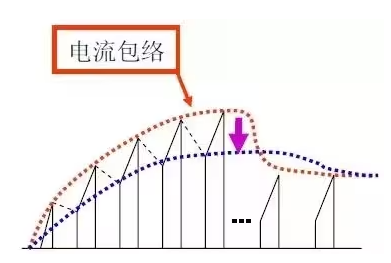

通過使用擴頻調頻(SSFM)技術,對開關調壓器開關頻率進行抖動,將降低EMI,并幫助設計人員當在濾波和優化布局無法滿足EMI標準限制時通過一致性測試。抖動略微調制開關穩壓器中的基波開關頻率。下面是它的工作原理。

開關電源的電磁輻射通過方波脈沖分布在許多頻率上,其中最大的能量在基頻處。稍微改變基頻(使用3%左右的典型調制)將調制峰值開關噪聲能量,該能量將在多個基頻之間共享。總電磁能量將保持不變,但窄帶能量已降低,因此EMI有效降低。

在圖1所示的示例中,5 dB峰值降噪可以在獲得標準批準的情況下快速上市,還是將噪聲峰值降低到標準限值以下(圖2)。

2. 此圖顯示了在 330 kHz 附近有和沒有抖動的準峰值測量值,顯示抖動導致 5 dB 降低。

使用封裝和引腳排列來降低 EMI

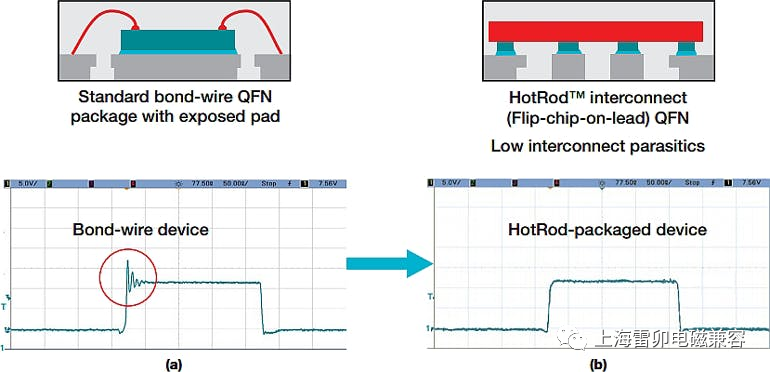

許多設計人員可能沒有考慮到,選擇有助于降低EMI的IC封裝類型的好處。一個很好的例子是在SMPS中封裝功率MOSFET。這些類型的電源轉換器使用快速開關電壓轉換速率 (dv/dt) 以及高電流速率 (di/dt),這將增加系統中的 EMI。

設計人員可以添加EMI濾波器作為解決方案。但是,在這樣做并增加設計尺寸(從而降低功率密度)之前,請先了解也有助于降低EMI的封裝技術。以下是如何利用功率MOSFET封裝設計改善EMI的一些示例。

排列電源引腳和GND引腳相鄰,這樣可以平行放置濾波電容,盡可能的減小環路,改進高頻EMI。此外,兩個相等和并聯電感的等效寄生環路電感減半。因此設計時的優化布置引腳位置可以降低高頻EMI.

QFN封裝中的鍵合線有時可以通過使用銅柱和引線框架與芯片之間的倒裝芯片互連來消除(圖3)。

3. 這種典型的 QFN 封裝使用鍵合線將芯片連接到裸露焊盤,電源開關在該焊盤中表現出明顯的振鈴 (a)。改進的封裝采用銅柱和從芯片到引線框架的倒裝芯片互連,從而消除了電源開關中的振鈴 (b)。

循環輸入電流將產生相反的磁場,導致H場抵消并減少輻射發射。因此,通過創建高di/dt輸入環路的對稱布局,產生的(相反方向的)磁場可以相互抵消。

降低封裝EMI的另一種方法是在另一個PCB層(如頂層電源電路正下方的第2層)的兩個電感環路下方放置一個連續接地層,用于返回電流。

電磁干擾濾波器

EMI濾波器可以是分立式的,也可以是模塊化的。電源設計人員將不得不在時間、尺寸和成本方面選擇最有利于其設計需求的電源。

高功率密度電源架構中的EMI濾波器

在高功率密度電源中,最大限度地減小EMI濾波器的尺寸至關重要。沒有磁性元件的濾波器設計更緊湊,從而達到良好的功率密度。

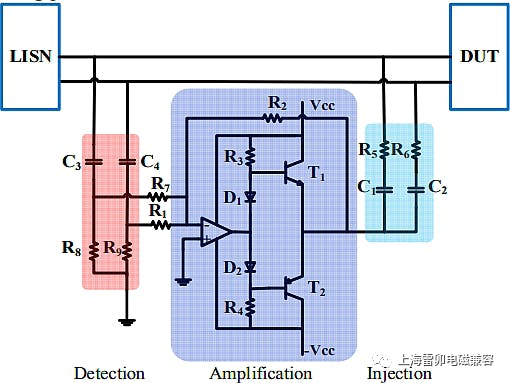

例如,圖4中的濾波器設計使用電壓檢測和無磁性元件的電流注入拓撲。為了增強濾波器的輸出電流和功率以及改善插入損耗(IL),在放大器輸出后面使用推挽式功率放大器電路,以使輸出電流足夠大。這種濾波器設計足夠穩定,可以取代無源EMI濾波器。

4. 這種高性能濾波器設計,沒有磁性元件,可以支持60 A量級的高輸出電流。

屏蔽EMI濾波器是控制傳導EMI的最后努力

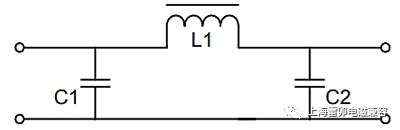

差模(DM)EMI濾波器(圖5)可能會在電源系統中產生傳導EMI干擾。

圖為π型EMI濾波器

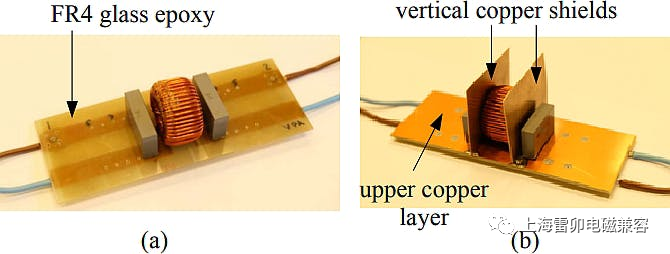

5.在DM濾波器下方放置銅屏蔽可能會有所幫助(圖6a)。當所有其他方法都失敗時,在PCB的頂部和底部添加銅層,并在濾波器的兩側添加兩個垂直銅屏蔽(圖6b)。

6. DM EMI濾波器有兩種不同的配置:在(a)中,濾波器位于單銅層PCB的頂部,每個濾波器元件之間的距離為3.5毫米。在(b)中,濾波器位于雙銅層(頂部和底部)PCB和兩個垂直銅屏蔽層上,每個濾波器組件之間有3.5 mm。

總結

設計人員需要了解以及工具,以最大程度地減少電路板設計之間的傳導和輻射EMI干擾。本文上海雷卯EMC小哥重點介紹SMPS,它比線性電源大大提高了效率,但為了最大限度地降低EMI干擾,也可能需要非常耗時。本文介紹的技術和工具提供了改進SMPS設計的方法,以幫助設備通過EMI標準測試,同時最大限度地縮短設計時間。

-

電源

+關注

關注

184文章

17704瀏覽量

249964 -

emi

+關注

關注

53文章

3587瀏覽量

127607 -

信號

+關注

關注

11文章

2789瀏覽量

76730 -

設備

+關注

關注

2文章

4502瀏覽量

70600 -

電磁干擾

+關注

關注

36文章

2312瀏覽量

105392

發布評論請先 登錄

相關推薦

開關電源的效率優化方法 如何定制開關電源解決方案

開關電源的EMI/EMC測試標準

開關電源的尖峰干擾和抑制方法

怎樣降低開關電源的輸出電壓

開關電源故障檢修方法

開關電源紋波的測試方法是什么

開關電源輸出波形的分析方法

開關電源的種類及區分方法

開關電源沖擊電流測試方法有哪些

開關電源電磁兼容設計流程與方法

降低開關電源的EMI的方法

降低開關電源的EMI的方法

評論