針對I/O需求數目更多的低功耗應用,Actel可以提供IGLOO PLUS系列,規模分別是3萬、6萬和12.5萬門。和相同封裝的IGLOO器件相比,可以提供最多多出64%的I/O。其所有的器件都支持4個I/O Bank。在多電壓應用環境中比較有利,并且支持熱插拔和施密特觸發器。Actel在IGLOO系列產品的開發過程中,對靜態功耗的主要物理來源——漏電流方面做了改進。同時在生產過程中對產率、速度以及可靠性做了嚴密的監控。

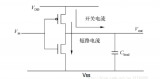

采用IGLOO器件的低功耗優勢從哪些方面獲得呢?首先來自IGLOO器件本身對漏電流源頭的控制,以及器件所提供的各種節省功耗的特性的實現和各種最少功耗數據存儲技術的實現。除此之外,設計中采用一些低功耗技巧,也可以降低靜態功耗。

IGLOO具有功耗友好的器件架構,能提供靜態、睡眠、Flash*Freeze功耗模式,允許采用動態電壓和頻率調節技術來降低系統整體實際功耗。提供可選擇的1.2V和1.5V的I/O和核電壓,以方便用戶平衡設計的性能和功耗之間的關系。IGLOO的時鐘結構可以沒有副作用的對全局信號和局部信號進行門控制。另外IGLOO的RAM模塊具有LP和F*F端口來控制RAM本身的靜態功耗。系統溫度及功耗概況

工業、汽車電子、軍事, 甚至商業類客戶都會對系統的溫度和運行模式的概況有規定。這些概況指引我們在設計時要注意哪些地方以及精力該如何分配。IGLOO器件的低功耗工藝和硅片設計由Actel來保證,用戶所要關注的是:關心器件的選型、掌握所使用的FPGA的架構、掌握PCB的板級布局(主要是電容及I/O的走線)。

對于同一系列的器件來說,器件的die越小,器件的功耗也會越小。也就是說,在選用器件的時候,應該盡量選擇規模小的器件。選定器件后,可以在設計過程中,通過一些技巧盡可能的少占用資源,比如通過時分復用的方式少占用I/O,共享加法、乘法等算法邏輯,共享RAM等,同時也有必要了解所選用的FPGA的架構。

用戶需要在功耗和速度之間做平衡,在對速度性能要求不高的時候,盡量使用低的核電壓和低電壓的I/O接口標準。根據設計工作的實際狀況,在某些時候將當前不工作的資源關掉,比如通過控制SRAM的LP或BLK引腳,使其在不工作的時候可以被關斷,或者是通過Flash Freeze端口進入Fresh Frezee模式以降低靜態功耗。在PLL不需要工作的時候,通過Power Down引腳將其關掉,不過需要注意的是,需要考慮重新開啟以后,PLL的鎖定時間對系統是不是有影響。關掉沒有輸入總線的I/O Bank。

注意,不要濫用上拉/下拉電阻。在活動模式下,如果總線被反向模式驅動(如上拉的被“0”驅動,或下拉的被“1”驅動),那么每個I/O上的電流會增加。要預防被驅動的總線進入3態狀態。除非FPGA的工作時間確實短,否則建議跟板子設計者溝通以確保對輸入進行持續的驅動。

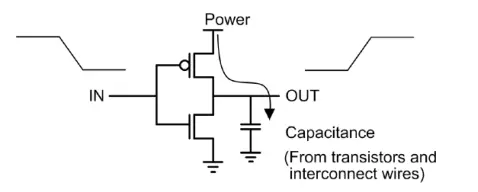

要降低設計的動態功耗,首先要了解影響動態功耗的因素。動態功耗通常和電壓、信號翻轉頻率、容性負載正相關,設計所占用的邏輯資源越多、時鐘頻率越高、I/O和RAM越多,動態功耗就越大。同時也需要分析設計的動態功耗概況。

確定要降低的動態功耗的目標,如果要降低的動態功耗的目標是目前整個系統動態功耗的20%,那么選用Actel的IGLOO器件或許就可以實現所要達到的目標。如果目標是80%,那么除了選用IGLOO器件外,還需要從系統和架構上去考慮。

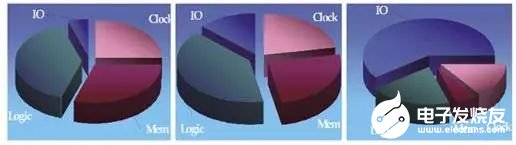

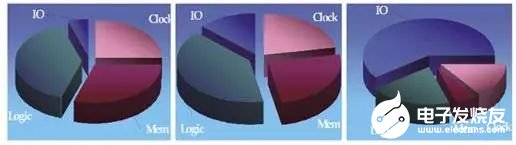

針對不同的系統功耗的概況,梳理動態功耗的重點,見圖1。針對Case1中動態功耗的示意圖,我們可以看出其功耗主要分布在邏輯、存儲和時鐘方面,這樣我們的精力就不能放在如何降低I/O的功耗上去,而針對Case3這種情況,如果要降低動態功耗,就必須要解決I/O上的功耗問題。

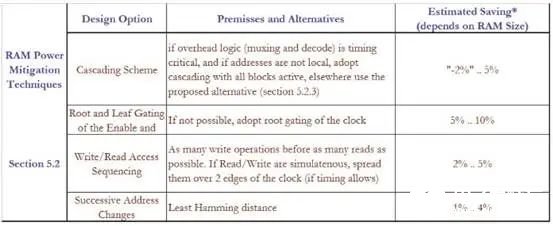

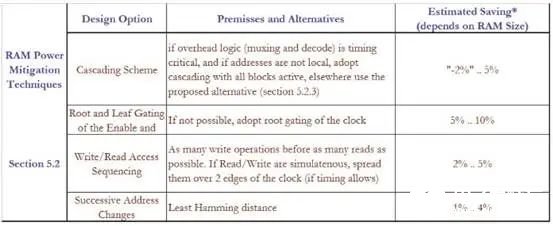

要減少RAM的功耗,除了對RAM的控制和時鐘信號進行門控制以外,還需要知道RAM的讀和寫分別對功耗的影響有多少。地址變化、讀寫順序、RAM級聯方式對功耗的影響。

對RAM進行讀操作涉及到:控制所存地址和控制鎖存、行的預譯碼電路、讀的列譯碼電路、行的最終譯碼電路、讀的列譯碼控制、傳感放大器、數據輸出選擇和鎖存電路、Sense enable logic、讀控制電路、Bit-line預充電電路等十個相關電路。而對RAM進行寫操作需要涉及到的電路有:地址和控制鎖存、行的預譯碼電路、寫的列譯碼電路、行的最終解碼控制、寫的列譯碼控制、寫驅動電路和Bit Line預充電電路。因此,相比較而言,讀操作會比寫操作消耗更多的功耗。

RAM的讀寫地址改變的方式,也會對功耗有不同的影響。連續操作地址之間的漢明距離越小,產生的功耗也越小。反之亦然。也就是說當前操作的地址和上次操作的地址之間變化的位數越少,所產生的功耗也會越小。

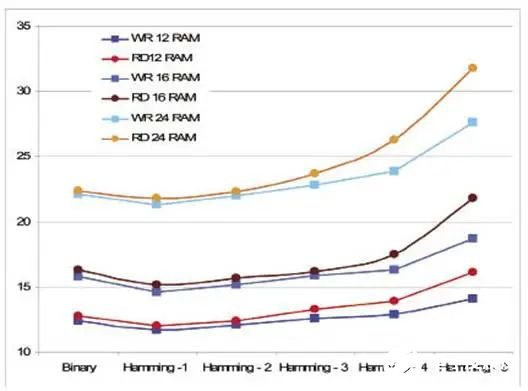

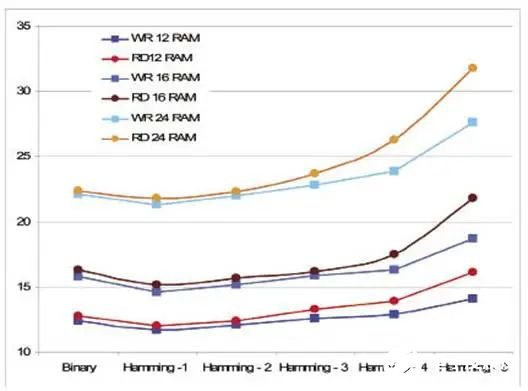

讀寫間隔操作和連續讀、連續寫操作相比,要產生多一些的功耗。從圖2中分別對12塊RAM、16塊RAM和24塊RAM做的測試結果看,同樣的操作條件下,RAM塊數越多,連續操作地址之間的漢明距離越長,功耗就越大。同樣的塊數和連續操作之間的漢明距離,寫-讀三次會比三次寫三次讀消耗的功耗要大。

圖1 不同系統的動態功耗在線座談精華

圖2 寫讀操作順序vs.讀序列后跟寫序列操作

通過前面所述,我們可以通過調整RAM的訪問順序降低RAM的功耗。可能的話,對RAM少進行讀操作,盡可能一次多讀一些數據或者多寫一些數據,少一些讀寫操作之間的切換。如果在連續相同操作的地址之間,漢明距離能保持最小的話更好。也可以考慮在反向時鐘沿上對RAM進行讀寫操作,以降低RAM的峰值功耗。

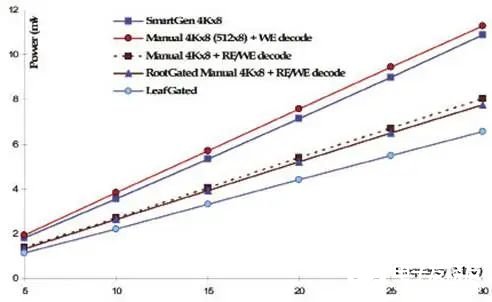

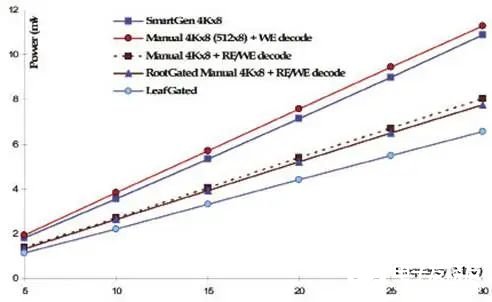

不同的RAM級聯架構所產生的功耗也不同。如果想獲得一個4K×4的RAM,有許多不同的實現方式。從圖3中可以看出,根據這些不同的實現方式,對每塊RAM的讀寫時鐘控制,進行門控制所產生的功耗是最低的。

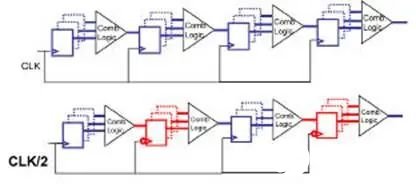

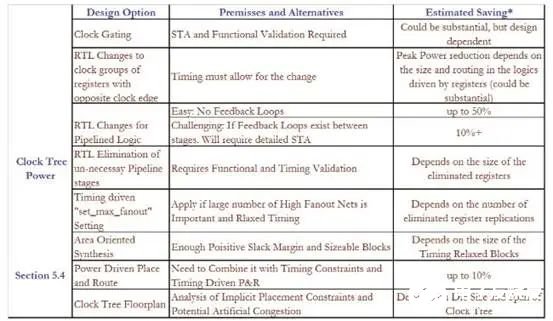

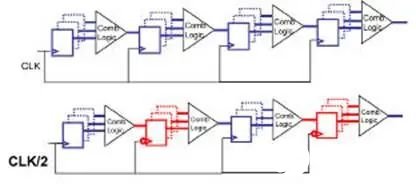

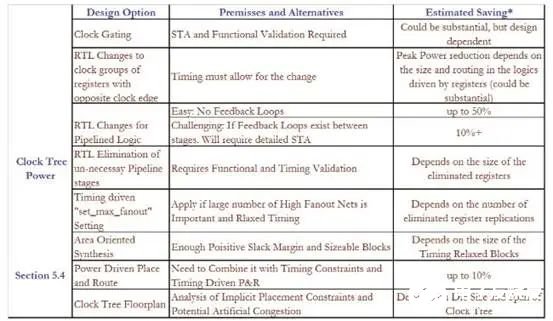

在降低時鐘樹的功耗方面,常用的方法有使用門控時鐘,對常用的流水線時鐘結構進行修改,盡量使用FPGA內部的全局時鐘資源等。通過對常用的流水線時鐘結構在RTL級進行修改,就像在圖4中所看到的,做正反時鐘沿間隔,這樣時鐘頻率可以減慢一半,可以節省該時鐘路徑一半的功耗。同樣可以通過人工對時鐘域進行平面布局,來降低時鐘樹產生的功耗。這種方式對工程師的要求相對較高。Actel的設計師提供基于功耗驅動的布局布線策略。選擇該策略,布局布線工具自動會在滿足時序要求的情況下,盡可能的降低布局功耗。

圖3 根時鐘vs.葉時鐘vs.門控允許

圖4 對常用的流水線時鐘結構在RTL級做修改

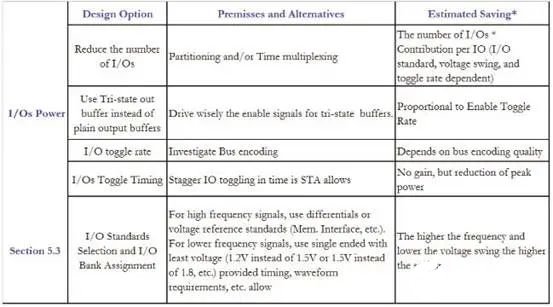

要降低邏輯和走線的功耗,需要調整綜合選項、了解算法/功能塊的架構和功耗概況,通過減少信號的翻轉來降低功耗。不同的綜合選項和策略會對動態功耗有影響,基本上需要注意的是全局時序的設定以及set_max_fanout選項,以及是選用面積優先還是時序優先的綜合策略。

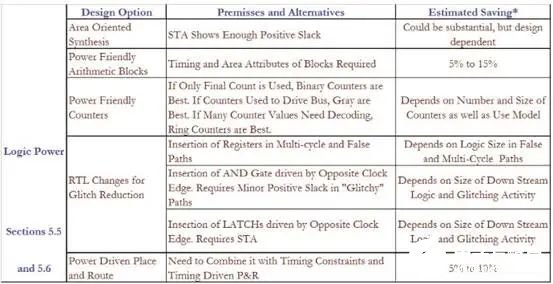

通過對DesignWare和一些私有的加法器和不同頻率下的功耗的評估,DesignWare下面的BK加法器在功耗方面是最友好的。針對同樣5%到10%的速度降級,BK加法器和其他的私有加法器的核相比,可以減少10%到15%的面積和功耗。在選擇乘法器的時候,必須要考慮乘法器的面積、功耗和速度。

計數器在設計中有不同的用法,有的用于計算事件發生的順序或者用掉的時間,有的用于驅動類似于RAM的地址總線、數據總線、狀態機的下一跳狀態或者輸出邏輯,有的用于當輸出的值達到不同的解碼值時做不同的設定的處理。根據不同的用途可以考慮用二進制順序計數、格雷碼計數、環形計數的實現方法。如果計數器只是用于產生一些標記,建議采用二進制的實現方式;如果計數器用于驅動一個大的負載總線,建議用格雷碼計數器;如果多個計數器的值需要被解碼,環形計數器是最佳選擇(譯碼邏輯是最小的)。

通過降低邏輯的翻轉率來降低動態功耗

首先在設計中,需要盡量避免不必要的翻轉,可以通過下面幾個步驟來實現這一目標:首先分析哪些邏輯的翻轉是不必要的,隨后對不必要的邏輯翻轉的傳播進行限制,展開邏輯翻轉的時間。

減少邏輯可能產生的毛刺,先標識出翻轉率高的網絡以及它們的驅動,然后對驅動單元輸入的最壞時序情況做評估,隨后將毛刺的源往前調或往后調,然后對驅動單元的輸入的最壞時序情況做評估,最后在驅動的邏輯后面插入一級觸發器,根據先前的評估情況來決定用路徑上其他時序元件的相同時鐘沿或者相反的時鐘沿來驅動觸發器。即使是在單周期路徑上面,如果有足夠的slack來增加一個與門以及相關走線,那么就可以用與門的另外一個輸入(毛刺源驅動寄存器)的反相時鐘沿,從而減少毛刺。在某些情況下,可以通過伸展反轉時間來降低毛刺的峰值功耗。

建議設計者要了解最終系統的運行模式,以及每種模式下系統的功耗概況。如果系統處于睡眠模式或者關閉模式的時間較長,需要觀察浪涌電流和編程電流的影響,并處理好靜態功耗。需要檢查設計的動態功耗概況,找出功耗的主要瓶頸,根據概括表(圖5~圖8)找出最好的解決方法。

圖5 RAM 動態功耗概括表

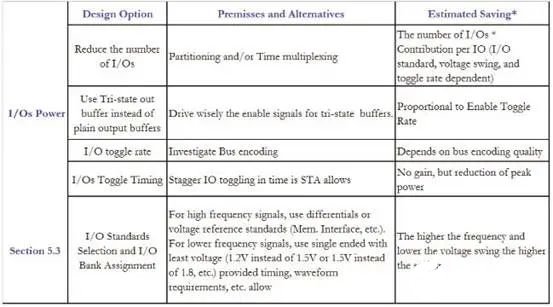

圖6 I/O功耗概括表

圖7 時鐘樹功耗概括表

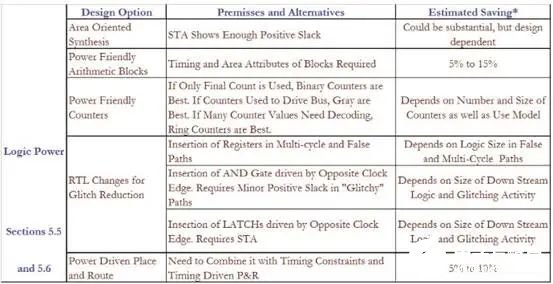

圖8 邏輯功耗概括表在對照概括表之前,只要時序允許,可以修改RTL代碼;保證修改以后的功能和時序有效性;也可以嘗試調整綜合選項以及使用基于功耗優先的策略來進行布局布線。

采用IGLOO器件的低功耗優勢從哪些方面獲得呢?首先來自IGLOO器件本身對漏電流源頭的控制,以及器件所提供的各種節省功耗的特性的實現和各種最少功耗數據存儲技術的實現。除此之外,設計中采用一些低功耗技巧,也可以降低靜態功耗。

IGLOO具有功耗友好的器件架構,能提供靜態、睡眠、Flash*Freeze功耗模式,允許采用動態電壓和頻率調節技術來降低系統整體實際功耗。提供可選擇的1.2V和1.5V的I/O和核電壓,以方便用戶平衡設計的性能和功耗之間的關系。IGLOO的時鐘結構可以沒有副作用的對全局信號和局部信號進行門控制。另外IGLOO的RAM模塊具有LP和F*F端口來控制RAM本身的靜態功耗。系統溫度及功耗概況

工業、汽車電子、軍事, 甚至商業類客戶都會對系統的溫度和運行模式的概況有規定。這些概況指引我們在設計時要注意哪些地方以及精力該如何分配。IGLOO器件的低功耗工藝和硅片設計由Actel來保證,用戶所要關注的是:關心器件的選型、掌握所使用的FPGA的架構、掌握PCB的板級布局(主要是電容及I/O的走線)。

對于同一系列的器件來說,器件的die越小,器件的功耗也會越小。也就是說,在選用器件的時候,應該盡量選擇規模小的器件。選定器件后,可以在設計過程中,通過一些技巧盡可能的少占用資源,比如通過時分復用的方式少占用I/O,共享加法、乘法等算法邏輯,共享RAM等,同時也有必要了解所選用的FPGA的架構。

用戶需要在功耗和速度之間做平衡,在對速度性能要求不高的時候,盡量使用低的核電壓和低電壓的I/O接口標準。根據設計工作的實際狀況,在某些時候將當前不工作的資源關掉,比如通過控制SRAM的LP或BLK引腳,使其在不工作的時候可以被關斷,或者是通過Flash Freeze端口進入Fresh Frezee模式以降低靜態功耗。在PLL不需要工作的時候,通過Power Down引腳將其關掉,不過需要注意的是,需要考慮重新開啟以后,PLL的鎖定時間對系統是不是有影響。關掉沒有輸入總線的I/O Bank。

注意,不要濫用上拉/下拉電阻。在活動模式下,如果總線被反向模式驅動(如上拉的被“0”驅動,或下拉的被“1”驅動),那么每個I/O上的電流會增加。要預防被驅動的總線進入3態狀態。除非FPGA的工作時間確實短,否則建議跟板子設計者溝通以確保對輸入進行持續的驅動。

要降低設計的動態功耗,首先要了解影響動態功耗的因素。動態功耗通常和電壓、信號翻轉頻率、容性負載正相關,設計所占用的邏輯資源越多、時鐘頻率越高、I/O和RAM越多,動態功耗就越大。同時也需要分析設計的動態功耗概況。

確定要降低的動態功耗的目標,如果要降低的動態功耗的目標是目前整個系統動態功耗的20%,那么選用Actel的IGLOO器件或許就可以實現所要達到的目標。如果目標是80%,那么除了選用IGLOO器件外,還需要從系統和架構上去考慮。

針對不同的系統功耗的概況,梳理動態功耗的重點,見圖1。針對Case1中動態功耗的示意圖,我們可以看出其功耗主要分布在邏輯、存儲和時鐘方面,這樣我們的精力就不能放在如何降低I/O的功耗上去,而針對Case3這種情況,如果要降低動態功耗,就必須要解決I/O上的功耗問題。

要減少RAM的功耗,除了對RAM的控制和時鐘信號進行門控制以外,還需要知道RAM的讀和寫分別對功耗的影響有多少。地址變化、讀寫順序、RAM級聯方式對功耗的影響。

對RAM進行讀操作涉及到:控制所存地址和控制鎖存、行的預譯碼電路、讀的列譯碼電路、行的最終譯碼電路、讀的列譯碼控制、傳感放大器、數據輸出選擇和鎖存電路、Sense enable logic、讀控制電路、Bit-line預充電電路等十個相關電路。而對RAM進行寫操作需要涉及到的電路有:地址和控制鎖存、行的預譯碼電路、寫的列譯碼電路、行的最終解碼控制、寫的列譯碼控制、寫驅動電路和Bit Line預充電電路。因此,相比較而言,讀操作會比寫操作消耗更多的功耗。

RAM的讀寫地址改變的方式,也會對功耗有不同的影響。連續操作地址之間的漢明距離越小,產生的功耗也越小。反之亦然。也就是說當前操作的地址和上次操作的地址之間變化的位數越少,所產生的功耗也會越小。

讀寫間隔操作和連續讀、連續寫操作相比,要產生多一些的功耗。從圖2中分別對12塊RAM、16塊RAM和24塊RAM做的測試結果看,同樣的操作條件下,RAM塊數越多,連續操作地址之間的漢明距離越長,功耗就越大。同樣的塊數和連續操作之間的漢明距離,寫-讀三次會比三次寫三次讀消耗的功耗要大。

圖1 不同系統的動態功耗在線座談精華

圖2 寫讀操作順序vs.讀序列后跟寫序列操作

通過前面所述,我們可以通過調整RAM的訪問順序降低RAM的功耗。可能的話,對RAM少進行讀操作,盡可能一次多讀一些數據或者多寫一些數據,少一些讀寫操作之間的切換。如果在連續相同操作的地址之間,漢明距離能保持最小的話更好。也可以考慮在反向時鐘沿上對RAM進行讀寫操作,以降低RAM的峰值功耗。

不同的RAM級聯架構所產生的功耗也不同。如果想獲得一個4K×4的RAM,有許多不同的實現方式。從圖3中可以看出,根據這些不同的實現方式,對每塊RAM的讀寫時鐘控制,進行門控制所產生的功耗是最低的。

在降低時鐘樹的功耗方面,常用的方法有使用門控時鐘,對常用的流水線時鐘結構進行修改,盡量使用FPGA內部的全局時鐘資源等。通過對常用的流水線時鐘結構在RTL級進行修改,就像在圖4中所看到的,做正反時鐘沿間隔,這樣時鐘頻率可以減慢一半,可以節省該時鐘路徑一半的功耗。同樣可以通過人工對時鐘域進行平面布局,來降低時鐘樹產生的功耗。這種方式對工程師的要求相對較高。Actel的設計師提供基于功耗驅動的布局布線策略。選擇該策略,布局布線工具自動會在滿足時序要求的情況下,盡可能的降低布局功耗。

圖3 根時鐘vs.葉時鐘vs.門控允許

圖4 對常用的流水線時鐘結構在RTL級做修改

要降低邏輯和走線的功耗,需要調整綜合選項、了解算法/功能塊的架構和功耗概況,通過減少信號的翻轉來降低功耗。不同的綜合選項和策略會對動態功耗有影響,基本上需要注意的是全局時序的設定以及set_max_fanout選項,以及是選用面積優先還是時序優先的綜合策略。

通過對DesignWare和一些私有的加法器和不同頻率下的功耗的評估,DesignWare下面的BK加法器在功耗方面是最友好的。針對同樣5%到10%的速度降級,BK加法器和其他的私有加法器的核相比,可以減少10%到15%的面積和功耗。在選擇乘法器的時候,必須要考慮乘法器的面積、功耗和速度。

計數器在設計中有不同的用法,有的用于計算事件發生的順序或者用掉的時間,有的用于驅動類似于RAM的地址總線、數據總線、狀態機的下一跳狀態或者輸出邏輯,有的用于當輸出的值達到不同的解碼值時做不同的設定的處理。根據不同的用途可以考慮用二進制順序計數、格雷碼計數、環形計數的實現方法。如果計數器只是用于產生一些標記,建議采用二進制的實現方式;如果計數器用于驅動一個大的負載總線,建議用格雷碼計數器;如果多個計數器的值需要被解碼,環形計數器是最佳選擇(譯碼邏輯是最小的)。

通過降低邏輯的翻轉率來降低動態功耗

首先在設計中,需要盡量避免不必要的翻轉,可以通過下面幾個步驟來實現這一目標:首先分析哪些邏輯的翻轉是不必要的,隨后對不必要的邏輯翻轉的傳播進行限制,展開邏輯翻轉的時間。

減少邏輯可能產生的毛刺,先標識出翻轉率高的網絡以及它們的驅動,然后對驅動單元輸入的最壞時序情況做評估,隨后將毛刺的源往前調或往后調,然后對驅動單元的輸入的最壞時序情況做評估,最后在驅動的邏輯后面插入一級觸發器,根據先前的評估情況來決定用路徑上其他時序元件的相同時鐘沿或者相反的時鐘沿來驅動觸發器。即使是在單周期路徑上面,如果有足夠的slack來增加一個與門以及相關走線,那么就可以用與門的另外一個輸入(毛刺源驅動寄存器)的反相時鐘沿,從而減少毛刺。在某些情況下,可以通過伸展反轉時間來降低毛刺的峰值功耗。

建議設計者要了解最終系統的運行模式,以及每種模式下系統的功耗概況。如果系統處于睡眠模式或者關閉模式的時間較長,需要觀察浪涌電流和編程電流的影響,并處理好靜態功耗。需要檢查設計的動態功耗概況,找出功耗的主要瓶頸,根據概括表(圖5~圖8)找出最好的解決方法。

圖5 RAM 動態功耗概括表

圖6 I/O功耗概括表

圖7 時鐘樹功耗概括表

圖8 邏輯功耗概括表在對照概括表之前,只要時序允許,可以修改RTL代碼;保證修改以后的功能和時序有效性;也可以嘗試調整綜合選項以及使用基于功耗優先的策略來進行布局布線。

有你想看的精彩 至芯科技FPGA就業培訓班——助你步入成功之路、9月23號北京中心開課、歡迎咨詢! 基于FPGA的攝像機傳感器接口 為什么研究浮點加法運算,對FPGA實現方法很有必要?

掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:FPGA設計技巧,如何能有效降低靜態功耗?

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603977

原文標題:FPGA設計技巧,如何能有效降低靜態功耗?

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何降低電子開關的功耗

電子開關是現代電子系統中不可或缺的組成部分,它們控制電流的流動,實現設備的開啟和關閉。然而,隨著電子設備功能的增強和集成度的提高,功耗問題也日益突出。降低電子開關的功耗不僅有助于節約能源,還能

如何降低AD1247的功耗?

為了使AD1247進入睡眠模式以降低功耗嘗試了以下兩種方法:

1、將START置為低電平 ,但是至低電平后電流沒有變化;

2、通過SLEEP指令,這個進入睡眠后AD1247的確不工作了,喚醒之后

發表于 12-24 07:51

TPA3116靜態功耗靜態電流比較大是什么原因導致的?

關于TPA3116靜態功耗大,在TI的論壇里面發現幾乎所有的電感發熱都是說是因為輸出LC電路導致

1,想問一下這個靜態功耗靜態電流比較大

發表于 10-12 08:35

如何測試TPA3118和TPA3116的靜態電流和靜態功耗?

1.如何測試TPA3118和TPA3116的靜態電流和靜態功耗?

2.測試時候需要帶負載嘛?(是否需要接喇叭)

3.如果用萬用表測試應該怎么測?

發表于 10-12 06:54

物聯網系統中TCP低功耗產品長連接狀態下降低功耗功能的實現方案

01 ?概述 TCP相關內容參考文章《物聯網行業中TCP通信協議介紹以及如何實現》 02 ?功耗的組成 低功耗技術就是一系列的降低功耗的技術。 在了解低功耗技術之前,我們必須先了解

談一談FPGA設計中的功率計算

和動態功率。 盡管FPGA廠商承諾將提供切實可用的低功耗器件,但由于工藝技術從130納米縮小到90納米、65納米或更加小的線條,晶體管固有的漏電加劇了,靜態功耗也增加了。此外,使用

發表于 07-31 22:37

工業物聯網系統如何有效降低儲能設備運維成本

在現代工業發展的浪潮中,儲能設備作為能源體系的重要組成部分,扮演著不可或缺的角色。儲能系統不僅可以提高電網的安全性和穩定性,還能有效利用電力峰谷電價差異,降低電力系統的成本。

OPA454如何降低功耗?

opa454 供電+60V/-15V,輸出空載懸空,放大倍數5倍,同向放大,輸入0~10V正弦波100hz,輸出為50v正弦波,發現功耗很大,有降低功耗措施?

發表于 07-29 06:32

wifi smartconfig時功耗比較大,如何降低?

現在wifi 的smartconfig 時候功耗比較大,現在達不到要求,需要在配網時降低10mA。

1,如何通過編程的手段進行降低?

2,這個需要考慮配網時跟路由器之間的距離嗎?

發表于 07-10 08:09

FSMC讀寫NAND后,如何能夠拉高NCE片選信號,以求降低功耗?

請教大家問題:

FSMC讀寫NAND后,如何能夠拉高NCE片選信號,以求降低功耗!

手冊和實際測試結果只能通過bank切換才能實現!bank2和bank3可以單獨切換,釋放NCE,但如何同時釋放NC呢?

不知道大家有沒有遇到這樣的問題!

謝謝大家

發表于 04-28 08:36

如何降低LoRa模塊的功耗以延長電池壽命?

我正在開發一個使用 LoRa模塊的物聯網項目, 但我發現 LoRa 模塊的功耗比較高, 這可能會導致電池消耗得很快.我正在尋找一些建議來幫助我降低 LoRa 模塊的功耗以延長電池壽命.我已經考慮了

發表于 03-01 07:38

FPGA設計技巧,如何能有效降低靜態功耗?

FPGA設計技巧,如何能有效降低靜態功耗?

評論