作者:Adam Taylor

編者按:全新的 FPGA 架構方法帶來了更精細的控制和更大的靈活性,以滿足機器學習 (ML) 和人工智能 (AI) 的需求。本系列文章包括兩部分,第 1部分介紹了 Efinix 一款此類架構的產品,以及如何借助開發板開始使用該產品。本文是第 2 部分,討論了開發板與外部器件和外設(如攝像頭)的連接,以及如何利用

FPGA 消除圖像處理的瓶頸。

從工業控制和安全到機器人、航空航天和汽車,FPGA 在許多應用中扮演著重要角色。憑借可編程邏輯內核的靈活性及其廣泛的接口能力,FPGA 在可以部署機器學習(ML) 的影像處理中的應用日漸廣泛。由于其并行邏輯結構,FPGA 非常適合用來實現具有多個高速攝像頭接口的解決方案。此外,FPGA還能在邏輯中使用專門的處理管道,從而消除與基于 CPU 或 GPU 的解決方案相關的共享資源瓶頸。

本文將再次介紹 Efinix 的 Titanium FPGA,并探討該 FPGA 的 Ti180 M484開發板附帶的參考圖像處理應用。其目的是了解設計的構成部分,并明確 FPGA 技術能夠消除哪些方面的瓶頸或為開發人員帶來其他好處。

基于 Ti180 M484 的參考設計

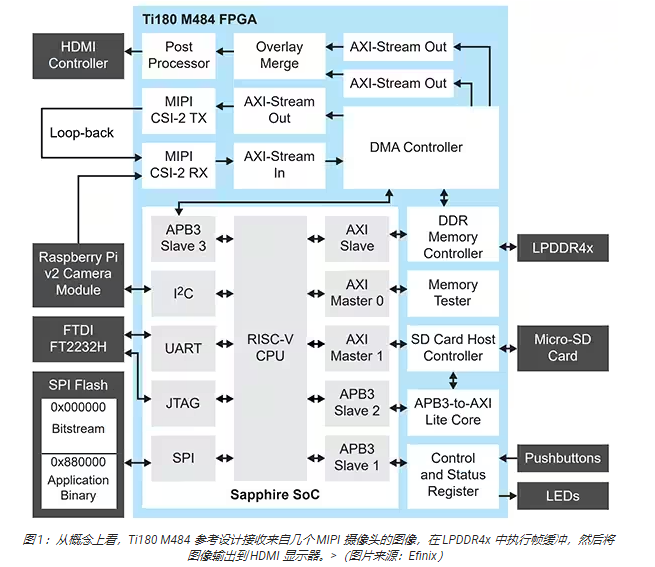

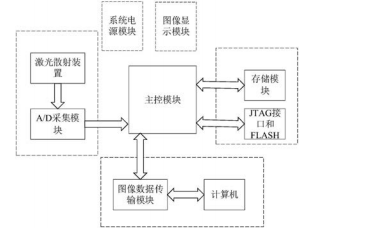

從概念上看,該參考設計(圖 1)接收來自幾個移動行業處理器接口 (MIPI) 攝像頭的圖像,在 LPDDR4x

中執行幀緩沖,然后將圖像輸出到高清多媒體接口 (HDMI) 顯示器。利用一個 FPGA 夾層卡 (FMC) 和開發板上的四個 Samtec QSE接口提供攝像頭輸入和 HDMI 輸出。

FMC 轉 QSE 擴展卡與 HDMI 子卡配合使用,提供輸出視頻路徑,而 3 個 QSE 連接器用于與 DFRobot SEN0494 MIPI攝像頭連接。如果沒有多個 MIPI 攝像頭,可以使用單個攝像頭,通過回環單個攝像頭通道來模擬其他攝像頭。

從高層次看,這種應用可能看起來很簡單。但是要以高幀率接收多個高清 (HD) MIPI 流頗具挑戰性。這恰好是 FPGA技術的優勢所在,因為它允許設計人員并行利用多個 MIPI 流。

該參考設計的架構利用了 FPGA 的并行和順序處理結構。并行結構用于實現圖像處理管道,而 RISC-V 處理器提供用于 FPGA 查詢表 (LUT)的順序處理。

在許多基于 FPGA的圖像處理系統中,圖像處理管道可以分成兩個部分,即輸入和輸出流。輸入流連接到攝像頭/傳感器接口,各種處理功能則應用至傳感器輸出。這些處理功能包括 Bayer轉換、自動白平衡和其他增強功能。在輸出流中,準備圖像用于顯示。這包括改變顏色空間(例如從 RGB 更改為 YUV),以及后處理為所需的輸出格式,如HDMI。

通常,輸入圖像處理鏈以傳感器的像素時鐘頻率運行。這與輸出鏈的時序不同,輸出鏈以輸出顯示頻率進行處理。

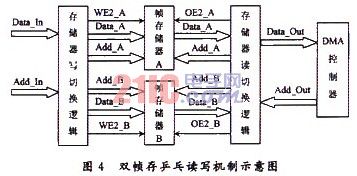

幀緩沖區用于連接輸入和輸出處理管道,它通常存儲在 LPDDR4x等外部高性能存儲器中。該幀緩沖區在輸入和輸出管道之間去耦,從而允許以適當的時鐘頻率通過直接內存訪問來訪問幀緩沖區。

Ti180 參考設計采用了與上述概念類似的方法。輸入圖像處理管道實現了一個 MIPI 攝像頭串行接口 2 (CSI-2) 接收器知識產權 (IP)內核,該內核建立在支持 MIPI 物理層 (MIPI D-PHY) 的 Titanium FPGA 輸入/輸出 (I/O) 之上。MIPI接口頗為復雜,因為除了低速和高速通信,它還在同一差分對上同時使用單端和差分信號。將 MIPI D-PHY 集成到 FPGA I/O中,降低了電路板設計的復雜性,同時還可簡化物料清單 (BOM)。

收到攝像頭的圖像流后,參考設計會將 MIPI CSI-2 RX 的輸出轉換為高級可擴展接口 (AXI) 流。AXI

流屬于單向高速接口,提供從主設備到從設備的數據流。除了在主設備和從設備之間傳輸的握手信號(tvalid 和tready),還提供了邊帶信號。這些邊帶信號可用于傳遞圖像時序信息,如幀的開始和行的結束。

AXI 流是圖像處理應用的理想選擇,使 Efinix 能夠提供一系列的圖像處理 IP,然后可以根據應用的需要輕松集成到處理鏈中。

接收后,MIPI CSI-2 圖像數據和時序信號被轉換為 AXI 流,并輸入到直接內存訪問 (DMA) 模塊,該模塊將圖像幀寫入 LPDDR4x并充當幀緩沖區。

此 DMA 模塊在 Sapphire 片上系統 (SoC) 內 FPGA 中的 RISC-V 內核控制下運行。該 SoC 提供停止和開始 DMA寫入等控制功能,此外還為 DMA 寫入通道提供必要的信息,以便將圖像數據正確寫入

LPDDR4x。這包括有關存儲器位置的信息以及圖像寬度和高度(以字節為單位)。

該參考設計中的輸出通道在 RISC-V SoC 的控制下從 LPDDR4x 幀緩沖區讀取圖像信息。數據作為 AXI 流從 DMA IP輸出,然后從傳感器提供的 RAW 格式轉換為 RGB 格式(圖 2),并準備通過板載 Analog Devices 的 ADV7511 HDMI發射器輸出。

借助 DMA,Sapphire SoC RISC-V 也能夠訪問存儲于幀緩沖區中的圖像,以及統計和圖像信息摘要。Sapphire SoC 還能將覆蓋層寫入LPDDR4x 中,以便與輸出的視頻流合并。

現代 CMOS 圖像傳感器 (CIS) 有幾種工作模式,可配置為提供片上處理,以及幾種不同的輸出格式和時鐘方案。通常通過 I2C 接口提供這種配置。在該Efinix 參考設計中,與 MIPI 攝像頭的 I2C 通信由 Sapphire SoC RISC-V 處理器提供。

在 Titanium FPGA 中集成 RISC-V 處理器減少了最終解決方案的整體尺寸,因為不需要部署會增加設計風險的復雜 FPGA狀態機,也不需要會增加 BOM 的外部處理器。

集成該處理器后,還可以支持額外的 IP 與 MicroSD 卡進行通信。這能夠支持可能需要存儲圖像以供日后分析的現實應用。

總的來說,Ti180 參考設計的架構經過優化,可實現緊湊、低成本但高性能的解決方案,使開發人員能夠通過系統集成降低 BOM 成本。

參考設計的主要優點之一是可用于在定制硬件上啟動應用開發,使開發人員能夠利用設計的關鍵元素,并以此為基礎進行所需的定制。這包括能夠利用 Efinix 的TinyML 流程來實現運行于 FPGA 上的視覺 TinyML 應用。這既可利用 FPGA 邏輯的并行特性,又可輕松地將自定義指令添加至 RISC-V處理器中,從而能夠在 FPGA 邏輯內創建加速器。

實現

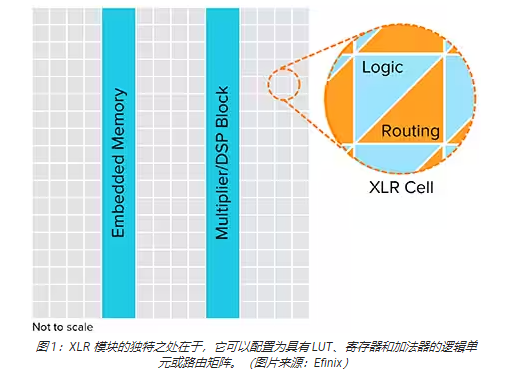

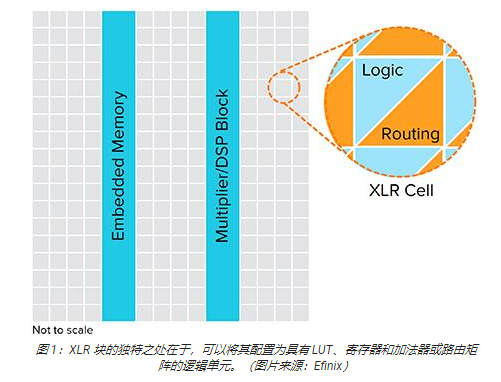

正如第 1 部分所述,Efinix 架構的獨特之處在于,它使用可交換邏輯和路由 (XLR)單元來提供路由和邏輯功能。像上述參考設計這樣的視頻系統屬于邏輯和路由都很復雜的混合系統:需要大量的邏輯來實現圖像處理功能,還需要廣泛的路由來以所需的頻率連接IP 單元。

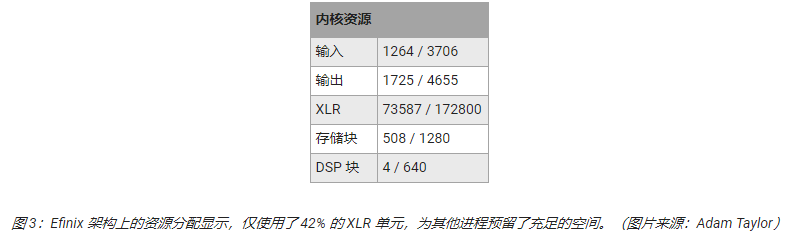

該參考設計使用了器件內約 42% 的 XLR 單元,留下了充足的空間來添加內容,包括邊緣 ML 等定制應用。

塊 RAM 和數字信號處理 (DSP) 塊的使用也非常高效,只使用了 640 個 DSP 塊中的 4 個和 40% 的存儲塊(圖 3)。

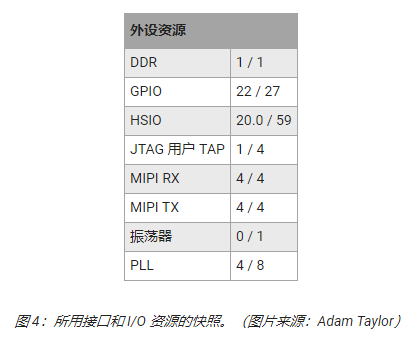

在器件 IO 上,LPDDR4x 的 DDR 接口用于為 Sapphire SoC 提供應用存儲器以及提供圖像幀緩沖區。所有器件專用的 MIPI 資源與50% 的鎖相環一起使用(圖 4)。

通用 I/O (GPIO) 用于提供 I2C 通信以及幾個連接到 Sapphire SoC 的接口,包括 NOR FLASH、USB UART 和 SD卡。HSIO 用于向 ADC7511 HDMI 發射器提供高速視頻輸出。

采用 FPGA 進行設計的一個關鍵因素是,不僅要在 FPGA 中實現和擬合設計,還要能夠在 FPGA內放置邏輯設計,并在路由時達到所需的時序性能。

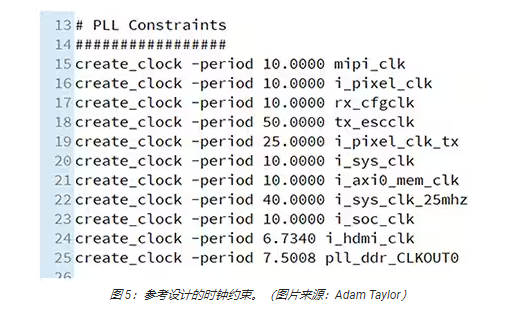

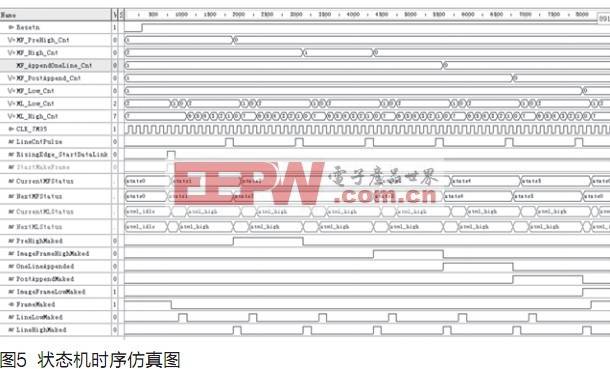

單時鐘域 FPGA 設計的時代已經一去不復返了。在 Ti180參考設計中,有幾個不同的時鐘,都以高頻率運行。最終時序表顯示了系統內時鐘達到的最大頻率。在此表中也可以看到時鐘約束中要求的時序性能(圖 5),其中 HDMI輸出時鐘的最大時鐘頻率為 148.5 MHz。

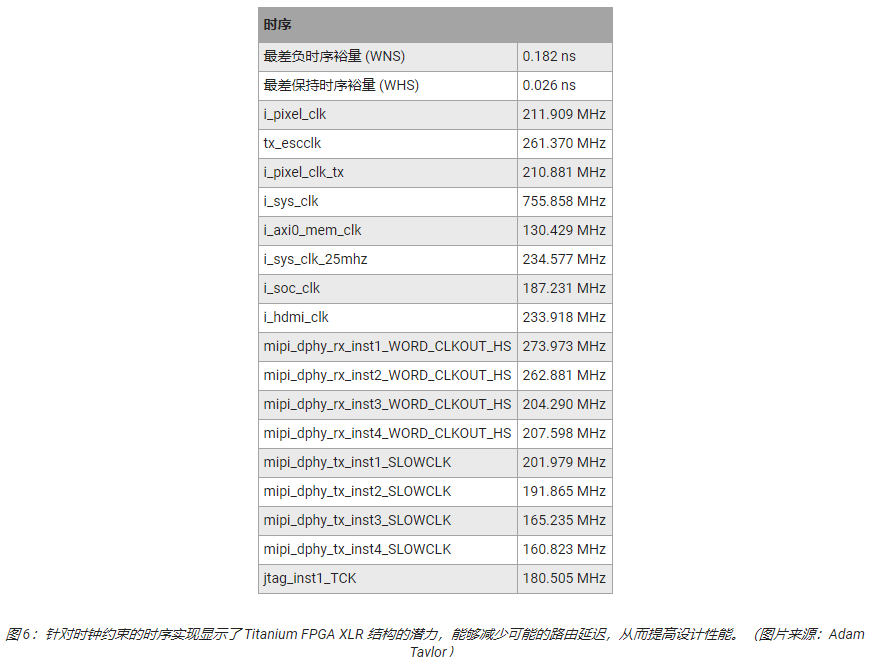

針對時鐘約束的時序實現顯示了 Titanium FPGA XLR 結構的潛力,因為它減少了可能的路由延遲,從而提高了設計性能(圖 6)。

總結

Ti180 M484 參考設計清楚地展示了 Efinix FPGA 的能力,尤其是 Ti180。該設計利用幾個獨特的 I/O

結構來實現復雜的圖像處理路徑,支持多個傳入的 MIPI 流。此圖像處理系統在軟核 Sapphire SoC的控制下運行,實現了該應用必需的順序處理元素。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603041 -

HDMI

+關注

關注

32文章

1695瀏覽量

151867 -

AI

+關注

關注

87文章

30763瀏覽量

268906 -

開發板

+關注

關注

25文章

5035瀏覽量

97384 -

ML

+關注

關注

0文章

149瀏覽量

34644

發布評論請先 登錄

相關推薦

FPGA的B超成像系統圖像采集的原理和實現

為什么以及如何使用 Efinix FPGA 進行 AI/ML 成像 — 第 1 部分:入門

為什么以及如何將 Efinix FPGA 用于 AI/ML 成像 — 第 1 部分:入門指南

新冒出來的Efinix會革掉FPGA的命么?

【HarmonyOS HiSpark AI Camera】AI圖像開發

基于FPGA的網絡圖像采集處理系統設計

為什么以及如何將 Efinix FPGA 用于 AI/ML 成像第 2 部分:圖像采集和處理

為什么以及如何將 Efinix FPGA 用于 AI/ML 成像第 2 部分:圖像采集和處理

評論