RISC-V 是一種模塊化指令集架構 (ISA),具有強大的定制能力,在實現創新和差異化的同時而不會出現碎片化現象。在已批準/標準的 ISA 擴展(如整數指令或浮點指令)的基礎模塊之上,設計人員可以通過添加自定義指令而實現純粹的設計自由!

通過添加自定義指令而實現更好的性能,更小的內存占用或者更低的功率,意味著軟件(最終應用程序)要針對特定的 RISC-V ISA 進行編譯。軟件開發工具包(SDK)必須清楚地了解 RISC-V 處理器實現了哪些 ISA 模塊,這樣才能自動利用這些模塊。這些指令包括標準指令和定制指令。

但是如何為特定的 RISC-V ISA 獲取最佳的 SDK 呢?這里不得不提到 SDK 的重要組成部分--C/C++ 編譯器。編譯器必須盡可能能夠自動、明智地使用這些自定義指令。

什么是 LLVM C/C++ 編譯器?

LLVM(低級虛擬機)是一套編譯器和工具,如匯編器、鏈接器或調試器。我們可以把重點放在編譯器上。

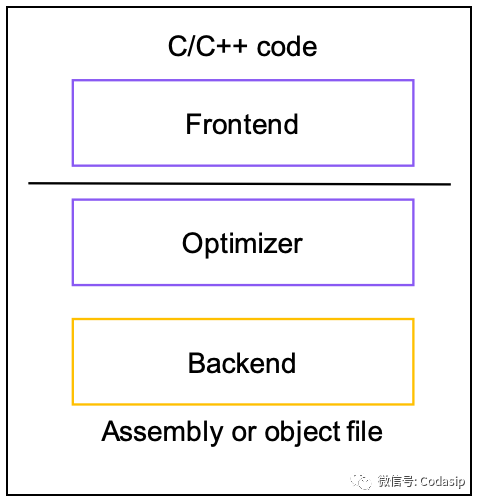

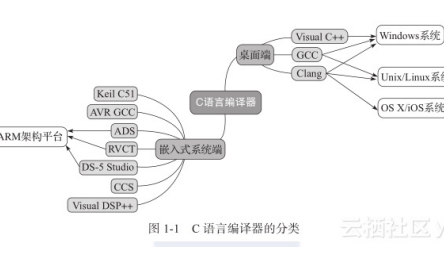

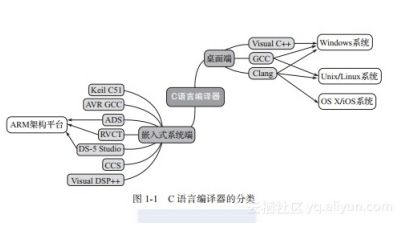

與其他編譯器一樣,LLVM 編譯器可分為三個部分:前端、優化器(也稱中端)和后端,如下圖所示。每一層都有不同的用途。

LLVM 編譯器前端

前端將 C 或 C++ 源代碼作為文本文件輸入。前端會對其進行解析,并創建一個中間表達(IR)。IR 以機器格式表示輸入內容。

LLVM 編譯器優化器

優化器接收 IR,主要針對獨立的優化(如循環展開或常量/變量傳播),并生成經過優化的 IR。

LLVM 編譯器后端

后端接收優化后的 IR,并執行與目標相關的優化、寄存器分配、堆棧操作等。最后生成處理器的匯編代碼。

對于可重定位目標性而言,后端是最重要的部分,因為它必須了解目標架構、指令等信息。而 Codasip 的解決方案生成的正是編譯器后端。

重定向 LLVM C/C++ 編譯器

對于這個問題,Codasip 的做法如下:

以CodAL作為處理器描述的單一來源

RISC-V ISA(包括自定義指令)是通過 CodAL 語言(一種基于 C 語言的處理器高級描述語言)捕獲的。該語言捕獲了所有重要信息,包括指令的文本形式、二進制編碼以及更重要的指令行為。CodAL 描述還包含以下信息:不同類型的危險是如何遞交的(它會影響指令調度)、指令是如何執行的(單周期、多周期)、處理器的應用二進制接口(例如,哪些寄存器用于堆棧)或其他微體系結構描述等。此外它還包含其它 C/C++ 編譯器功能(例如窺孔優化-peephole optimizations)的說明。

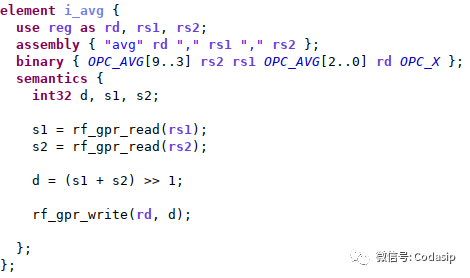

下面的示例顯示了一條表示兩個數字平均值的簡單指令。

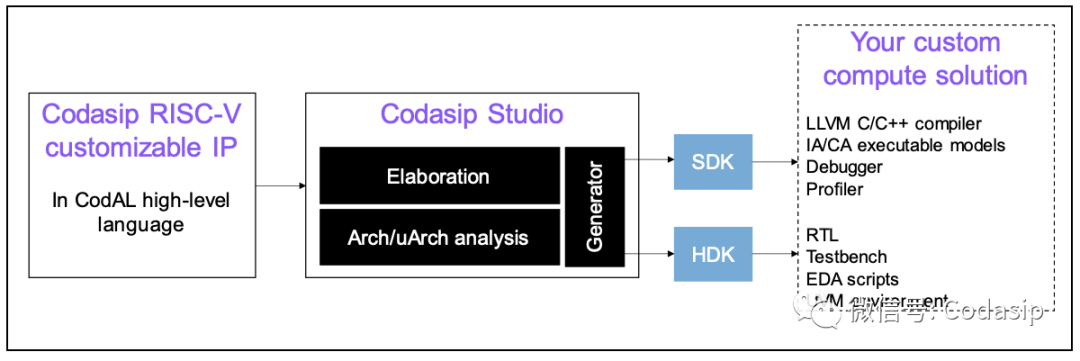

根據這一描述可以生成一系列工具。從下圖中可以看到,生成的輸出之一是 LLVM C/C++ 編譯器。

C/C++ 編譯器生成器會解析所有已描述的指令和微架構描述。然后提取指令語義、ABI 或時序,為前端和優化器生成新的后端和配置文件。換句話說,前端和優化器經過預編譯和配置,可以快速探索設計空間。而后端則需要編譯。生成的后端可以接收到 RISC-V 處理器的每一條指令,且上述指令可以由生成的 C/C++ 編譯器自動使用,也可以通過自動生成的內建函數或內聯匯編使用。

最獨特的是,生成的后端向設計人員開放。如果設計人員想要添加新的 LLVM optimization pass,假設已經用 C++ 編寫了一個optimization pass,那么就可以隨時添加新的pass。

Codasip同時還改進了 vanilla LLVM。通過添加針對性能提升(例如改進的跳轉線程、超級塊調度或循環折疊/扁平化)、代碼縮減(例如改進的-msave-restore、改進的多輸出指令支持或機器大綱器)或 DSP 功能(例如零開銷循環、雙堆棧架構支持或帶后增量/前增量的加載/存儲)的高級optimization pass。

此時我們了解一下生成的 C/C++ 編譯器在基準測試中的表現如何,并重點關注編譯器的兩個方面:性能和代碼量。

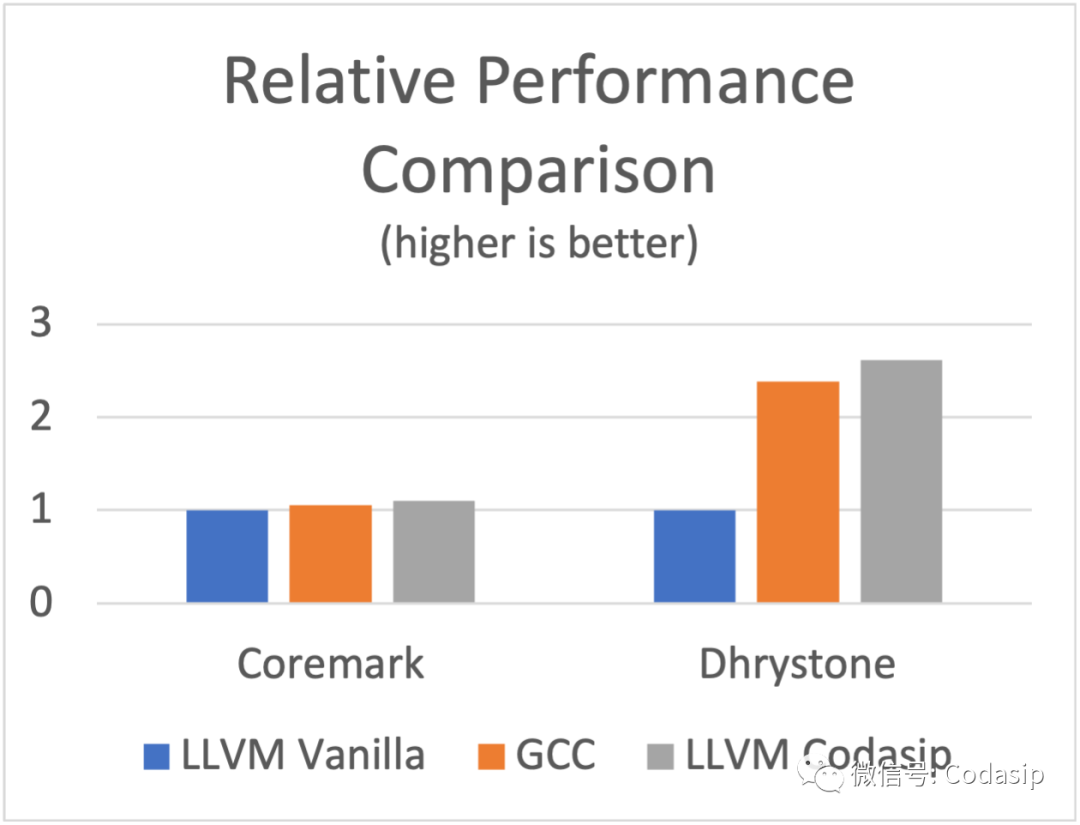

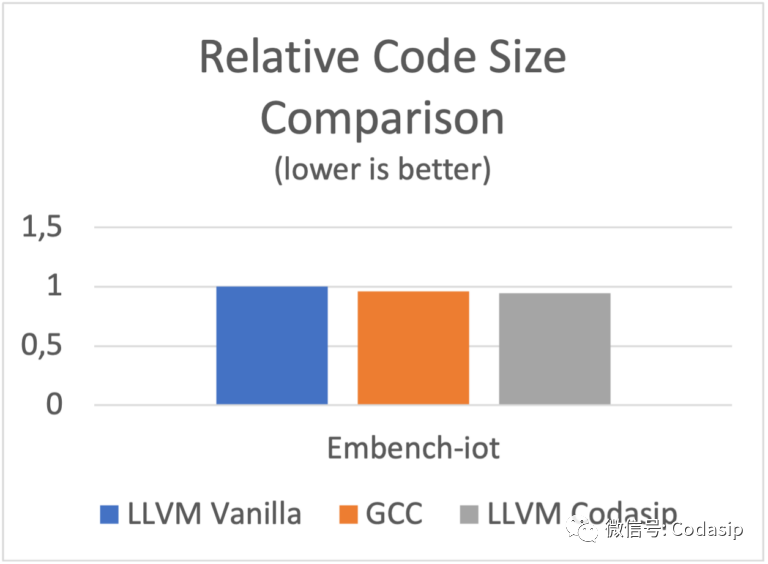

Coremark 和 Dhrystone 用于測量性能,Embench-iot 用于測量代碼大小。我們比較了三種編譯器: GCC、Vanilla LLVM 和 Codasip LLVM。比較是相對于其他編譯器進行的,Vanilla LLVM 是參考編譯器(即在圖表中得分 1)。RISC-V ISA 配置為 RV32IMCB。

測試性能結果

性能比較顯示了 Codasip LLVM 的改進,以及它如何優于其他編譯器。請注意,所有編譯器都使用了類似的優化標志。自定義指令可以明顯改善結果。

代碼大小結果

代碼大小比較也顯示了 Codasip LLVM 的優勢,盡管差距并不大。在此,自定義指令也能明顯改善結果。對于如何縮減RISC-V的代碼大小,大家可通過IP&SoC雜志7/8月版的電子書查閱Codasip的迷你技術白皮書,鏈接如下:https://ipsoc.yunzhan365.com/books/stka/mobile/index.html

創新自動化助理 RISC-V的飛速發展

RISC-V ISA 仍在不斷發展,行業急需一些方法來輕松探索不同指令及其對軟件的影響(包括性能、代碼大小或功耗等方面)。自動化是非常可取的,因為自動化流程可以快速高效地探索設計空間。或者說,如果設計人員想要創新或與眾不同,那么他們就需要能夠實現創新或與眾不同的工具和語言,協助其達到目的。

而Codasip Studio 正是實現這一目標的有效方法。Codasip的處理器設計自動化工具集能從單一的真實源自動生成所有需要的部件。生成的 LLVM C/C++ 編譯器可以自動使用新指令(也就是說,除非您愿意,否則無需更改 C/C++ 代碼)。此外它在性能和代碼大小方面的表現也非常出色。Codasip Studio 可以自動生成可執行模型、RTL 或驗證工具,以完善 IP 工具包,并在最終產品中部署創新的 RISC-V 架構。

審核編輯:彭菁

-

C++

+關注

關注

22文章

2108瀏覽量

73622 -

編譯器

+關注

關注

1文章

1623瀏覽量

49108 -

調試器

+關注

關注

1文章

303瀏覽量

23716 -

SDK

+關注

關注

3文章

1035瀏覽量

45902 -

RISC-V

+關注

關注

45文章

2270瀏覽量

46130

原文標題:編譯器重度愛好者有話說 - 針對 RISC-V 的可重定向 LLVM C/C++ 編譯器

文章出處:【微信號:Codasip 科達希普,微信公眾號:Codasip 科達希普】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

C++編譯器數值性能比較

主流的C語言編譯器詳細介紹

主流C語言編譯器的詳細資料介紹

什么是 LLVM C/C++ 編譯器?

什么是 LLVM C/C++ 編譯器?

評論