1.1 概述

ESD:Electro-Static discharge的簡稱,意思是“靜電釋放”。靜電是一種自然現象,通常通過接觸、摩擦、電器間感應等方式產生,其特點是長時間積聚、高電壓(可以產生幾千伏甚至上萬伏的靜電)、低電量、小電流和作用時間短的特點,常常造成電子電器產品運行不穩定,甚至損壞。

EMI:Electromagnetic Interference的簡稱,直譯是電磁干擾;在高速PCB及系統設計中,高頻信號線、集成電路的引腳、各類接插件等都可能成為具有天線特性的輻射干擾源,能發射電磁波并影響其他系統或本系統內其他子系統的正常工作。

EMC:Electro Magnetic Compatibility的簡稱,也稱電磁兼容,各種電氣或電子設備在電磁環境復雜的共同空間中,以規定的安全系數滿足設計要求的正常工作能力。

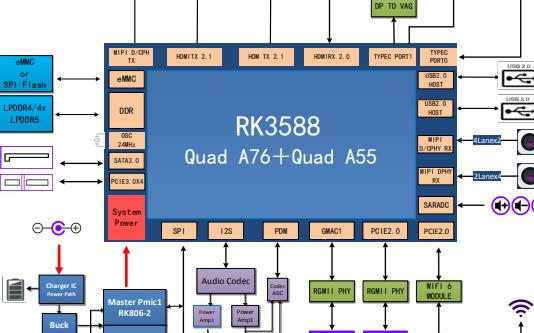

本章對于 RK3588產品設計中的 ESD/EMI防護設計及EMC的設計檢查給出了建議,幫助大家更好的提高產品的抗靜電、抗電磁干擾水平。

1.2 ESD防護設計

1、模具上做隔離:接插件能內縮的盡量內縮于殼體內,讓靜電釋放到內部電路上的距離變長,能量變弱,測試標準由接觸放電條件變為空氣放電等。

2、在PCB布局時做好敏感器件的保護、隔離,一些敏感模塊如射頻、音頻、存儲器可以添加屏蔽罩。

3、布局時盡量將RK3588芯片及核心部件放在PCB中間,不能放在PCB中間的,需要保證屏蔽罩離板邊至少2MM以上的距離,且要保證屏蔽罩能夠可靠接地。

4、應該按功能模塊及信號流向來布局PCB, 各個敏感部分相互獨立,對容易產生干擾的部分最好能 隔離,比如DCDC開關電源模塊等。

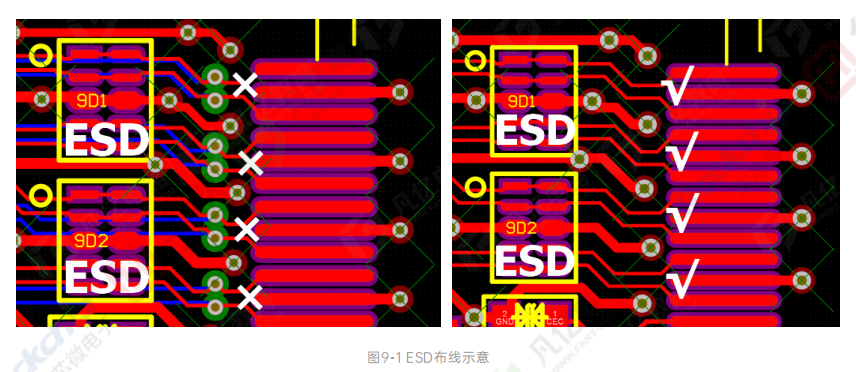

5、要求合理擺放應對ESD器件,一般要求擺在源頭,即ESD器件擺放在接口處或靜電釋放處,走線時先經過靜電器件之后再打孔引出,如圖9-1所示。

6、元件布局遠離板邊且距插接件有一定距離,一般建議布局板邊至少20mil,接插件40mil以上。

7、PCB表面一定要有良好的GND回路,各接插件在表層都要有較好的GND連接回路。有加屏蔽罩的應盡量跟表層地相連,并在屏蔽罩焊接處多打地孔接地。要做到這一點,就要求各個連接座部分在表層不要走線,也不要出現大范圍切斷表層銅皮的走線。

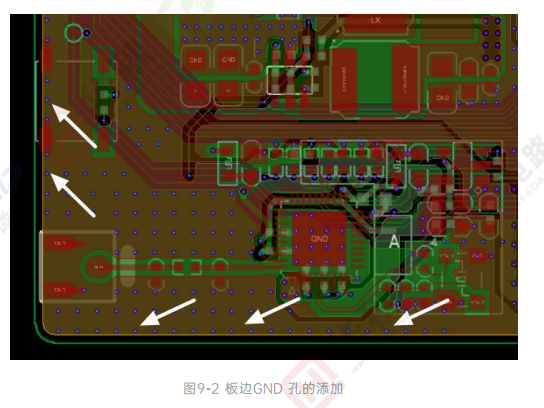

8、表層板邊不走線且多打地孔,必要時要做好信號跟地之間的隔離,如圖9-2所示。

9、如果有經連接器實現板對板連接時,建議全部信號串接一定阻值的電阻(2.2ohm-10ohm之間,具體以能滿足SI測試為準),以及預留TVS器件,可提升抗靜電浪涌能力。

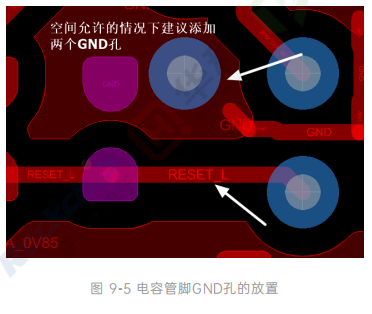

10、RK3588 nPOR管腳的100nF電容必須靠近管腳放一個8/16mil的地過孔,空間允許建議打兩個以上,更良好的接地。

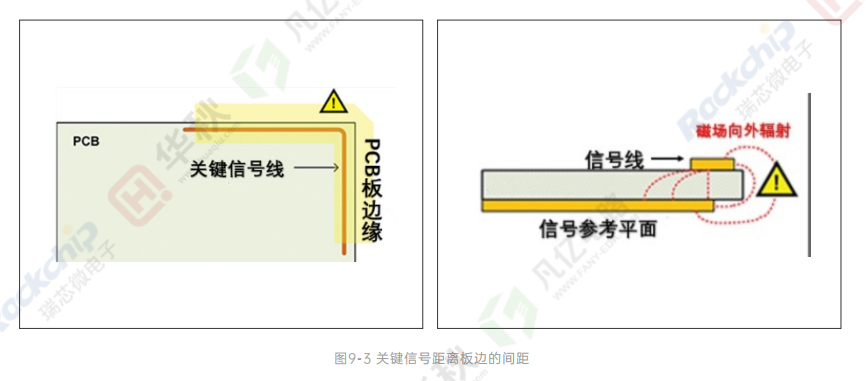

11、關鍵信號比如Reset、時鐘、中斷等敏感信號與板邊距離不得小于5mm,走線下方需要有參考平面,避免出現邊緣效應,如圖9-3所示。

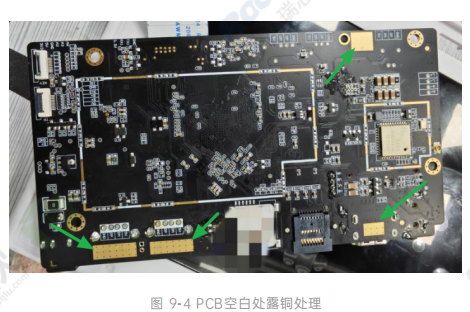

12、在PCB板空白多露銅,以便加強靜電釋放效果,或者便于增加加泡棉等補救措施,如圖9-4所示。

13、其它外圍芯片如果有帶Reset管腳,建議增加100nF電容必須靠近管腳,電容的地焊盤必須有一個8/16mil地過孔,空間允許建議打兩個以上,更良好的接地,如圖9-5所示。

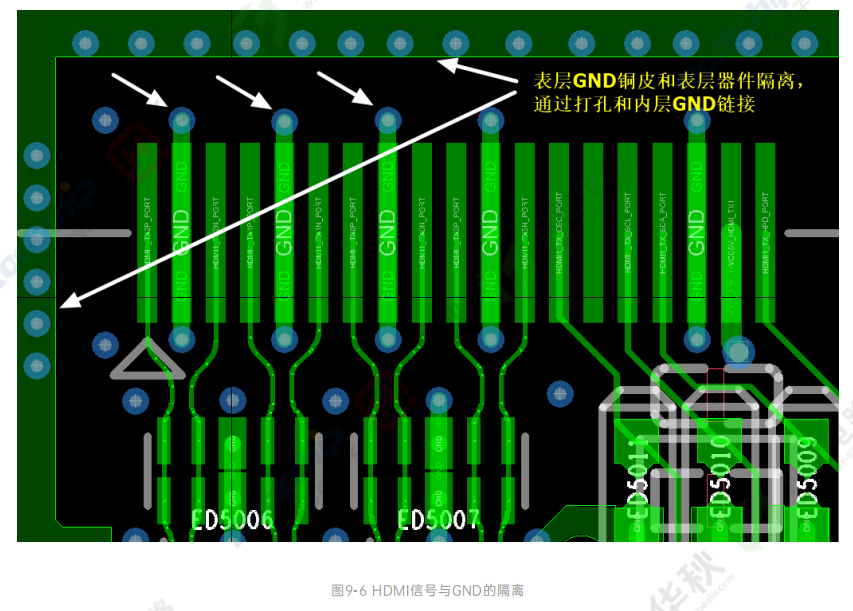

14、從PCB上進行隔離,讓靜電只能釋放在部分區域,比如座子地管腳單獨過孔和內層的地層連接,對表層的PCB進行Keepout,表層的地銅皮和管腳盡量遠離,即讓敏感信號遠離靜電易放電區域(表層地銅皮)等等,如圖9-6所示,在表層隔離HDMI信號與GND的距離。

1.3 EMI防護設計

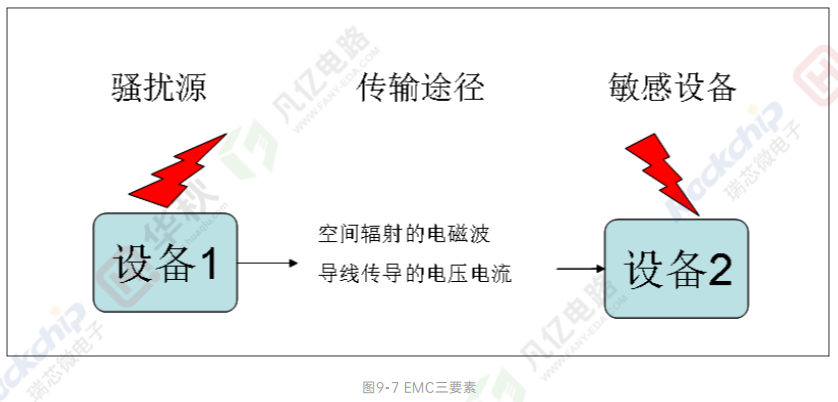

1、電磁干擾三要素:干擾源、耦合通道及敏感設備,如圖9-7所示,我們不能處理敏感設備,所以處理EMI就只能從干擾源跟耦合通道入手。解決EMI問題,最好的方式就是消除干擾源,消除不了的就想辦法切斷耦合通道或者避免天線效應;

2、PCB上干擾源一般很難完全消除,可以通過濾波、接地、平衡、阻抗控制,改善信號質量(如端 接)等方法來應對。各種方法一般會綜合運用,但良好的接地是最基本的要求。

3、常用應對EMI材料有屏蔽罩、專用濾波器、電阻、電容、電感、磁珠、共模電感/磁環、吸波材料、展頻器件等。

4、濾波器選擇原則:若負載(接收器)為高阻抗(一般的單端信號接口都是高阻抗,比如SDIO、RBG、CIF等),則選擇容性濾波器件并入線路;若負載(接收器)為低阻抗(比如電源輸出接口),則選擇感性濾波器件串入線路。使用濾波器件后不能使信號質量超出其SI許可范圍。差分接口一般使用共模電感來抑制EMI。

5、PCB上屏蔽措施需良好接地,不然可能會引起輻射泄露或者屏蔽措施形成了天線效應,連接器的屏蔽需符合相關技術標準。

6、RK3588展頻的能分模塊使用。展頻的程度需根據相關部分對信號的要求而定。具體措施見RK3588展頻說明。

7、所有時鐘串接的匹配電阻,建議保留,提供匹配阻抗,提高信號質量的改善措施。

8、DC電源輸入處,有條件可預留電源共模電感或EMI濾波器。

9、USB、HDMI、VGA、屏連接座等接口處增加預留共模電感或濾波電路。

10、有加散熱器時,要注意散熱器也有可能耦合EMI能量,產生輻射,在選用散熱器時除了滿足熱設計要求,還應滿足EMI測試要求。散熱器要預留接地條件,當有需要接地時,將散熱器接地,此處不好明確接地點個數及怎么選擇接地點,需要第一個版本硬件在實驗室實際測試時依據實際情況整改。

11、EMI跟ESD對LAYOUT的要求有高度一致性,前述ESD的LAYOUT要求,大部分適用于EMI防護。另外增加下面的要求:

A、盡量保證信號完整性。

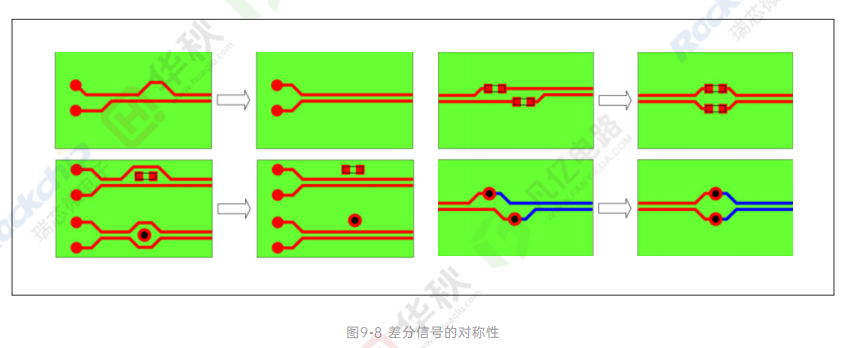

B、差分線要做好等長及緊密耦合,保證差分信號的對稱性,以盡量減少差分信號的錯位,避免轉化成引起EMI問題的共模信號,如圖9-8所示。

C、有插件器件等帶金屬殼器件的元件,應避免耦合干擾信號從而輻射。也要避免器件的干擾信號從殼體耦合到其他信號線。

D、所有時鐘串接的匹配電阻靠近CPU端(源端),CPU管腳和電阻之間走線必須控制在400mil以內。

E、如果PCB超過4層板,建議讓所有時鐘信號盡量走內層。

F、防止電源輻射,電源層覆銅必須內縮,以一個H(電源和地之間的介質厚度)為單位,建議內縮20H,我們要求地平面大于電源或信號層,這樣有利于防止對外輻射干擾和屏蔽外界對自身的干擾,(一般情況下在PCB設計的時候把電源層比地層內縮1mm即可,不然嚴格去滿足20H的話會導致PCB走線不方便,如圖9-9所示。)

1.4 EMC設計檢查建議

按照設計流程,一個產品Layout完成之后,需要進入嚴格的評審環節,所設計的產品是否滿足ESD或者EMI防護設計要求,撇開原理圖設計,PCB設計一般需要我們從PCB布局和PCB布線兩個方面進行審查,本小節就這兩方面的檢查做了建議,讀者可以此作為審核PCB Layout人員的PCB的參考標準。

EMC設計布局檢查建議:

1、整體布局檢查建議

② 高速、中速、低速電路要分開。

③ 強電流、高電壓、強輻射元器件遠離弱電流、低電壓、敏感元器件。

④ 多層板設計,必須要有單獨的電源平面和地平面。

⑤ 對熱敏感的元件(含液態介質電容、晶振)盡量遠離大功率的元器件、散熱器等熱源。

2、接口與保護布局檢查建議

① 一般電源防雷保護器件的順序是:壓敏電阻→保險絲→抑制二極管→EMI濾波器→電感或者共模電感,對于原理圖缺失上面任一器件進行順延布局。

② 一般對接口信號的保護器件的順序是:ESD(TVS管)→隔離變壓器→共模電感→電容→電阻,對于原理圖缺失上面任一器件進行順延布局。

③ 電平變換芯片(如RS232)要靠近連接器的位置(如串口)放置。

④ 易受ESD干擾的器件,如NMOS、CMOS器件等,要盡量遠離易受ESD干擾的區域(如單板的邊緣區域)。

3、時鐘電路布局檢查建議

① 時鐘電路的濾波器(盡量采用“∏”型濾波)要靠近時鐘電路的電源輸入管腳。

② 晶體、晶振和時鐘分配器的布局要注意遠離大功率的元器件、散熱器等發熱的器件。

③ 晶體、晶振和時鐘分配器與相關的IC器件要盡量靠近。

④ 晶振距離板邊和接口器件要大于1inch的距離。

4、開關電源布局檢查建議

① 開關電源要遠離ADDA轉換器、模擬器件、敏感器件、時鐘器件。

② 嚴格按照原理圖的要求進行布局,不要將開關電源的電容隨意放置。

③ 開關電源布局要緊湊,輸入輸出要分開。

5、電容與濾波器件布局檢查建議

① 原則上每個電源管腳放置一個0.1uf的小電容、一個集成電路放置一個或多個10uf大電容,可以根據具體情況進行增減。

② 電容務必要靠近電源管腳放置,而且容值越小的電容要越靠近電源管腳。

③ EMI濾波器要靠近芯片電源的輸入口。

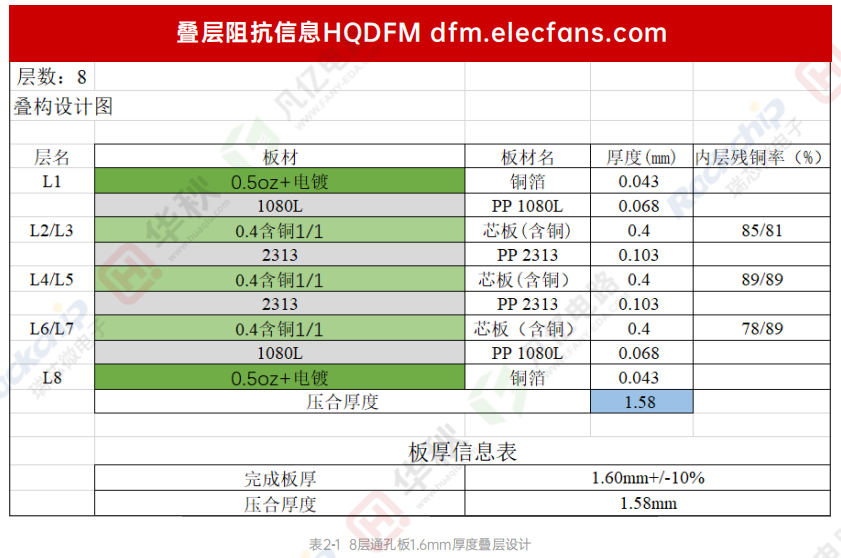

6、疊層檢查建議

① 多層板(四層以上)至少有一個連續完整的地平面用來控制PCB的阻抗和信號質量。

② 電源平面和地平面靠近放置。

③ 疊層盡量避免兩個信號層相鄰,如果相鄰加大兩個信號層的間距,并且布線時應該錯位布線,不能重疊布線,否側后期布線可能會引起串擾的產生。

④ 避免兩個電源平面相鄰,特別是由于信號層鋪電源而導致的電源平面相鄰。

⑤ 外層鋪地。

7、其他設計檢查建議

① 整機設計為浮地設備時,建議各接口不要分地設計。

② 機器外殼為金屬時,電源是三孔,要求金屬外殼必須良好連接大地。

1.5 EMC設計布線檢查建議

1、整體布線檢查建議

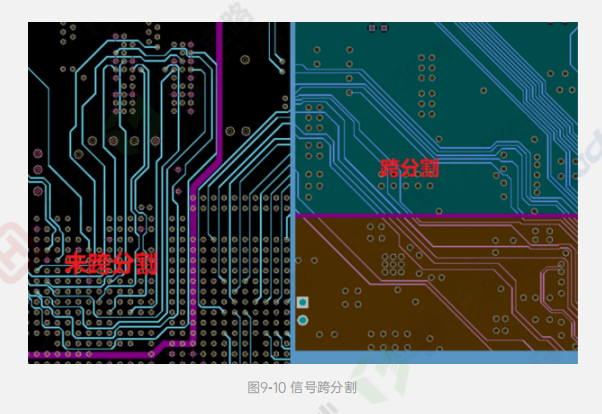

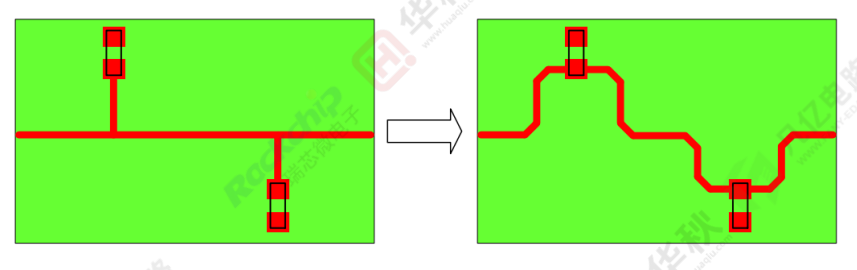

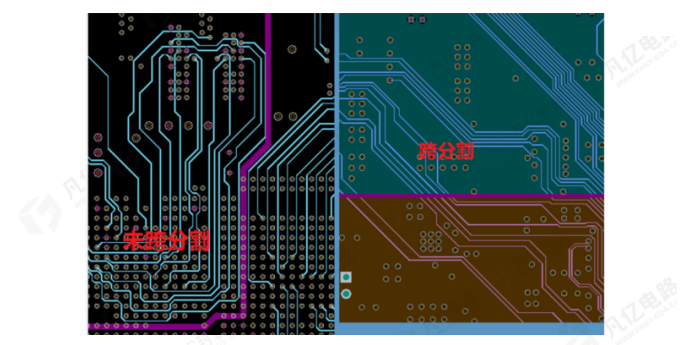

① 關鍵信號線走線避免跨分割我們PCB中的信號都是阻抗線,是有參考的平面層,對于設計的關鍵信號避免跨分割的現象出現,否則會導致信號阻抗的突變,導致信號完整性問題的出現。如圖9-10,描述了信號跨分割的現象。

② 相同功能的總線要并行走、中間不要夾叉其它信號,如果空間允許可以進行包地處理。

③ 關鍵信號線走線避免“U”型或“O”型。

④ 關鍵信號線走線不要人為的繞長(以最短路徑進行走線)。

⑤ 關鍵信號線需要距離邊沿和接口400mil以上。

⑥ 晶振下面所有層都不能走線。

⑦ 開關電源下面不能走線,特別是電感或轉換芯片下方。

⑧ 接收和發送信號要分開走,不能互相交叉布線。

2、隔離與保護

① 浪涌抑制器件(TVS管、壓敏電阻)對應的信號走線盡量表層,短且粗(一般10mil以上)。

② 不同接口之間的走線要清晰,不要互相交叉布線。

③ 接口線到所連接的保護和濾波器件布線要盡量短。

④ 接口線必需要先經過保護或濾波器件再到信號接收芯片。

⑤ 接口器件的固定孔要接到保護地上,連接到機殼的定位孔、扳手要直接接到信號地。

⑥ 變壓器、光耦等器件的輸入輸出地要分開處理(兩端使用不同的GND)。

3、時鐘布線

① 超過1inch的時鐘線盡量走在內層,時鐘線采用立體包地處理。

② 時鐘線換層為不同的地參考平面需要增加回流地過孔。

③ 時鐘線不允許跨分割。

④ 時鐘線與其它信號線的間距達到5W,空間允許的情況下可以進行包地處理。

⑤ 時鐘電路的電源走線需要加寬或鋪銅處理。

4、其他

① 保護地和信號地之間的間距大于80mil。

② DC48V的爬電間距是否為80mil以上。

③ 電源平面要比地平面內縮“20H”(H為電源和地平面的距離),一般情況地內縮20mil,電源需要內縮60mil,并間隔150mil打地過孔。

④ 布線要避免出線Stub線,Stub線就是俗稱的線頭或歪線, 或者說信號沒打算經過的路徑。

⑤ AC220V的爬電間距最少為300mil,具體可以查爬電間距規格表。

⑥ 差分走線可以抑制共模干擾。

⑦ 敏感的信號線必須采用包地處理,包地線每隔200mil增加一個GND孔。

審核編輯:湯梓紅

-

ESD

+關注

關注

49文章

2268瀏覽量

175223 -

emi

+關注

關注

53文章

3726瀏覽量

130396 -

emc

+關注

關注

172文章

4124瀏覽量

186081 -

電磁干擾

+關注

關注

36文章

2381瀏覽量

106329 -

RK3588

+關注

關注

7文章

406瀏覽量

5616

原文標題:RK3588 ESD/EMI防護設計及EMC設計檢查建議(附白皮書下載)

文章出處:【微信號:發燒友研習社,微信公眾號:發燒友研習社】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

瑞芯微RK3588開發板RK3588 EVB和RK3588S EVB解讀

RK3588 PCB推薦疊層及阻抗設計

評論