1.概述

信號完整性(Signal Integrity,SI)是指電路系統中信號的質量,如果在要求的時間內,信號能不失真地從源端傳輸到接收端,我們就稱該信號是完整的。信號完整性分析的目的就是用最小的成本,最快的時間使產品達到波形完整性、時序完整性、電源完整性的要求。

2.典型的信號完整性問題

信號具有良好的信號完整性是指當在需要的時候,具有所必需達到的電壓電平數值,差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同引起的。主要的信號完整性問題包括反射、振蕩、地彈、串擾、時序等。其中反射和串擾是引發信號完整性問題的兩大主要因素。

2.1 反射

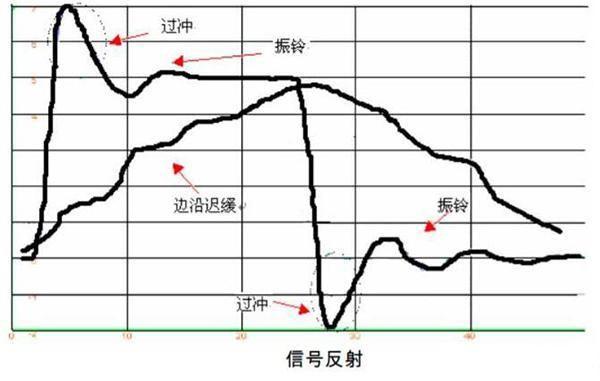

反射是指信號在傳輸線上的回波現象,由于傳輸系統阻抗不匹配,會使傳輸的信號不能被完全吸收,造成部分能量返回。反射造成信號出現過沖(Overshoot)、振鈴(Ringing)、邊沿遲緩(階梯電壓波)。過沖是振鈴的欠阻尼狀態,邊沿遲緩是振鈴的過阻尼狀態。下圖為信號反射的三種表現形式。

過沖一方面會造成強烈的電磁干擾,另一方面會損傷后面電路的輸入級,甚至失效。而振鈴會帶來信號長時間不能穩定,邊沿遲緩帶來信號上升時間過長,二者都可能帶來信號的時序問題,如時鐘數據同步、建立與保持時間不滿足等。

2.2串擾

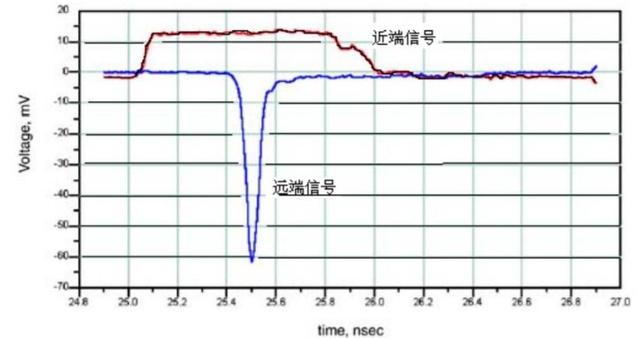

由于導線之間間距過小,當有快速變化的電流流過導線時會產生交變的磁場,而使鄰近的導線上感應出信號電壓,稱為串擾(Crosstalk)。下圖為受影響信號線上的串擾信號。

串擾干擾著正常的信號流,有可能造成數據錯誤,是造成誤碼的主要原因之一。PCB板層的參數、信號線間距、驅動端和接收端的電氣特性及信號線的端接方式對串擾都有一定影響。

3.信號完整性產生原因

- 信號上升沿變陡,帶寬高,也就是包含的頻率多,所以易出現反射,串擾等。

- 芯片工作電壓低,導致信號受干擾翻轉。

- 電路板集成度高,串擾影響嚴重。

常見的信號完整性問題引起問題的原因和相應的解決方法:

4.信號完整性設計的難點

SI設計的主要難點在于需要綜合信號幅度、噪聲、邊沿、延時等影響信號質量的多種因素,并且這種因素常常相互依賴,互相影響,交叉在一起,這就導致抑制了某一方面的影響可能又導致其他方面的影響惡化,因此SI設計中往往需要對各種因素反復權衡,做出系統化的綜合設計。

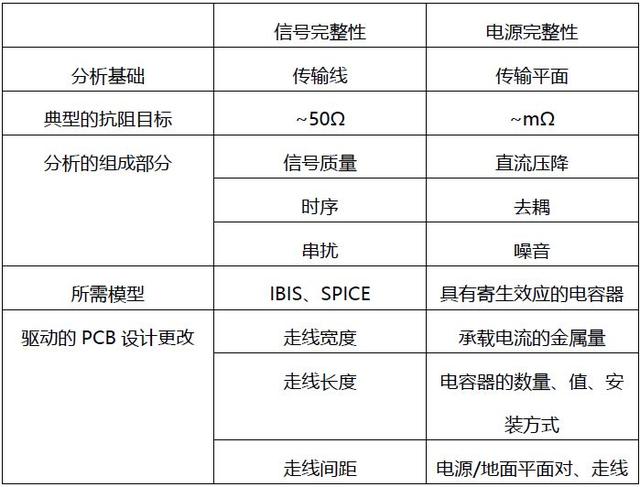

5.信號完整性和電源完整性之間的差異

在信號完整性中,重點是確保傳輸的邏輯1在接收器中看起來就像 1(對0同樣如此)。在電源完整性中,重點是確保為驅動器和接收器提供足夠的電流以發送和接收1和0。因此,電源完整性可能會被認為是信號完整性的一個組成部分。實際上,它們都是關于數字電路正確模擬操作的分析。

-

驅動器

+關注

關注

54文章

8438瀏覽量

148079 -

PCB板

+關注

關注

27文章

1459瀏覽量

52573 -

接收器

+關注

關注

14文章

2503瀏覽量

72805 -

信號完整性

+關注

關注

68文章

1423瀏覽量

96033 -

電源完整性

+關注

關注

9文章

213瀏覽量

20953

發布評論請先 登錄

相關推薦

什么是信號完整性

聽懂什么是信號完整性

評論