GIC硬件原理

- ARM公司提供了一個通用的中斷控制器

GIC(Generic Interrupt Controller),GIC的版本包括V1 ~ V4,由于本人使用的SoC中的中斷控制器是V2版本,本文將圍繞GIC-V2來展開介紹;

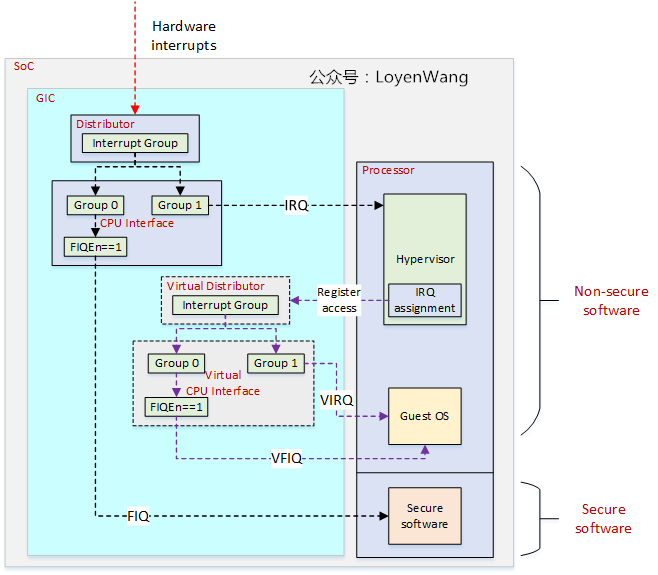

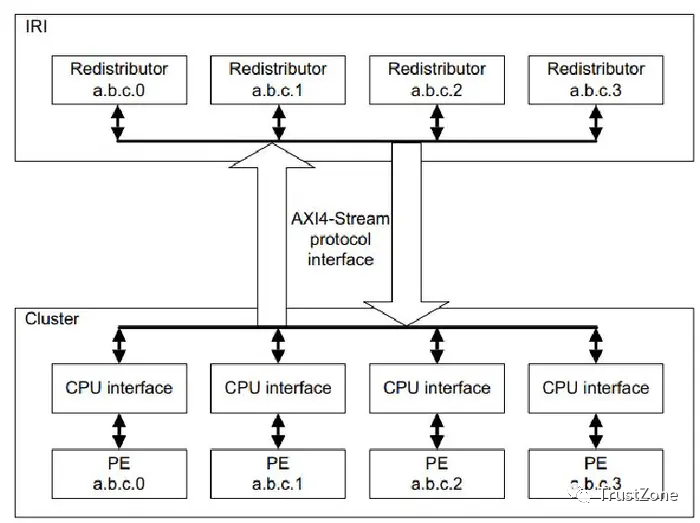

來一張功能版的框圖:

GIC-V2從功能上說,除了常用的中斷使能、中斷屏蔽、優先級管理等功能外,還支持安全擴展、虛擬化等;GIC-V2從組成上說,主要分為Distributor和CPU Interface兩個模塊,Distributor主要負責中斷源的管理,包括優先級的處理,屏蔽、搶占等,并將最高優先級的中斷分發給CPU Interface,CPU Interface主要用于連接處理器,與處理器進行交互;Virtual Distributor和Virtual CPU Interface都與虛擬化相關,本文不深入分析;

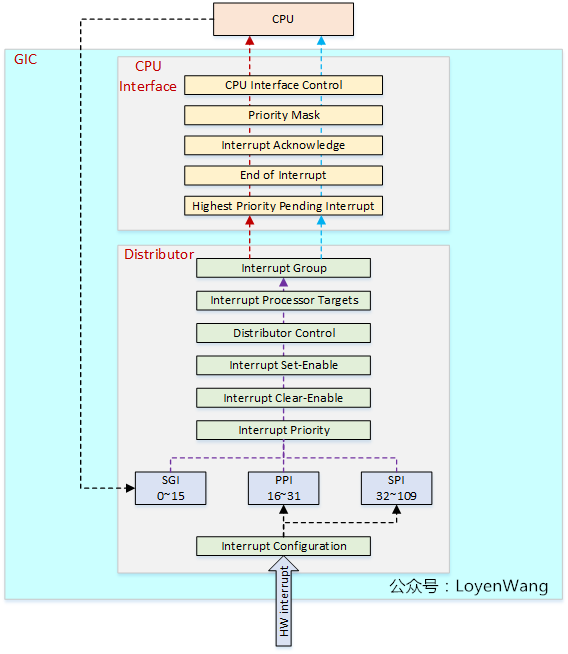

再來一張細節圖看看Distributor和CPU Interface的功能:

GIC-V2支持三種類型的中斷:SGI(software-generated interrupts):軟件產生的中斷,主要用于核間交互,內核中的IPI:inter-processor interrupts就是基于SGI,中斷號ID0 - ID15用于SGI;PPI(Private Peripheral Interrupt):私有外設中斷,每個CPU都有自己的私有中斷,典型的應用有local timer,中斷號ID16 - ID31用于PPI;SPI(Shared Peripheral Interrupt):共享外設中斷,中斷產生后,可以分發到某一個CPU上,中斷號ID32 - ID1019用于SPI,ID1020 - ID1023保留用于特殊用途;

Distributor功能:- 全局開關控制

Distributor分發到CPU Interface; - 打開或關閉每個中斷;

- 設置每個中斷的優先級;

- 設置每個中斷將路由的CPU列表;

- 設置每個外設中斷的觸發方式:電平觸發、邊緣觸發;

- 設置每個中斷的Group:Group0或Group1,其中Group0用于安全中斷,支持FIQ和IRQ,Group1用于非安全中斷,只支持IRQ;

- 將

SGI中斷分發到目標CPU上; - 每個中斷的狀態可見;

- 提供軟件機制來設置和清除外設中斷的pending狀態;

- 全局開關控制

CPU Interface功能:- 使能中斷請求信號到CPU上;

- 中斷的確認;

- 標識中斷處理的完成;

- 為處理器設置中斷優先級掩碼;

- 設置處理器的中斷搶占策略;

- 確定處理器的最高優先級pending中斷;

中斷處理的狀態機如下圖:

Inactive:無中斷狀態;Pending:硬件或軟件觸發了中斷,但尚未傳遞到目標CPU,在電平觸發模式下,產生中斷的同時保持pending狀態;Active:發生了中斷并將其傳遞給目標CPU,并且目標CPU可以處理該中斷;Active and pending:發生了中斷并將其傳遞給目標CPU,同時發生了相同的中斷并且該中斷正在等待處理;

GIC檢測中斷流程如下:

- GIC捕獲中斷信號,中斷信號assert,標記為pending狀態;

Distributor確定好目標CPU后,將中斷信號發送到目標CPU上,同時,對于每個CPU,Distributor會從pending信號中選擇最高優先級中斷發送至CPU Interface;CPU Interface來決定是否將中斷信號發送至目標CPU;- CPU完成中斷處理后,發送一個完成信號

EOI(End of Interrupt)給GIC;

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

嵌入式

+關注

關注

5082文章

19110瀏覽量

304841 -

Linux

+關注

關注

87文章

11295瀏覽量

209348 -

子系統

+關注

關注

0文章

109瀏覽量

12392 -

gic

+關注

關注

0文章

14瀏覽量

6270 -

控制器

+關注

關注

0文章

24瀏覽量

3274

發布評論請先 登錄

相關推薦

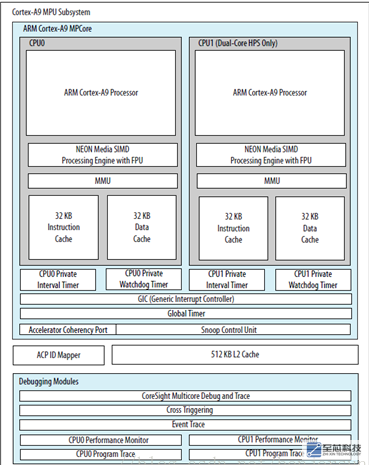

英特爾Altera系列cyclone V HPS GIC

大家好,又到了每日學習的時間了,今天我們來聊一聊英特爾 Altera系列 cyclone V HPS GIC. 一、CYCLONE V GIC配置 Cyclone v使用雙核ARM CORTEX

ARM之中斷GIC分析

1.“站的高尿的遠” GIC為中斷控制器,不要和ARM core的中斷搞混了,這些中斷都是連接到ARM core的IRQ或者FIQ上的。 要了解arm中斷系統,GIC絕對不容錯過,好先付

發表于 11-26 13:50

ARM GIC(一)之ARM soc中斷的處理介紹

的橋接器件,就是arm公司推出大名鼎鼎的gic,general interrupt controller。gic其實是一個架構,版本歷經了gicv1(已棄用),gicv2,gicv3,gicv4。對于

發表于 04-06 10:12

ARM GIC(二)之中斷術語的定義

ARM在GIC中,對于中斷,定義了如下的一些術語。一、中斷狀態對于每一個中斷而言,有以下4個狀態:?inactive:中斷處于無效狀態?pending:中斷處于有效狀態,但是cpu沒有響應該中斷

發表于 04-06 10:15

GIC ITS的ITS tables和Command Queue訪問簡析

ACE-Lite轉換為了AXI interface,因而這個系統設計不能實現GIC ITS和CPU的硬件一致性。在這樣的系統上運行Linux GICv3 driver可能會出現一致性問題:因為

發表于 12-20 14:35

小電阻器對治理電網GIC的效果分析

地磁感應電流(geomagnetically induced currents,GIC)引起變壓器半波飽和對電力系統的安全運行產生不利影響,甚至引發大面積停電事故。為了有效治理GIC對大規模電力系統

發表于 01-04 17:03

?7次下載

應用K值算法的甘肅電網GIC-Q擾動計算

的安全運行。以甘肅750 kV電網和330 kV電網GIC的計算數據為基礎,基于變壓器GIC無功(GIC-Q)損耗系數K值算法,計算了750 kV和330 kV變壓器的GIC無功損耗增

發表于 01-31 14:57

?3次下載

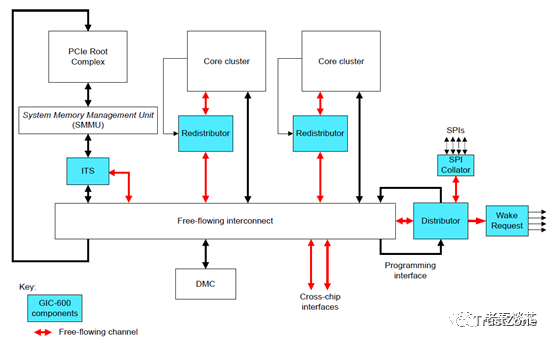

扒一扒GIC-600的相關知識

為了適應大規模的SoC設計,GIC-600被設計成分布式IP。所謂分布式,GIC-600由幾種組件構成,每個組件可以跟其它相關模塊在物理設計上擺放在一起,并與其擁有共同的電源域

發表于 02-06 11:36

?2733次閱讀

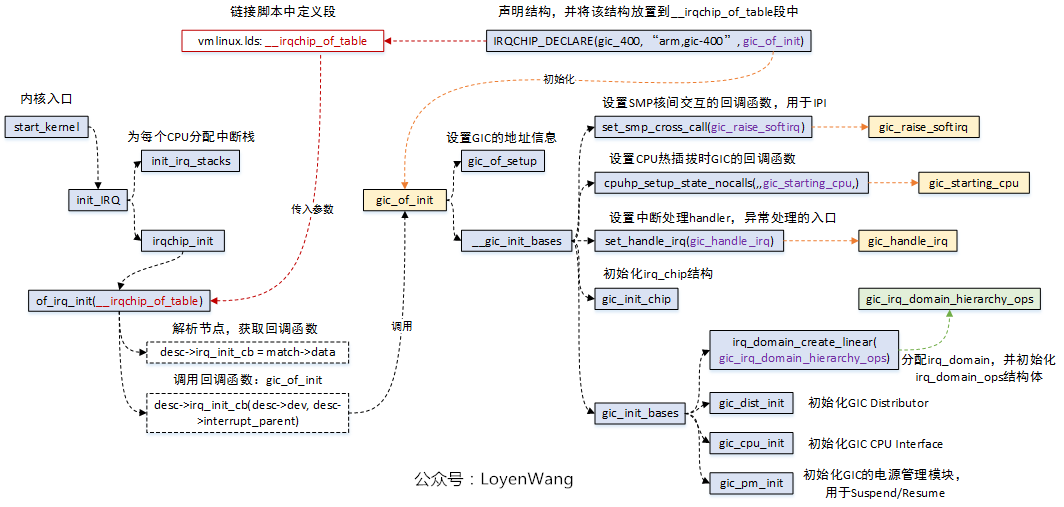

GIC驅動的執行流程是什么

驅動流程分析 GIC驅動的執行流程如下圖所示: 首先需要了解一下鏈接腳本 vmlinux.lds ,腳本中定義了一個 __irqchip_of_table 段,該段用于存放中斷控制器信息,用于最終來

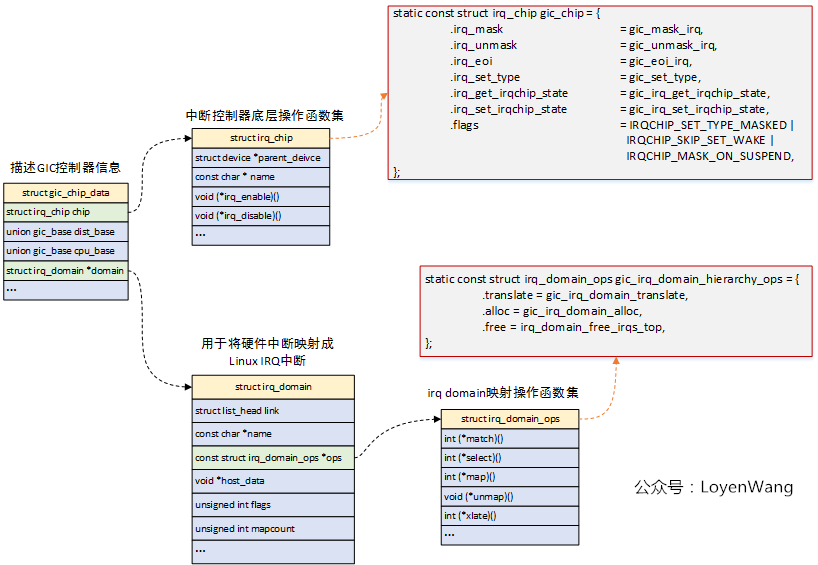

Linux GIC驅動數據結構分析

數據結構分析 先來張圖: GIC驅動中,使用 struct gic_chip_data 結構體來描述GIC控制器的信息,整個驅動都是圍繞著該結構體的初始化,驅動中將函數指針都初始化好,實際的工作

GIC-600的組件是如何連接的

為了適應大規模的SoC設計,GIC-600被設計成分布式IP。 所謂分布式,GIC-600由幾種組件構成,每個組件可以跟其它相關模塊在物理設計上擺放在一起,并與其擁有共同的電源域;組件之間通過片上網

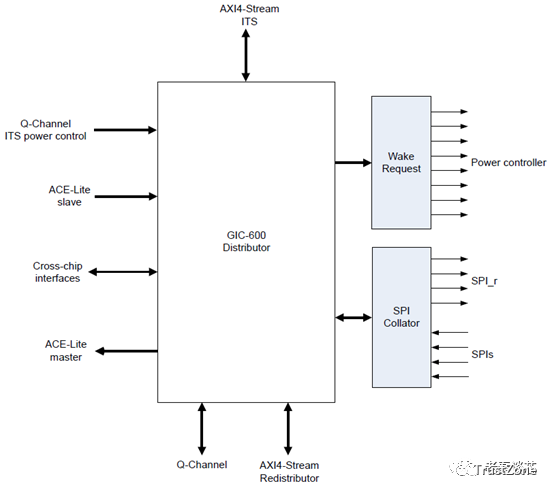

GIC-600的內部結構組件

接下來看看每個組件。 ? 首先是distributor,一個SoC只有一個。 ?它的組件只能與distributor通信。所以,可以看出,distributor是GIC-600中的核心,其作用是收集

gic和ARM Core的連接

? ?nVIRQ: 虛擬普通中斷 ? ?nVFIQ: 虛擬快速中斷 (2)gicv3和ARM Core的連接 gicv3 AXI-stream協議 ? ?gic stream協議,是基于AXI-stream協議

GIC是什么意思 GIC硬件原理

GIC是什么意思 GIC硬件原理

評論