點擊上方藍字關注我們

目前,在數據采集系統的硬件設計方案中,有采用通用單片機和USB相結合的方案,也有采用DSP和USB相結合的方案,前者雖然硬件成本低,但是時鐘頻率較低,難以滿足數據采集系統對速度要求;后者雖然可以實現高速傳輸,但DSP價格過于昂貴。而利用FPGA和USB接口芯片結合的方案,具有功耗低、時鐘頻率高、速度快、效率高、組合形式靈活等特點,是單片機和DSP所無法比擬的。

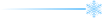

系統總體方案

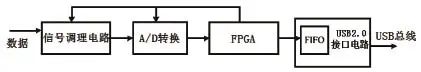

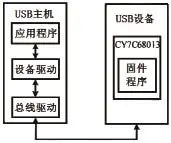

根據本系統要實現的功能,該系統硬件部分采用“信號調理電路+A/D轉換電路+FPGA+USB 2.0接口芯片”的模式加以設計。系統采用可編程邏輯器件FPGA控制信號調理電路的工作,同時控制A/D轉換器采樣,這樣通過硬件描述語言來描述可以使硬件設計如同軟件一樣靈活,并且FPGA可重復編程的特性提高了工作效率和設計的靈活性。另外系統所需的高速緩存FIFO是由USB 2.0接口芯片的片內資源來實現的,這樣做可以降低系統成本、提高系統可靠性。USB 2.0接口芯片的固件程序由集成在芯片內的增強型8051單片機進行控制,固件程序存放在主機上,在系統上電后通過上位機驅動程序下載到芯片內部的RAM內。系統的總體方案如圖1所示。

圖1 數據采集系統結構圖

整個硬件電路的工作流程是:當上位機發來數據采集請求,FPGA就開始啟動對信號調理模塊和A/D采樣控制模塊的控制。經過A/D轉換后的數據按照一定的時序發送到USB 2.0接口芯片的端口FIFO里面,然后再把數據通過USB總線傳輸給上位機。

系統硬件設計與實現

本數據采集系統的硬件設計主要是基于USB 2.0的硬件數據采集卡的設計。此采集卡的作用是首先用A/D轉換器對輸入的電路實驗數據進行采樣量化,然后將采樣得到的數據通過USB 2.0總線傳送到上位機,以便進行后續處理。

主控芯片簡介

Altera公司的Cyclone II FPGA是基于Stratix II的90nm工藝推出的低成本FPGA,由于增加了DSP硬件塊,在芯片總體性能上要優于Cyclone系列器件,而在成本上卻仍維持Cyclone系列低成本的優點。本設計選用了Cyclone II系列中的EP2C5Q208芯片,其邏輯單元有4608個,M4K RAM有26個,鎖相環有2個、乘法器模塊有13個,最大用戶可用I/O引腳為142個,可以滿足本設計的需要。圖2為EP2C5Q208的外圍連接電路框圖。

圖2 主控芯片連接框圖

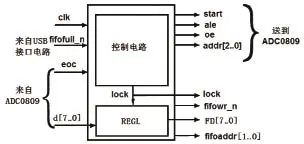

設計電源電路之前,首先對系統中各器件所需電源的需求情況進行分析,電源電路需要提供5種直流電壓才能滿足系統對電源的需求:FPGA的供電電壓是3.3V和1.2V;信號調理電路電壓為+12V和-12V;A/D轉換器ADC0809所需要的電壓為5V;USB 2.0接口芯片CY7C68013需要3.3V供電。而系統只有USB總線能提供+5V電壓,因此需使用開關電源進行電壓轉換。電壓轉換電路如圖3所示。

圖3 電源電路

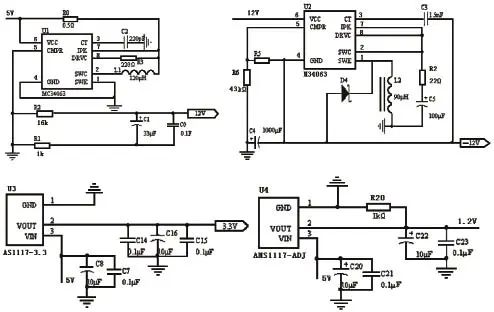

信號調理電路

信號調理電路的作用是對微弱的輸入信號進行適當的調理,使其電壓范圍在0~5V之間,從而滿足A/D轉換芯片的輸入電壓的要求。本調理電路中采用了運算放大器芯片AD827。該芯片最高帶寬為50MHz,芯片內部集成2片運放,分別用來進行信號的放大平移和衰減。信號調理電路如圖4所示。

圖4 信號調理電路

圖中左半部分為第一個環節,這個環節輸入電壓V1,輸出電壓為V2,對于微弱的輸入信號,可以經過調理達到正常電平范圍之內。右半部分為第二個環節,這個環節是信號的衰減環節,若第一個環節得到的電壓幅值較大,超過了0~5V的電壓范圍,則可以將此信號在第二個環節進行衰減。第二個環節的最大增益為1,通過調節電位器,可以使信號最小衰減為0。這樣,信號經過信號調理電路之后,就可以滿足A/D采樣的要求了。

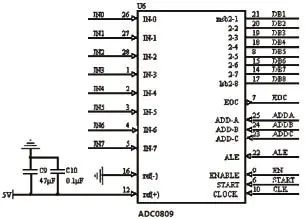

A/D采樣電路

經過調理后的模擬信號需要經A/D轉換芯片進行采樣、量化、編碼,然后將編碼后的數據經過USB 2.0接口芯片傳送至USB主機,A/D采樣電路是整個數據采集電路的關鍵部分。本設計所使用的A/D采樣芯片是ADC0809轉換芯片,它是通過采樣逐次逼近的方法完成A/D轉換的。ADC0809由單一+5V電源供電,片內帶有鎖存功能的8路模擬多路開關,可以對8路0~5V的模擬信號分時進行轉換。A/D轉化器電路的連接如圖5所示,其中,參考電壓VREF+接+5V,VREF-接地,輸入模擬電壓范圍為0~5V。

圖5 A/D采樣電路

圖6 從屬FIFO模式連接框圖

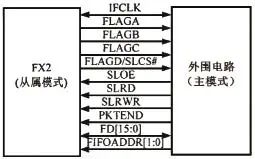

USB 2.0接口電路

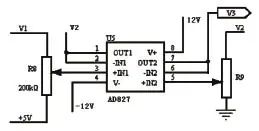

Cypress公司的EZ-USB FX2系列芯片是世界上第一個集成了USB 2.0協議的微處理器,它支持12Mb/s的全速傳輸和480Mb/s的高速傳輸,可使用4種USB傳輸方式。本系統采用EZ-USB FX2系列中CY7C68013-56PVC芯片。該芯片集成了USB 2.0收發器、串行接口引擎SIE(Serial Interface Engine)、8.5KB的RAM、4KB的FIFO存儲器、I/O口、通用可編程接口GPIF(General Programmable Interface)。

由于在EZ-USB FX2的內部嵌入了增強型的8051,所以一般的數據傳輸都可以通過8051來控制實現,但是因為8051本身的工作頻率較低,限制了與外圍電路之間的數據傳輸速度的進一步提高。雖然這種限制在12Mb/s的全速模式下不是很明顯,但是當數據傳輸速度提升到高速時,8051將成為系統的帶寬瓶頸。為此,本設計選擇采用了從屬FIFO接口模式進行傳輸,這樣8051就不會參與數據的傳輸,但它可以通過FIFO或RAM的方式訪問所傳輸的數據。由于篇幅限制,在此只給出其連接框圖。

系統軟件設計

本系統軟件的設計主要包括A/D轉換控制程序、USB設備固件程序(Firmware)、主機USB設備驅動程序、主機端應用程序和遠程客戶端應用程序幾個模塊。系統的軟件構成框圖如圖7所示。

圖7 系統軟件設計框圖

A/D轉換控制程序主要是控制A/D轉換芯片的工作時序,然后把轉換完成后的數字信號發送到FPGA內部。本設計的該程序部分是在可編程邏輯器件FPGA中實現的。

芯片CY7C68013的固件程序負責處理PC機發來的各種USB請求,以完成主機和外圍電路之間的數據傳輸,例如,完成對接口芯片的I/O端口和存儲單元的初始化;設置CPU時鐘頻率,配置相應端點的工作狀態;初始化工作模式和數據傳輸方式;響應各種主機發送來的請求等。

設備驅動程序的主要功能是使Win32應用程序能夠正確訪問本采集電路的硬件設備。本系統設計的設備驅動程序是以Microsoft的設備驅動開發包DDK(Device Driver Kit)為開發工具,以微軟驅動模型WDM(Windows Driver Model)的形式編寫的。應用程序通過API函數發出相應命令以后,設備驅動程序以I/O請求包IRP(I/O Request Packets)的形式封裝該命令,并把它傳遞給底層的總線驅動程序USBD(Universal Serial Bus Driver),從而達到與硬件設備進行通信的目的,最后總線驅動程序給上層驅動程序返回一個狀態信號來告知本次通信是否成功完成。

主機端應用程序的主要功能是接收硬件設備發送的數據,并且把采集到的數據進行顯示和存儲。

結論

本文主要完成了一種高速數據采集系統的設計,該數據采集系統利用高性能FPGA、高速A/D轉換器、高速USB 2.0接口芯片,是一種具有高速USB接口的外置式數據采集卡,信號的處理都是在PC機上完成的,這樣不僅縮小了電路體積,提高了系統的穩定性,而且節約了系統成本。

有你想看的精彩 至芯科技FPGA就業培訓班——助你步入成功之路、9月23號北京中心開課、歡迎咨詢! 利用FPGA設計基于LVDS的圖像數據采集傳輸系統 流水線ADC的內部結構和工作原理是什么

掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:基于FPGA的高速數據采集系統該怎么設計?

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603010

原文標題:基于FPGA的高速數據采集系統該怎么設計?

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

利用ADS869X做一個隔離的高速數據采集系統,ADC需要一個時鐘信號,可以自己外接一個晶振電路嗎?

高速分切機數據采集監控告警系統解決方案

ADS869x 18位、高速、單電源、SAR ADC數據采集系統數據表

ADS867x 14位、高速、單電源、SAR ADC數據采集系統數據表

典型的數據采集系統設計及其核心元件

基于FPGA的高速數據采集系統該怎么設計?

基于FPGA的高速數據采集系統該怎么設計?

評論