隨著集成電路技術的不斷發展,芯片中的晶體管數量呈現出爆炸性增長。為了提高性能,降低功耗,SoC設計中采用了各種優化技術。其中,Clock Gating(時鐘門控)技術已成為低功耗設計領域的重要研究方向。本文將探討 Clock Gating 技術在 SoC 設計中的重要性。

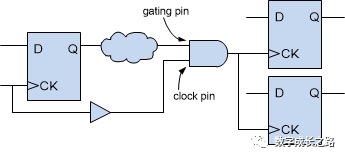

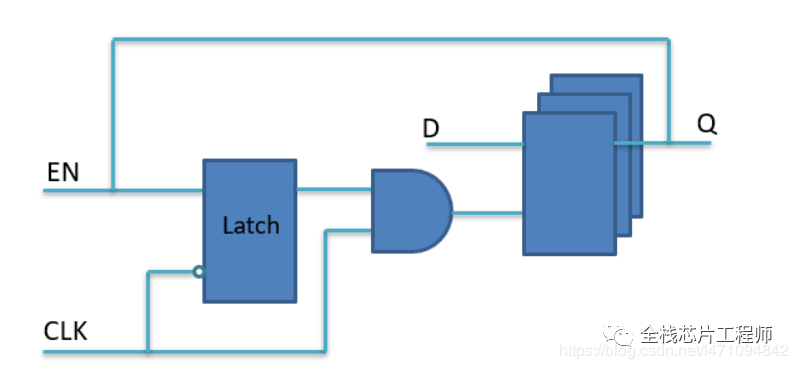

一、什么是 Clock Gating 技術?

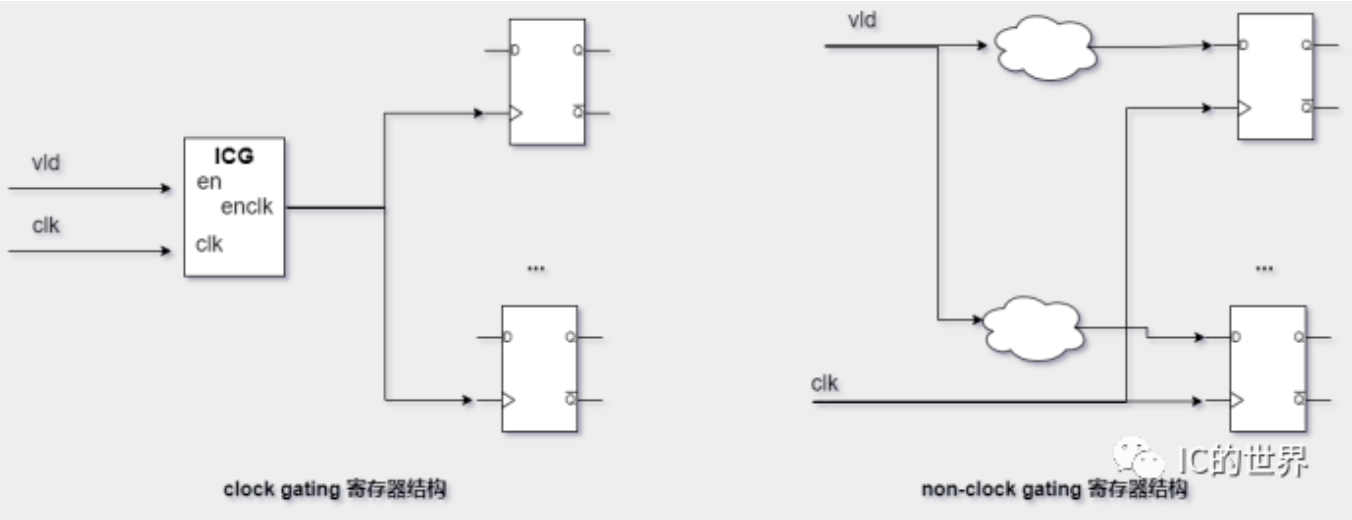

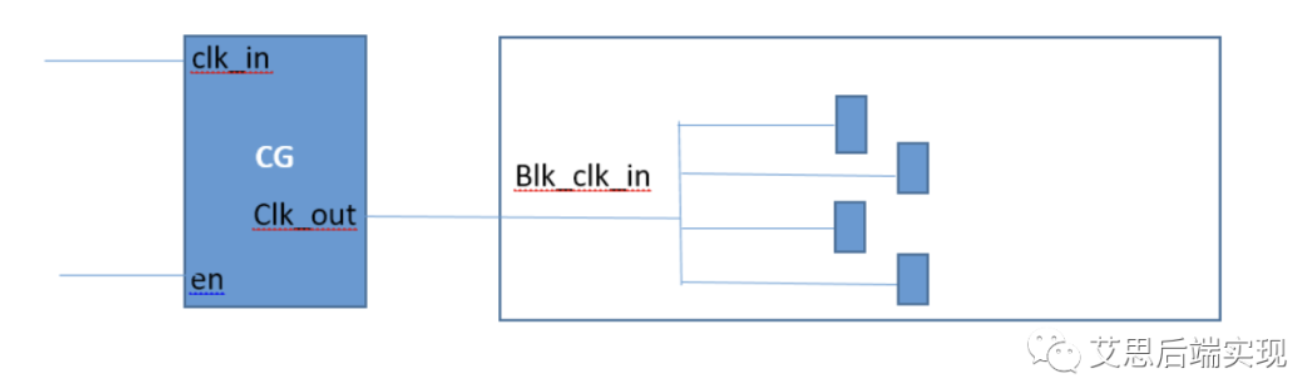

Clock Gating 是一種動態調整時鐘頻率的技術,通過關閉不需要的時鐘,從而降低功耗。在 SoC 設計中,很多模塊在不同時間段內并不都需要工作。通過 Clock Gating 技術,可以為這些模塊提供動態時鐘控制,實現功耗的有效降低。

二、Clock Gating 在 SoC 設計中的應用

處理器核心

處理器核心是 SoC 中的重要組成部分,負責執行程序指令。在處理器核心中,有很多功能單元(如:ALU、寄存器、緩存等)在不同指令周期內并不都需要工作。通過 Clock Gating 技術,可以實現對這些功能單元的動態時鐘控制,降低功耗。

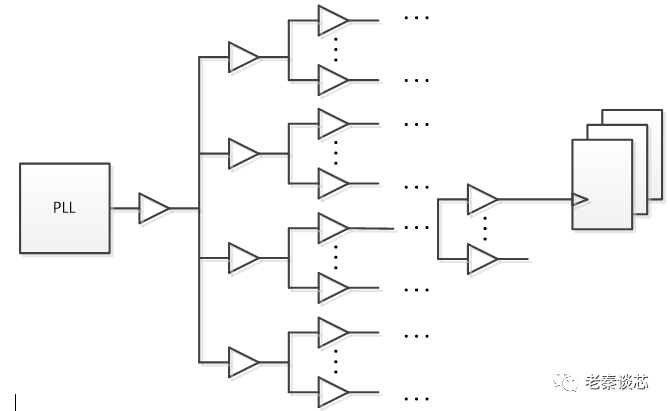

片上網絡(NoC)

隨著 SoC 中模塊數量的增加,片上網絡(Network-on-Chip,NoC)已經成為了 SoC 設計的重要組成部分。NoC 負責在各個模塊之間傳輸數據,但在某些時間段內,部分通信鏈路并不需要工作。通過 Clock Gating 技術,可以為這些通信鏈路提供動態時鐘控制,降低功耗。

存儲器控制器

存儲器控制器負責管理 SoC 中的各種存儲器。與處理器核心和 NoC 類似,存儲器控制器中的部分功能單元在不同時間段內并不需要工作。通過 Clock Gating 技術,可以實現對這些功能單元的動態時鐘控制,降低功耗。

I/O接口

I/O接口是SoC與外部設備進行數據交互的通道。在很多情況下,I/O接口的部分信號線并不需要一直處于激活狀態。通過Clock Gating 技術,可以為這些信號線提供動態時鐘控制,降低功耗。

三、Clock Gating 在 SoC 設計中的優勢

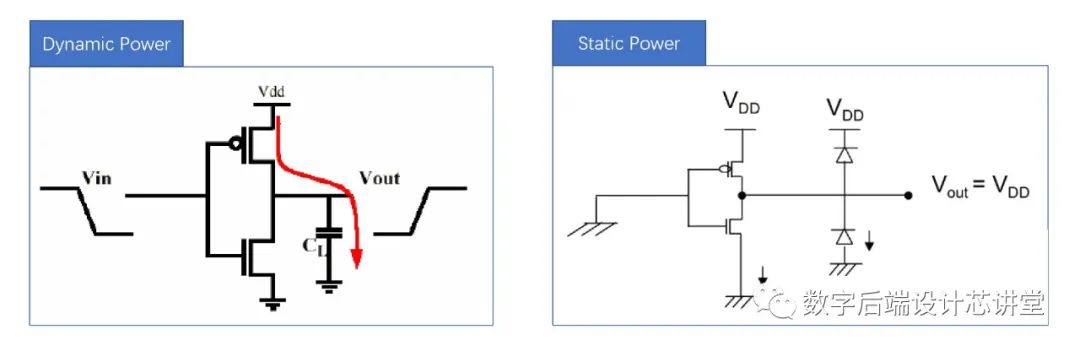

降低功耗

通過 Clock Gating 技術,可以為不需要工作的模塊提供動態時鐘控制,降低功耗。在 SoC 設計中,很多模塊在不同時間段內并不都需要工作。通過 Clock Gating 技術,可以實現對這些模塊的動態時鐘控制,有效降低功耗。

節省面積

采用 Clock Gating 技術可以降低模塊的功耗,從而降低對散熱和電源的要求,進一步縮小模塊面積。在 SoC 設計中,面積是一個寶貴的資源。通過 Clock Gating 技術,可以為其他功能模塊節省空間,提高集成度。

提高性能

通過 Clock Gating 技術,可以降低功耗,延長電池壽命。此外,動態時鐘控制還可以減少電磁干擾,提高系統性能。

Clock Gating 技術在 SoC 設計中具有重要意義。通過實現動態時鐘控制,Clock Gating 技術可以為不需要工作的模塊降低功耗,節省面積,提高性能。隨著集成電路技術的不斷發展,Clock Gating 技術將在 SoC 設計中發揮越來越重要的作用。

審核編輯:劉清

-

處理器

+關注

關注

68文章

19299瀏覽量

230009 -

控制器

+關注

關注

112文章

16381瀏覽量

178292 -

寄存器

+關注

關注

31文章

5346瀏覽量

120485 -

SoC設計

+關注

關注

1文章

148瀏覽量

18774 -

晶體管

+關注

關注

77文章

9698瀏覽量

138296

原文標題:Clock Gating 在 SoC 設計中的重要性

文章出處:【微信號:快樂的芯片工程師,微信公眾號:快樂的芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RTL實例化的clock gating cell淺見

FPGA的時鐘門控是好還是壞?

同步電路設計中CLOCK SKEW的分析說明

通常有兩種不同的時鐘門控實現技術

ASIC的clock gating在FPGA里面實現是什么結果呢?

什么是Clock Gating技術?Clock Gating在SoC設計中的重要性

什么是Clock Gating技術?Clock Gating在SoC設計中的重要性

評論