PMP 和 Paging

物理內存保護機制旨在與 RISC?V 指令集手冊,第二卷:特權架構,版本 1.10 中描述的基于頁面的虛擬內存系統(tǒng)組合。啟用分頁后,訪問虛擬內存的指令可能會導致多次物理內存訪問,包括對頁表的隱式引用。PMP 檢查適用于所有這些訪問。隱式頁表訪問的有效特權模式是管理員模式。

允許使用虛擬內存的實現(xiàn)以推測方式執(zhí)行地址轉換,并且比顯式虛擬內存訪問所需的時間更早。可以在地址轉換和顯式虛擬內存訪問之間的任何時候檢查結果物理地址的 PMP 設置。到不可執(zhí)行地址范圍的錯誤預測分支不會生成陷阱。因此,當以影響保存頁表的物理內存或頁表指向的物理內存的方式修改 PMP 設置時,M 模式軟件必須將 PMP 設置與虛擬內存系統(tǒng)同步。這是通過在寫入 PMP CSR 后執(zhí)行 rs1=x0 和 rs2=x0 的 SFENCE.VMA 指令來實現(xiàn)的。

如果未實現(xiàn)基于頁面的虛擬內存,或者當它被禁用時,內存訪問會同步檢查 PMP 設置,因此不需要 fence。

PMP 限制

在包含多個 hart 的系統(tǒng)中,每個 hart 都有自己的 PMP 設備。hart 上的 PMP 權限不能應用于多 hart 系統(tǒng)中其他 hart 的訪問。此外, SiFive 設計可能包含一個前端端口,以允許外部總線主控器訪問系統(tǒng)的完整內存映射。PMP 無法阻止前端端口上的外部總線主控器的訪問。

沒有 PMP 保護的區(qū)域的行為

如果內存映射的非保留區(qū)域沒有應用 PMP 權限,則默認情況下,管理員或用戶模式訪問將失敗,而機器模式訪問將被允許。

訪問設備內存映射中的保留區(qū)域(例如中斷控制器)讀取時將返回 0x0,寫入將被忽略。在沒有 PMP 保護的情況下訪問設備內存映射之外的保留區(qū)域將導致總線錯誤。總線錯誤可以使用總線錯誤單元 (BEU) 對 hart 產(chǎn)生中斷。

PMP 保護區(qū)的緩存刷新行為

當一條線被帶入高速緩存并且 PMP 設置為斷言鎖定 (L) 位以保護該線的一部分時,數(shù)據(jù)高速緩存刷新指令將生成存儲訪問錯誤異常,如果沖洗包括受保護的線路的任何部分。緩存刷新指令執(zhí)行無效和回寫,因此它實際上是在嘗試寫回受保護的內存位置。

如果緩存刷新發(fā)生在未受保護的部分行上,刷新將成功并且不會產(chǎn)生異常。如果需要在沒有回寫的情況下刷新數(shù)據(jù)高速緩存,請改用高速緩存丟棄指令,因為這會使該行無效但不會回寫。

-

內核

+關注

關注

3文章

1391瀏覽量

40602 -

內存

+關注

關注

8文章

3081瀏覽量

74595 -

設備

+關注

關注

2文章

4584瀏覽量

71060 -

PMP

+關注

關注

0文章

45瀏覽量

18240 -

RISC

+關注

關注

6文章

468瀏覽量

84119 -

sifive

+關注

關注

0文章

36瀏覽量

9492

發(fā)布評論請先 登錄

相關推薦

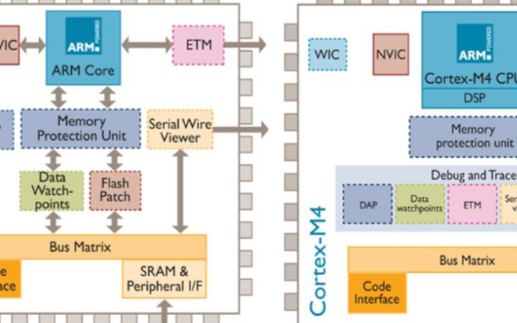

管理STM32 MCU中的內存保護單元

STM32H750在使能內存保護后啟用cache導致SPI+DMA傳輸不準確怎么解決?

STM32H750使能內存保護后DMA異常的原因?怎么解決?

玄鐵VirtualZone:基于RISC-V架構的安全擴展

Armv8-M內存模型與內存保護用戶指南

如何管理STM32產(chǎn)品中的內存保護單元(MPU)

為什么要使用MPU?MPU如何實現(xiàn)內存保護?

應用筆記|管理STM32 MCU中的內存保護單元

為什么要使用MPU?MPU如何實現(xiàn)內存保護?

如何管理STM32產(chǎn)品中的內存保護單元(MPU)

PMP物理內存保護介紹

PMP物理內存保護介紹

評論