加法器(Adder) 是非常重要的,它不僅是其它復(fù)雜算術(shù)運(yùn)算的基礎(chǔ),也是** CPU 中 ALU **的核心部件(全加器)。

在數(shù)字計(jì)算機(jī)中,兩個(gè)二進(jìn)制數(shù)之間的算術(shù)邏輯運(yùn)算(加、減、乘、除),基本上都是化成若干步加法操作進(jìn)行的。因此,學(xué)好數(shù)字電路,數(shù)字 IC 設(shè)計(jì)的入門,從學(xué)好加法器開始。

加法器分為 半加器 (Half Adder)**** 和 全加器 (Full Adder)**** 。全加器和半加器相比,只是 多了一個(gè)來(lái)自低位的單比特信號(hào)相加的進(jìn)位輸入 ,

全加器就是 3 位相加,半加器就是 2 位相加。例如,我們?cè)谧黾臃ㄟ\(yùn)算的時(shí)候,總是需要進(jìn)行低位進(jìn)位的判斷,接著進(jìn)行下一位的計(jì)算,這就是全加器的由來(lái)。

此外,下文的 RTL 代碼中的 **{} 符號(hào)表示的是 ** “拼接位” ,即先計(jì)算 a 與 b 的值,當(dāng) a 與 b 分別為 “0” 和 “1” 時(shí),它們之和為 1,那么就是{01},對(duì)應(yīng) cout 和 sum ;當(dāng) a 與 b 為 “1” 和 “1” 時(shí),它們之和為 2,那么就是轉(zhuǎn)換為二進(jìn)制就是{10},同樣對(duì)應(yīng) cout 和 sum 等等。

說(shuō)太多,都不如底層硬件代碼和設(shè)計(jì)電路看一看、學(xué)一學(xué)!!!

可基于多種方式描述的半加器的 Verilog 代碼和 RTL 電路

module Half_Adder(

input wire a, // 加數(shù)

input wire b, // 加數(shù)

output reg sum, // 和

output reg cout // 進(jìn)位輸出

);

// 行為描述

always @(a or b) begin

sum = a ^ b; // 實(shí)踐證明,這里 <= 和 = 的結(jié)果都一樣;都是純粹的組合邏輯;

cout = a & b;

end

// 數(shù)據(jù)流描述

// assign sum = a ^ b;

// assign cout = a & b;

// 門級(jí)描述

// and(cout,a,b);

// xor(sum,a,b);

endmodule

可基于多種方式描述的全加器的 Verilog 代碼和 RTL 電路

module Full_Adder(

input wire a, // 加數(shù)

input wire b, // 加數(shù)

input wire cin,// 進(jìn)位輸入

output reg sum, // 和

output reg cout // 進(jìn)位輸出

);

// 行為描述

always @(a or b or cin) begin

{cout,sum} <= a + b + cin;

end

// 行為描述

// always @(a or b or cin) begin

// sum = a ^ b ^ cin; // 實(shí)踐證明,這里 <= 和 = 的結(jié)果都一樣;都是純粹的組合邏輯;

// cout = a & b | b & cin | a & cin;

// end

// 數(shù)據(jù)流描述

// assign {cout,sum} = a + b + cin;

endmodule

-

IC設(shè)計(jì)

+關(guān)注

關(guān)注

38文章

1295瀏覽量

103918 -

加法器

+關(guān)注

關(guān)注

6文章

183瀏覽量

30114 -

半加器

+關(guān)注

關(guān)注

1文章

29瀏覽量

8790 -

全加器電路

+關(guān)注

關(guān)注

0文章

3瀏覽量

1624

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

加法器,加法器是什么意思

十進(jìn)制加法器,十進(jìn)制加法器工作原理是什么?

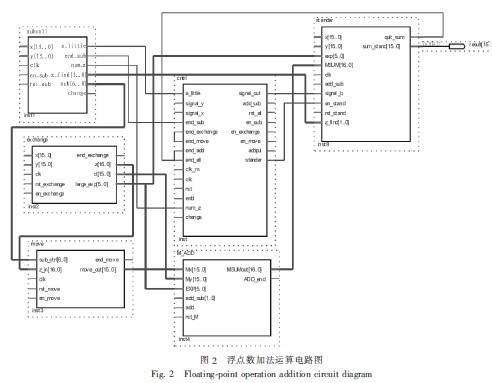

FPU加法器的設(shè)計(jì)與實(shí)現(xiàn)

8位加法器和減法器設(shè)計(jì)實(shí)習(xí)報(bào)告

同相加法器電路原理與同相加法器計(jì)算

加法器原理

加法器工作原理_加法器邏輯電路圖

加法器的原理及采用加法器的原因

同相加法器和反相加法器的區(qū)別是什么

加法器的原理是什么 加法器有什么作用

初級(jí)數(shù)字IC設(shè)計(jì)-加法器

初級(jí)數(shù)字IC設(shè)計(jì)-加法器

評(píng)論