在數字 IC 設計中,總是需要對一些數據進行 大小的比較 ,例如比較兩個或者三個以上的數據的大小,接著進行排序,最終輸出等等。于是, 比較器 (Comparator)的數字邏輯電路就應運而生。

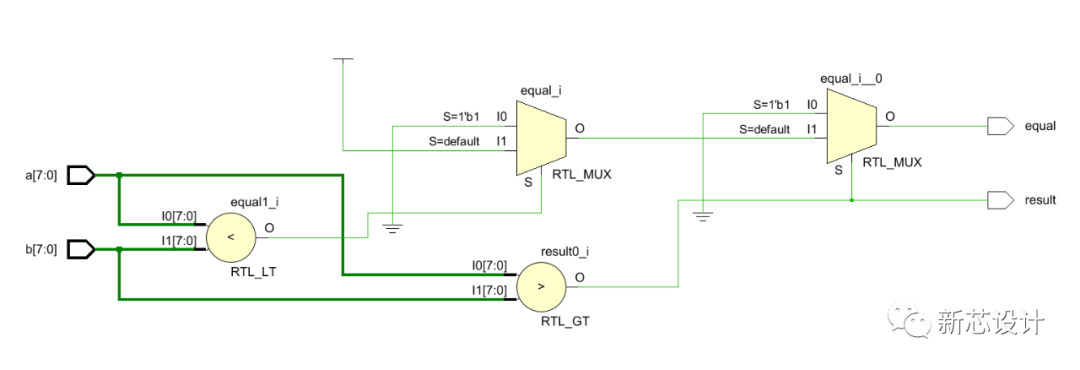

基于 8 位的數值比較器的 Verilog 代碼和 RTL 電路

module Comparator(

input wire [7:0] a , // 比較數

input wire [7:0] b , // 比較數

output reg result, // 比較結果

output reg equal // 比較結果

);

// 行為描述

always @(a or b) begin

if(a > b)

{equal,result} <= 2'b01; // a 比 b 大

else begin

if(a < b)

{equal,result} <= 2'b00; // a 比 b 小

else

{equal,result} <= 2'b10; // 相等

end

end

// 數據流描述

// assign equal = (a == b) ? 1 : 0;

// assign result = (a > b) ? 1 : 0;

endmodule

代碼詳解

對兩個**** 8 比特二進制輸入信號的大小進行判斷:如果 a 比較大,則 out 輸出高電平;如果 b 比較大,則 out 輸出低電平;如果 a 和 b 大小相等,那么,則 equal 輸出高電平,否則 equal 輸出低電平。

對于比較器的應用呢,其實,比較器在現實生活中也可以作為過濾器來使用。比如我們在統計成績的時候,要把不及格的學生過濾掉,那么我們就可以利用比較器,過濾掉成績不及格的學生。當輸入的成績小于 60 分的時候就不輸出顯示出來,那么最后統計出來的都是成績合格的學生。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

IC設計

+關注

關注

38文章

1295瀏覽量

103918 -

比較器

+關注

關注

14文章

1650瀏覽量

107185 -

二進制

+關注

關注

2文章

795瀏覽量

41643 -

過濾器

+關注

關注

1文章

428瀏覽量

19593 -

數字邏輯電路

+關注

關注

0文章

106瀏覽量

15812

發布評論請先 登錄

相關推薦

【下載】《數字邏輯電路的ASIC設計》

`內容簡介本書是“實用電子電路設計叢書”之一。本書以實現高速高可靠性的數字系統設計為目標,以完全同步式電路為基礎,從技術實現的角度介紹ASIC邏輯電路設計技術。內容包括:

發表于 04-03 17:14

VHDL硬件描述語言與數字邏輯電路設計

VHDL硬件描述語言與數字邏輯電路設計:本書系統地介紹了一種硬件描述語言,即VHDL語言設計數字邏輯電路和數字系統的新方法。這是電子

發表于 02-06 16:55

?363次下載

組合邏輯電路和時序邏輯電路比較_組合邏輯電路和時序邏輯電路有什么區別

組合邏輯電路和時序邏輯電路都是數字電路,組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入,與

發表于 01-30 17:26

?9.4w次閱讀

時序邏輯電路設計之同步計數器

時序電路的考察主要涉及分析與設計兩個部分,上文介紹了時序邏輯電路的一些分析方法,重點介紹了同步時序電路分析的步驟與注意事項。 本文就時序邏輯電路設計的相關問題進行討論,重點介紹時序

比較器的數字邏輯電路設計

比較器的數字邏輯電路設計

評論