思考:

1、L1、L2、L3 cache的替換策略是怎樣的?

2、什么類型的內(nèi)存永遠不會進L3 cache?

3、L3 cache一般都是多大?

4、L3 cache的組織形式一般是怎樣的?

5、什么是cache partitioning?

6、DSU、DSU-110、DSU-120有什么區(qū)別?

7、什么MPAM?有什么作用?

8、什么是Cache stashing?

9、什么是Cache slices?有什么好處?

在共享DSU-110 DynamIQ cluster中,所有core共享L3緩存。

注意:以下功能在此版本中不受支持,計劃在后續(xù)版本中支持:

DSU-110的共享L3緩存提供以下功能:

- (1)動態(tài)優(yōu)化的緩存分配策略,通常是互斥的。這種緩存分配策略意味著在正常使用中,一行數(shù)據(jù)要么位于一個或多個核心(或complexes)的緩存中,要么位于L3緩存中,但不會同時存在于兩個緩存中。只有可緩存的、可共享的內(nèi)存位置才會被分配到L3緩存中。不可共享的內(nèi)存位置不會被分配到L3緩存中。

- (2)可以通過內(nèi)存系統(tǒng)資源分區(qū)和監(jiān)視(MPAM)體系結構擴展將緩存路組分區(qū)并分配給進程。緩存分區(qū)確保每個進程不會主導緩存的使用,以不利于其他進程。

- (3)支持來自ACP和CHI接口的存儲請求。這些存儲請求也可以針對集群中核心或complexes的任何L2緩存。

- (4)對緩存數(shù)據(jù)和標簽RAM提供糾錯碼(ECC)保護。

- (5)緩存可以實現(xiàn)最多八個緩存切片( cache slices),取決于指定的L3緩存大小。緩存切片可以增加L3緩存的帶寬并改善物理布局。每個緩存切片包括數(shù)據(jù)、標簽、犧牲和嗅探過濾器RAM以及相關的邏輯(data, tag, victim, and snoop filter RAMs and associated logic)。

在關機時,DSU-110會自動執(zhí)行cache cleaning操作,無需進行由軟件控制的緩存清理。

1 L3 cache allocation policy

DSU-110 L3緩存只允許存儲可緩存的、可共享的內(nèi)存位置。Non-shareable的內(nèi)存不能被分配到L3緩存中。DSU-110 L3緩存采用動態(tài)優(yōu)化的緩存分配策略,通常是互斥的。這種緩存分配策略意味著在正常使用中,一行數(shù)據(jù)要么位于一個或多個核心(或complexes)的緩存中,要么位于L3緩存中,但不會同時存在于兩個緩存中。

當數(shù)據(jù)只分配給一個核心或complexes時,使用獨占分配。有時,當數(shù)據(jù)在多個核心或complexes之間共享時,會使用Inclusive分配。

- 來自core0的初始請求將數(shù)據(jù)分配到L1或L2緩存,但不分配到L3緩存。

- 當從core0驅(qū)逐數(shù)據(jù)時,被驅(qū)逐的數(shù)據(jù)會分配到L3緩存。這個緩存行的分配策略仍然是獨占的。

- 如果core0重新獲取該行,它將分配到核心0的L1或L2緩存中,并從L3緩存中刪除。這個緩存行的分配策略仍然是獨占的。

- 如果core1訪問該行以進行讀取,那么它仍然分配給核心0。它還會分配到核心1和L3緩存中。在這種情況下,該行采用Inclusive分配,因為它在多個核心之間共享。

2 可用的緩存路組數(shù)量

每個緩存切片中可用的緩存路組數(shù)量取決于您選擇實現(xiàn)的L3緩存大小。當選擇2的冪次方L3緩存大小,如256KB、512KB、1024KB、2MB、4MB、8MB或16MB時,每個緩存切片具有16個緩存路組。當選擇非2的冪次方L3緩存大小,如1536KB、3MB、6MB或12MB時,每個緩存切片僅具有12個緩存路組。

3 L3緩存分區(qū)(partitioning)

L3緩存支持一種分區(qū)方案,可以改變替換(victim)選擇策略,以防止進程占用整個L3緩存,對其他進程造成不利影響。緩存分區(qū)適用于特殊的軟件,其中有不同緩存訪問模式的不同類別進程在運行。例如,兩個進程A和B在同一個cluster的不同核心上運行,因此共享L3緩存。如果進程A比進程B更具數(shù)據(jù)密集性,那么進程A可能導致進程B分配的所有緩存行都被驅(qū)逐。驅(qū)逐這些已分配的緩存行可能降低進程B的性能。DynamIQ Shared Unit-110(DSU-110)使用Memory System Resource Partitioning and Monitoring(MPAM)體系結構擴展來分區(qū)L3緩存。MPAM是一種旨在將內(nèi)存系統(tǒng)性能劃分給軟件的體系結構擴展。因此,MPAM提供了廣泛的可選功能,如緩存分區(qū)、帶寬分區(qū)和進程監(jiān)視。DSU-110僅使用MPAM來分區(qū)L3緩存。MPAM要求系統(tǒng)傳遞MPAM ID,各core綁定到每個內(nèi)存系統(tǒng)事務(transaction)。雖然MPAM ID的結構是架構性的,但其組件的配置是實現(xiàn)定義的。DSU-110使用以下MPAM ID結構:

? MPAMNS字段,1 BIT,指示此事務是否安全或非安全。

? PARTID,6 BIT,是當前事務的軟件分配的分區(qū)標識符。這支持在非安全空間中最多64個PARTID,在安全空間中最多8個PARTID。雖然單個進程最多可以使用2個PARTID,一個用于指令獲取,一個用于數(shù)據(jù)訪問,但也可以由多個進程共享單個PARTID。MPAMNS位指示此事務是否需要安全或非安全PARTID。如果此事務需要安全PARTID,則僅使用PARTID的低3位。

? PMG,1 BIT,標識性能監(jiān)視組(Performance Monitoring Group),用于MPAM提供分區(qū)的細粒度監(jiān)視,DSU-110不使用此功能。

當啟用L3MPAMSTORAGE參數(shù)時,L3緩存存儲此MPAM ID信息,可以在驅(qū)逐時檢索。注意:通常,只有在存在下游緩存(downstream cach),如系統(tǒng)緩存,也支持MPAM時才需要此設置。

如果未存儲MPAM ID,則任何L3驅(qū)逐都將使用引起驅(qū)逐的事務的MPAM ID。注意:如果將事務映射到未設置MPAMCFG_CPBM設置的分區(qū),則不會將此事務分配到L3緩存中。

L3緩存的分區(qū)是通過緩存路組的方式進行的,對于DSU-110,每個組包含兩個路組,因此最多支持8個分區(qū)。

- 不是2的冪次方的緩存大小(1.5MB、3MB、6MB和12MB)支持的緩存路組較少,因為它們具有較少的可用路組。

- 如果某些緩存路組被關閉(更多細節(jié)請參見第58頁的5.4.1節(jié)L3緩存RAM關機),則每個L3緩存分區(qū)中的路組數(shù)量會減少。這種緩存路組的減少可能會降低性能,當進程沒有足夠的路組可用時。因此,Arm建議在使用緩存分區(qū)時謹慎關閉緩存路組。

MPAM作為一種架構擴展的優(yōu)點之一是它定義了一種通用機制,用于分割L3緩存,因此可以很容易地通過標準軟件進行交互和配置。緩存分區(qū)允許您將L3緩存分割為最多8個獨立的分區(qū)。然而,您可以自由地定義所需的分區(qū)數(shù)量,也可以重疊分區(qū)。例如,您可以將路組0到4分配給分區(qū)0,然后將路組0到8分配給分區(qū)1。這意味著分配給分區(qū)1的進程可以使用所有路組,而分配給分區(qū)0的進程只能使用一半的路組。

4 緩存存儲

緩存存儲允許外部代理請求將一行數(shù)據(jù)帶入(或存儲)到簇中的緩存中。DynamIQ? Shared Unit-110(DSU-110)不能執(zhí)行cache stashing部分,響應如下:

- DSU-110永遠不會發(fā)送SnpResp * _ Read響應。

- 對于SnpMakeInvalidStash,DSU-110將以SnpResp_I響應。

- 對于SnpStashUnique和SnpStashShared,DSU-110將以SnpRespI、SnpRespSC或SnpResp_UC之一響應。

- 對于SnpUniqueStash,DSU-110將在需要的情況下返回數(shù)據(jù)。因此,它將返回SnpRespDataI或SnpRespI。DSU-110不執(zhí)行加速器一致性端口(ACP)事務的緩存存儲部分。這些事務被視為等效的非緩存存儲事務。

5 L3緩存數(shù)據(jù)RAM延遲

DSU-110 L3數(shù)據(jù)RAM接口可以實現(xiàn)在輸入和輸出路徑上具有可配置的延遲。以下選項可供選擇:

- 輸入路徑到L3數(shù)據(jù)RAM的寫入延遲可以是1個周期(默認)或2個周期。

- 從L3數(shù)據(jù)RAM的輸出路徑到達的讀取延遲可以是2個周期(默認)或3個周期。

- 當配置了輸出路徑上的3個周期讀取延遲時,輸入路徑上可以選擇2p的寫入延遲選項。這個2p的寫入延遲還可以使RAM輸入信號在額外的周期內(nèi)保持穩(wěn)定,允許在RAM輸入上進行額外的保持時間。

- L3數(shù)據(jù)RAM的輸出端口上可以選擇一個可選的寄存器切片。

在輸入路徑上,如果請求了2或2p的寫入延遲,則RAM時鐘使能會進行流水線處理,并且對所有其他RAM輸入信號應用多周期路徑。

在輸出路徑上,2個周期的讀取延遲和3個周期的讀取延遲會對所有RAM輸出信號應用多周期路徑。可選寄存器切片的輸出是單周期的,絕不能應用多周期路徑。

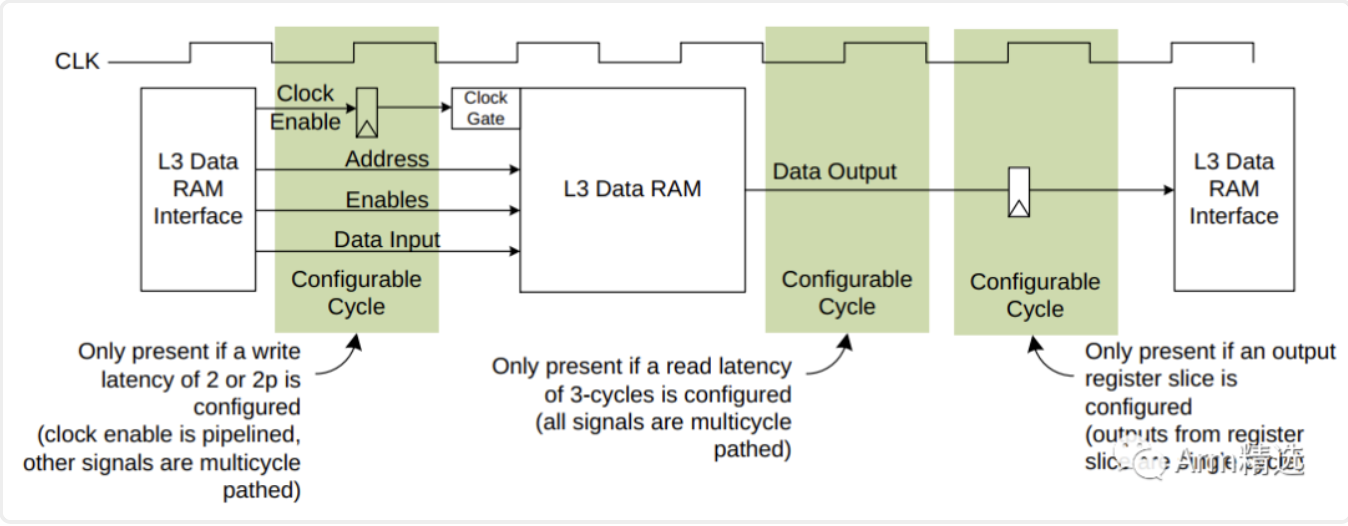

下圖顯示了L3數(shù)據(jù)RAM的時序圖。

RAM延遲的增加會增加L3命中延遲,從而降低性能。因此,只有在RAM無法滿足2個周期延遲的時序要求時才使用3個周期讀取延遲選項。但是,如果僅僅是從RAM到SCU邏輯的導線路由延遲無法滿足這個時序要求,那么應該使用寄存器切片。

延遲選項僅針對L3數(shù)據(jù)RAM進行了指定,因為L3標簽RAM和SCU嗅探過濾器RAM滿足1個周期的輸入和1個周期的輸出時序要求。

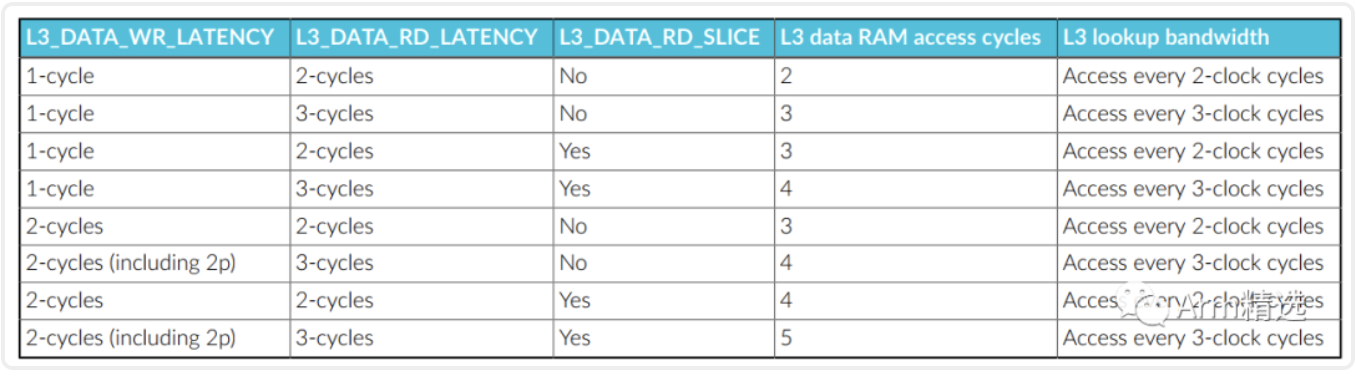

以下表格描述了不同延遲配置參數(shù)對L3數(shù)據(jù)RAM性能的影響:

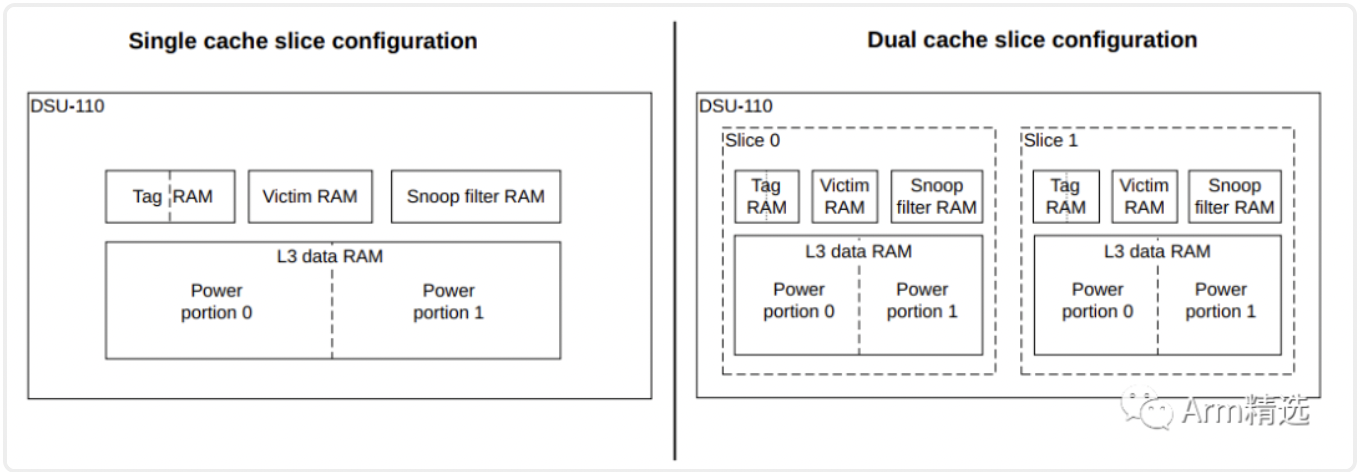

6 緩存切片和分區(qū)

DynamIQ? Shared Unit-110(DSU-110)的L3緩存可以分為最多八個相同的切片,每個切片包含256KB到2MB的緩存。一個緩存切片包括數(shù)據(jù)RAM、tag RAM、替換RAM和snoop RAM以及相關邏輯。一個分區(qū)是對緩存切片中的RAM的進一步細分。對于每個緩存切片,數(shù)據(jù)RAM和標簽RAM都被細分為兩個分區(qū)。

下圖顯示了單個和雙緩存切片配置之間的差異。

將L3緩存分割成切片提供了以下優(yōu)點:

- 在實現(xiàn)宏單元時改善物理布局,通過確保RAM位于控制它們的邏輯附近。

- 增加帶寬,因為可以并行訪問這些切片。

6.1 Cache slice and master port selection

對于具有多個緩存切片的實現(xiàn),請求會根據(jù)地址和內(nèi)存屬性發(fā)送到特定的切片。

地址到切片的映射不可配置,但地址到master port的映射是可配置的,并且可以獨立于切片映射。

-

加速器

+關注

關注

2文章

796瀏覽量

37840 -

RAM

+關注

關注

8文章

1368瀏覽量

114641 -

ARM芯片

+關注

關注

1文章

125瀏覽量

21466 -

緩存器

+關注

關注

0文章

63瀏覽量

11658 -

cache技術

+關注

關注

0文章

41瀏覽量

1062

發(fā)布評論請先 登錄

相關推薦

深入理解STM32

對棧的深入理解

ARM Cortex-A715核心技術參考手冊

ARM Cortex-X3核心技術參考手冊

ARM Cortex-A510核心技術參考手冊

ARM Dynamiq?共享單元-110型技術參考手冊

重磅!Arm正式推出Armv9架構

淺談ARM發(fā)布Armv9的三大改進

宋寶華:深入理解cache對寫好代碼至關重要

Arm微架構之Armv9時代

深入理解Cache工作原理

深入理解Armv9 DSU-110中的L3 cache

深入理解Armv9 DSU-110中的L3 cache

評論