SystemVerilog引入了interface,這里我們從可綜合的RTL代碼的角度聊聊interface。

什么是interface?

Interface是將一系列信號封裝為一個模塊,這里的“一系列信號”通常是彼此相關的,比如AXI接口協議之一的AXI4-Stream的TLAST/TVALID/TREADY/TDATA,這個“模塊”稱為接口模塊。接口模塊可以被實例化作為其他module的端口,從而簡化了module之間以及module與TB(testbench)之間的連線操作。

使用interface的好處

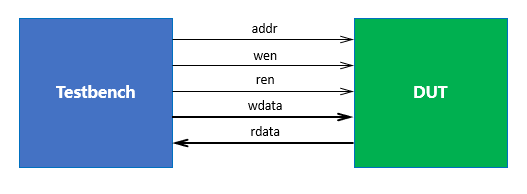

使用interface的好處也是顯而易見的。我們來看個例子。如下圖所示,待測模塊和測試平臺之間的連線包含5個信號,采用此方法就要在DUT module內定義5個端口,在TB內定義對應的5個信號。

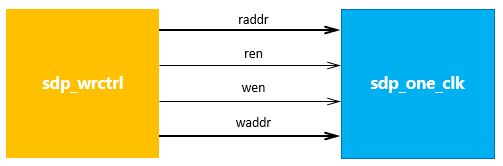

如果采用interface就會形成下圖所示的連接方式。這樣無論是DUT還是TB只需要在自身模塊內實例化這個interface即可。

可見,使用interface會帶來這樣幾個好處:

(1)module之間的連線由輸入/輸出列表替換為interface,不易出錯

(2)如果需要更新module的輸入/輸出端口,只用在interface里進行一次更新,而不必在相關module的端口處進行多次更新

其他好處跟UVM相關,這里先不做闡述。

接口的定義

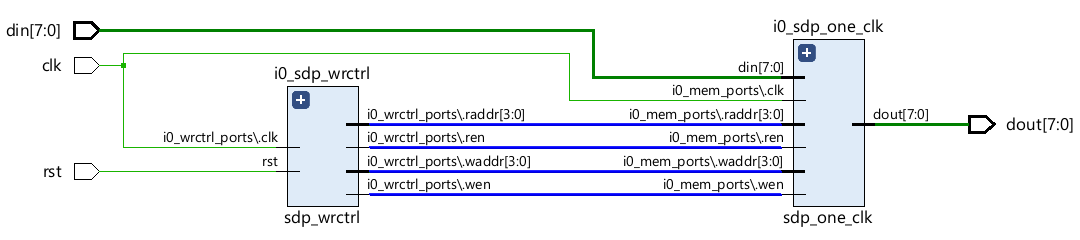

我們從可綜合RTL代碼的角度看個例子,如下圖所示的兩個模塊,一個是控制模塊,一個是存儲模塊,控制模塊生成相應的控制信號給存儲模塊。

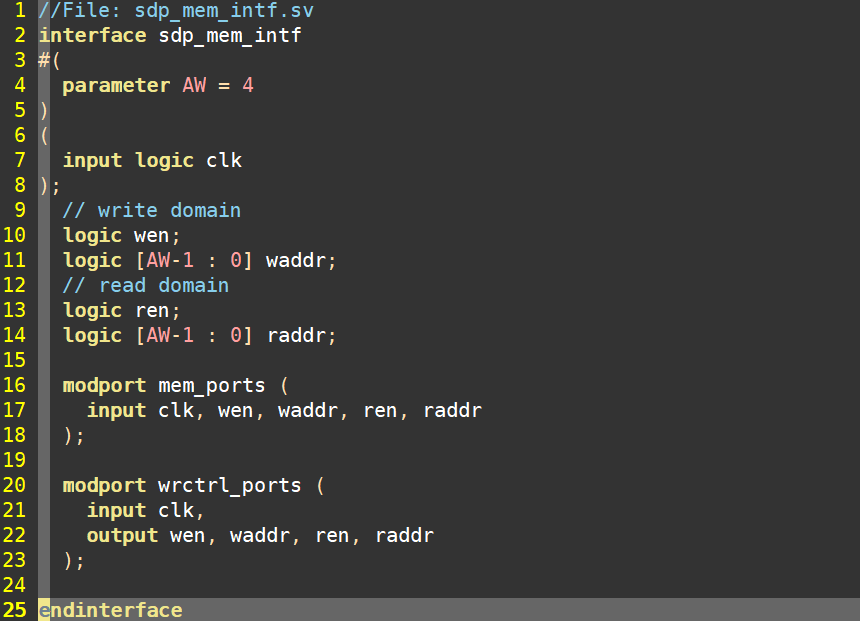

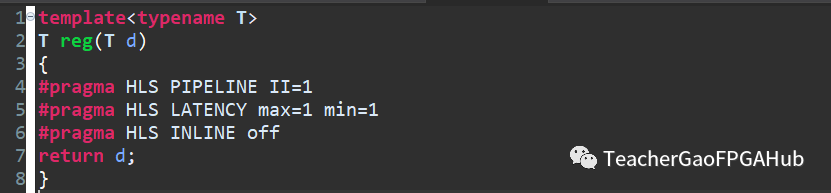

我們使用interface定義這組信號,如下圖所示代碼。從這段代碼可以看到,接口模塊以interface作為關鍵字開始,以endinterface結束(像不像module,endmodule)。Interface可以參數化,如代碼的4行所示,可以有輸入/輸出或雙向端口如代碼第7行所示。代碼第10行和第11行定義了寫方向的控制信號,第13行和14行定義了讀方向的控制信號。第16行modport(端口模塊)用來定義信號方向。對存儲模塊而言,這些信號都是輸入信號,對控制模塊而言,除時鐘外其他信號均為輸出信號。

因為只是定義信號的方向,所以只用列出信號名稱而無需指定信號的位寬。同時,同方向的信號可列在同一行,如代碼第17行所示。如果信號方向聲明的結尾也是modport的結尾,那么該結尾沒有任何額外標點符號,如代碼第22行的結尾,如果信號方向聲明的結尾不是modeport的結尾,那么結尾就用逗號,如代碼第21行。注意代碼第10行至第14行定義的信號類型為logic,相比于Verilog里的reg,logic更靈活,不僅可以用在always進程中,也能用于assign賦值語句中(Verilog需要用wire)。

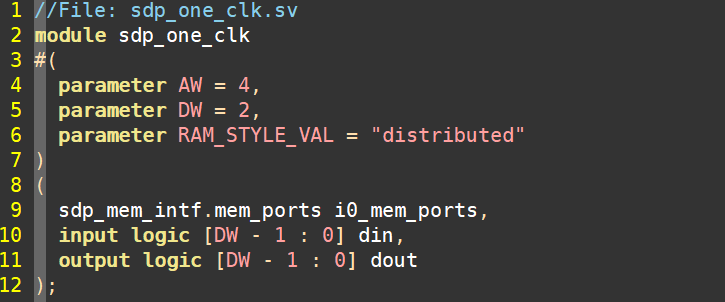

在存儲模塊中,可直接在端口列表內實例化該接口模塊,如下圖所示代碼片段第9行,實例化方式和模塊的實例化方式一樣,需要注意的是這里不能指定interface內的parameter,其余輸入/輸出端口不在接口模塊內的可單獨聲明,如代碼第10行和第11行所示。

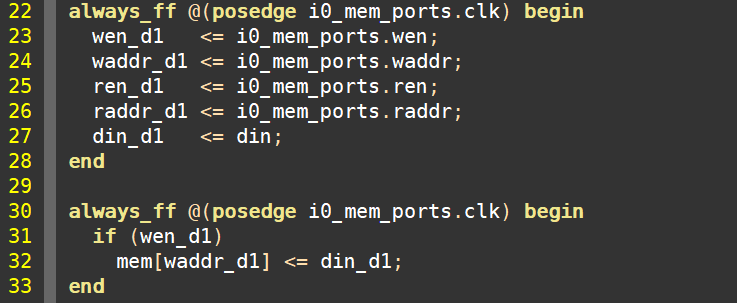

在模塊內部使用interface內聲明的接口,需要采用如下圖所示代碼片段的方式,如代碼第23行,通過i0_mem_ports.wen使用寫使能信號。因為代碼內部可能會反復使用interface內的信號,所以interface的名字盡量短一些。

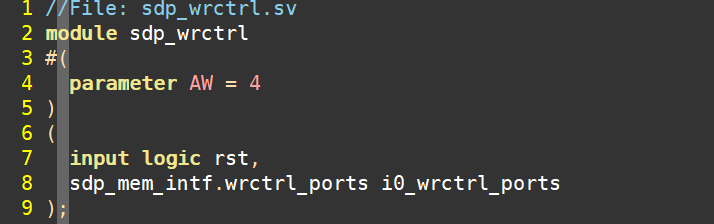

同樣地,在控制模塊內可直接實例化上述定義的interface,如下圖所示代碼片段。

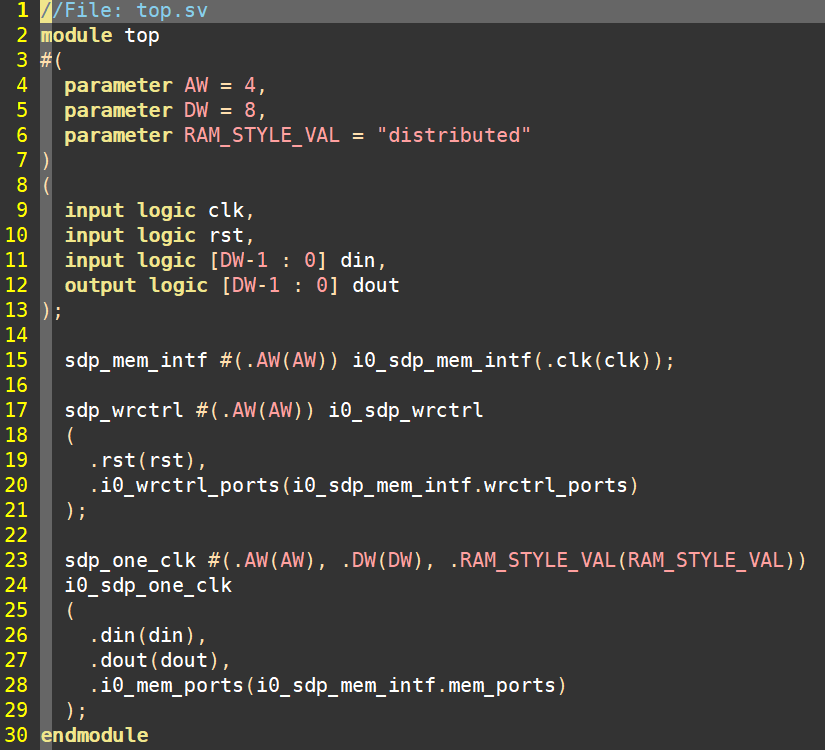

在設計的頂層,需要依次實例化接口、存儲模塊和控制模塊。此時,就需要對接口的parameter進行設定,如下圖所示代碼片段的第15行所示。

傳統的輸入/輸出列表方式存在這樣幾個不足之處:

(1)需要在相關模塊中反復聲明輸入/輸出信號

(2)存在不同模塊端口不匹配的風險

(3)設計規格的更改會導致需要在相關多個模塊中進行輸入/輸出信號的更新

這種重復性的更新不僅涉及到很多行代碼,還會存在信號名稱寫錯或者信號位寬寫錯的風險。

注意:module端口聲明若采用input/output/inout這種形式,實例化時這些端口是可以懸空的,但如果采用interface,實例化的interface是不允許處于未連接的狀態。

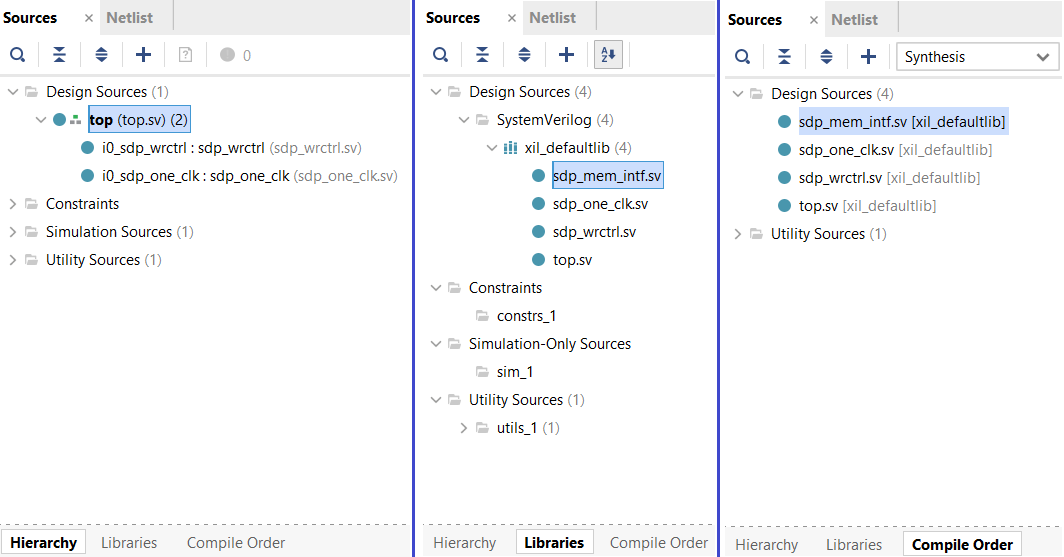

Vivado對interface是支持的。將上述4個文件直接添加到Vivado中,如下圖所示。在Hierarchy窗口中,可以看到top下面只有控制模塊和存儲模塊,而沒有接口模塊,因為接口并不是一個module。在Libraries下則可以看到接口模塊。在Compile Order窗口下,可以看到工具會先編譯接口模塊,再編譯其他模塊。

Vivado下打開Elaborated Design,可以看到interface信息,如下圖中的高亮部分,工具以“接口名.信號名”的方式顯示net的名字。

綜上所示,SystemVerilog提供的interface支持參數化,支持信號分組(modport),在可綜合的RTL代碼中,可使用interface簡化輸入/輸出列表的描述。

審核編輯:劉清

-

RTL

+關注

關注

1文章

388瀏覽量

60608 -

UVM

+關注

關注

0文章

182瀏覽量

19413 -

Interface

+關注

關注

0文章

103瀏覽量

38961 -

Module

+關注

關注

0文章

72瀏覽量

13157 -

DUT

+關注

關注

0文章

190瀏覽量

12816

原文標題:說說SystemVerilog的Interface

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

RTL級設計的基本要素和步驟是什么

評論